M.2 NVME/M.2 SATA SSD PCIE X4

2024-03-14 22:02:08

M.2 NVME 80MM SSD PCIE X4 ADAPT

2024-03-14 22:02:08

M.2 NVMe SSD PCIe 4.0 Adapt w/HS

2024-03-14 22:02:08

M.2 NVME 110MM SSD PCIE X4

2024-03-14 22:02:08

6 6 Pin PCIe to (2) SATA 15 Pin

2024-03-14 22:02:05

8-CH RELAY & 8-CH IDI PCIE CARD

2024-03-14 20:33:38

实时传递到上位机采集缓冲区。在超带宽视频采集情况下,支持采集丢帧操作,后续视频可以正常采集。视频采集与显示子系统使用高效的PCIe H2C DMA引擎读取上位机显示缓冲区的视频帧,存储到视频显示队列中

2024-03-13 13:59:45

Integrated Block,Multi-Channel PCIe RDMA Subsystem实现了使用DMA Ring缓冲的独立多通道、高性能/超低延时/超低抖动Continous Ring DMA

2024-03-07 13:54:29

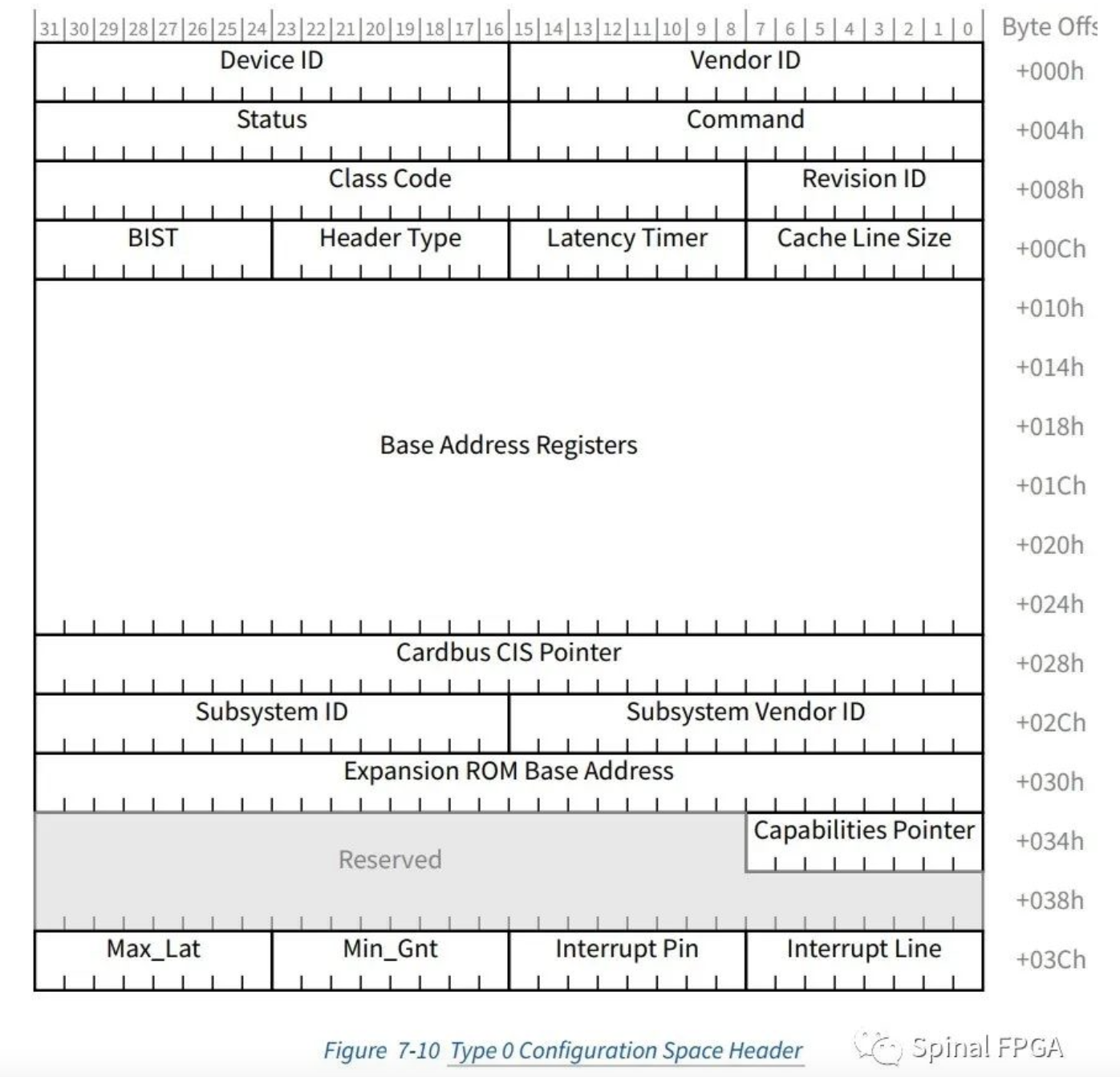

如图所示,PCIe IP作为endpoint与RC对接,用户实现了应用逻辑,与PCIe IP进行交互,交互信号中data格式为TLP报文格式,且交互信号包含相应的控制信号,例如PCIe配置空间和IP相干的配置信号。

2024-02-26 18:19:28 857

857 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous

2024-02-22 11:11:55 151

151

PCIe-AXI-Controller兼容PCI Express Base Specification Revision 3.1,实现PCIe PHY Layer,Data Link Layer以及

2024-02-21 15:15:03 144

144

什么是PCIe?PCIe有什么用途?什么是PCIe通道,x1、x4、x8和x16是什么意思?PCIe 5.0有何不同? PCI-Express(peripheral component

2024-01-30 16:09:25 503

503 /步进伺服驱动器;(2)联动轴数最高可达16轴,运动周期最小为100μs;(3)标配8进8出,其中4路高速锁存输入和8路高速PWM、PSO输出,更多IO请选配ACC37接线板扩展板;(4)支持PWM

2024-01-24 09:48:21

随着PCIE版本的不断升级,其应用范围也越来越广泛。除了传统的显卡、网卡、声卡等设备外,SSD、USB控制器、Thunderbolt接口等设备也开始支持PCIE接口。

2024-01-21 10:25:10 577

577 高性能20路PCIe时钟缓冲器新品推介SQ82100PCI-Express(PCIe)是一种高速串行计算机扩展总线标准,主要用于扩充计算机系统总线数据吞吐量以及提高设备通信速度。目前服务器

2023-12-20 08:19:38 240

240

)、AD9974的a、b两通道的寄存器空间是否相互独立?

2)、在双通道的配置过程中,是否应当有先后顺序?

3)、造成无法双通道同时使用的原因是什么?

2023-12-18 06:07:03

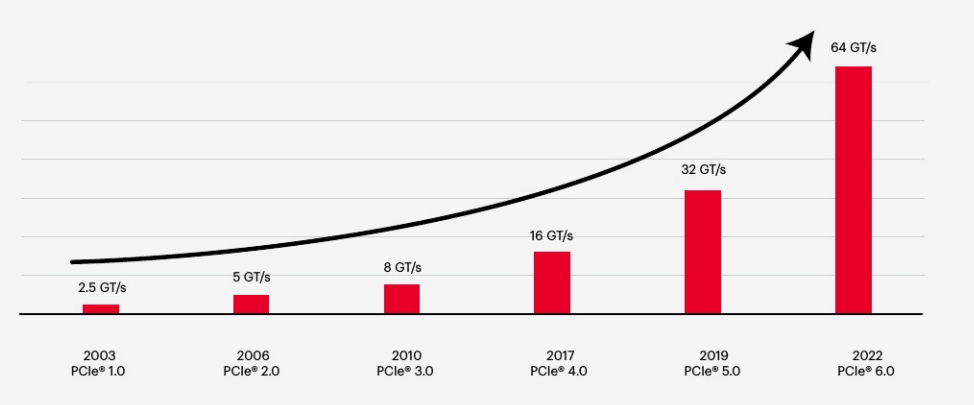

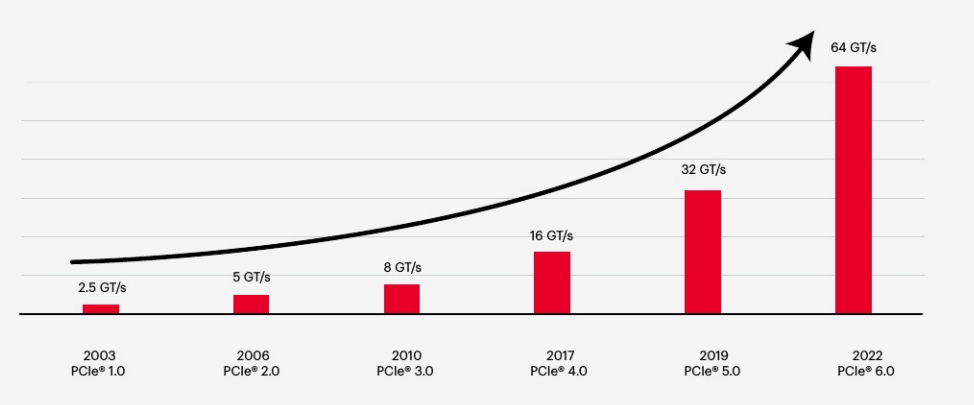

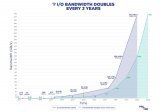

自2003年推出以来,PCIe发展至今已经从最初的1.0升级到了6.0,本文则为大家简单介绍一下PCIe标准的演进历史以及各代PCIe标准之间的主要差异。

2023-12-14 16:38:08 1525

1525

=94%]

[tr][td]

三、应用软件

2路AD采集PCIe传输(453 + 536)

软件实现FPGA逻辑 AD采集,PCIe XDMA传输,寄存器配置

采集显示上位机一体,支持2通道AD数据

2023-12-11 11:36:40

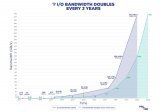

,PCIe标准几经迭代。PCIe最初作为一种串行接口引入,用于替代众多主板架构使用的并行总线, 但PCIe拥有一项独特特性:通道数量可从1个扩展至32个。 借助这一并行总线特性,PCIe兼容设备之间可以根据数据传输要求,建立宽度为1个、2个、4个、8个、16个甚至高达32个通道的链路

2023-11-30 12:15:01 310

310

随着英特尔Alder Lake CPU的发布,以及AMD 7000 Ryzen CPU的即将发布,PCIe 5.0 硬件终于成为现实。但什么是 PCIe 5.0?

2023-11-18 16:48:14 1298

1298

紫光的logos系列的PGL50H/PGL100H、logos-2全系列都集成gen2×4的PCIE硬核,且官方也提供了例程。

紫光的PCIE用起来还是挺方便的,生成IP的同时生成了对应的PCIE

2023-11-17 14:35:30

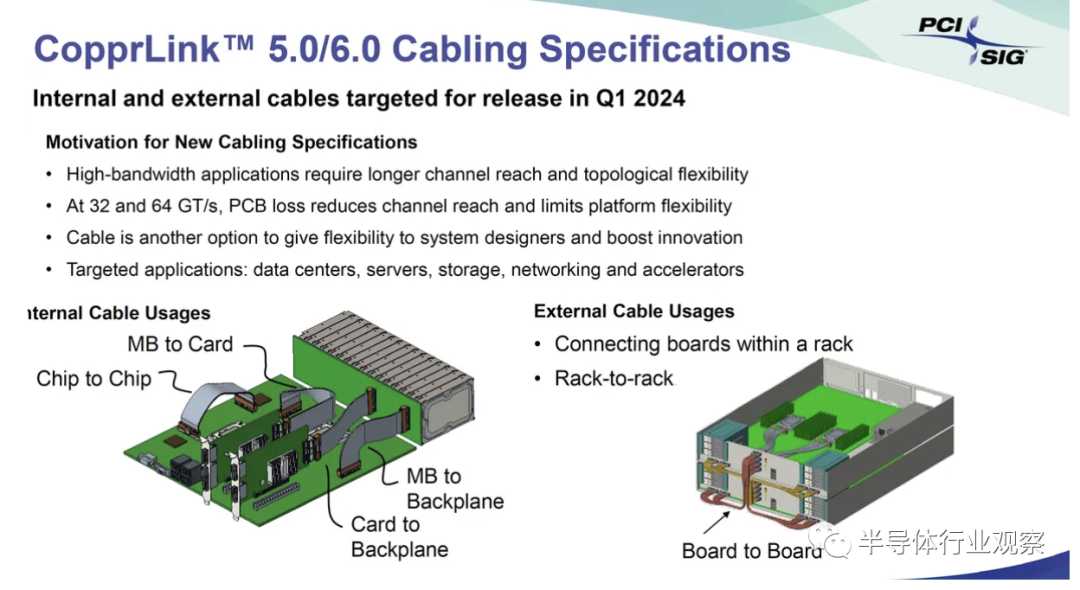

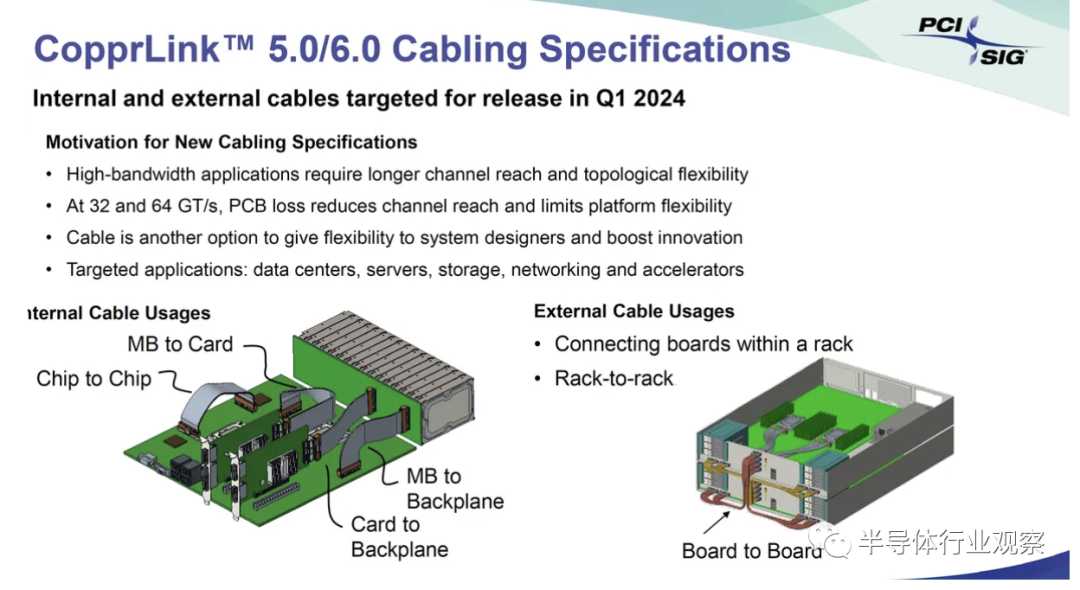

PCI SIG 本周表示,它正在开发 PCIe 5.0 和PCIe 6.0接口的布线规范,数据传输速率为 32 GT/s 和 64 GT/s。

2023-11-16 17:43:19 763

763

多种设备的连接。

2、传输速率简介

PCIe 分类、速度,按lane的个数分有 x1 x2 x4 x8 x16 (最大可支持32个通道),按代来分 有 gen1 gen2 gen3 gen4

PCIe

2023-11-02 09:31:28

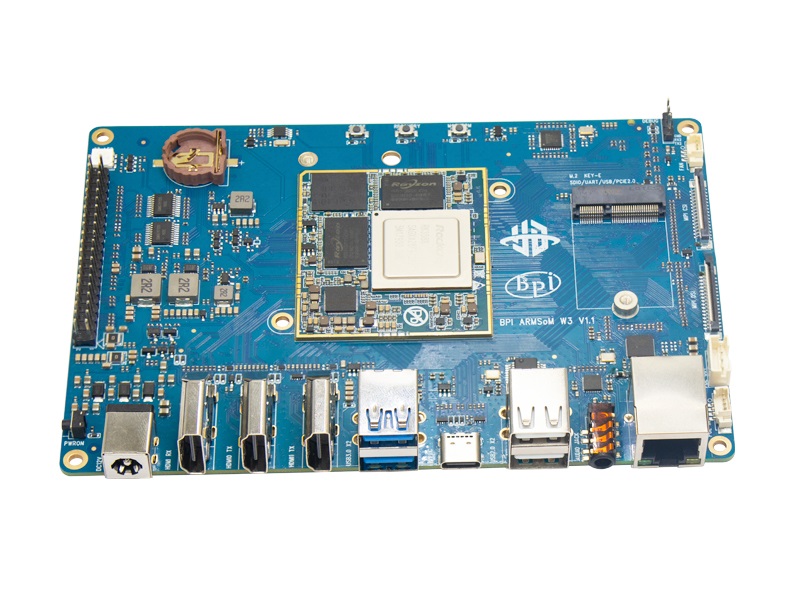

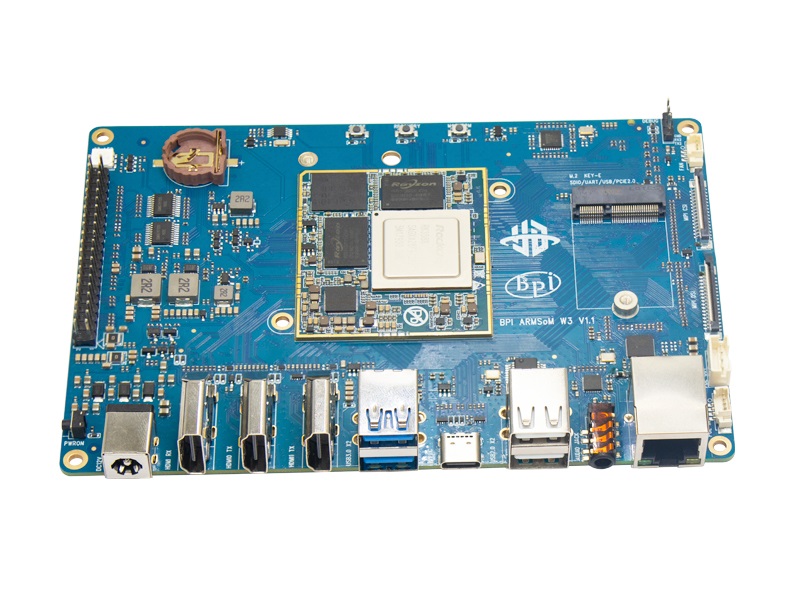

Banana Pi BPI-W3 RK3588平台驱动调试篇 [ PCIE篇 ] - PCIE的开发指南(二)

2023-11-02 09:24:05 275

275

本文我们将向大家介绍PCIe引脚定义以及PCIe协议层。

2023-09-26 11:39:14 5629

5629

Atlas200I A2+PCIE X4接口测试FPGA 实物图片

全爱科技QA200A2 Altas200I A2开发套件做了验证。

图 1-2 QA200A2 Atlas200I A2 开发套件实物图

2023-09-05 14:39:57

我们在进行PCIe RTL仿真时,由于PCIe ltssm协商过程比较复杂,导致PCIe ltssm进入L0状态所花费的时间比较长(大概在20~60分钟,因代码复杂度、服务器性能、PCIe速率

2023-08-17 09:42:22 721

721

本文档旨在提供关于将PCIe接口集成到基于AMBA的片上系统(SoC)的指导。

假设PCIe接口通过基于AXI或ACE协议的互连连接到SoC的其余部分。

读者应熟悉PCIe、AMBA AXI

2023-08-17 07:25:03

电子发烧友网为你提供Maxim(Maxim)MAX4950ACTX+T相关产品参数、数据手册,更有MAX4950ACTX+T的引脚图、接线图、封装手册、中文资料、英文资料,MAX4950ACTX+T真值表,MAX4950ACTX+T管脚等资料,希望可以帮助到广大的电子工程师们。

2023-08-15 18:50:47

电子发烧友网为你提供Maxim(Maxim)MAX4950CTO+T相关产品参数、数据手册,更有MAX4950CTO+T的引脚图、接线图、封装手册、中文资料、英文资料,MAX4950CTO+T真值表,MAX4950CTO+T管脚等资料,希望可以帮助到广大的电子工程师们。

2023-08-15 18:50:23

电子发烧友网为你提供Maxim(Maxim)MAX4950ACTX+相关产品参数、数据手册,更有MAX4950ACTX+的引脚图、接线图、封装手册、中文资料、英文资料,MAX4950ACTX+真值表,MAX4950ACTX+管脚等资料,希望可以帮助到广大的电子工程师们。

2023-08-15 18:45:11

电子发烧友网为你提供Maxim(Maxim)MAX4950CTO+相关产品参数、数据手册,更有MAX4950CTO+的引脚图、接线图、封装手册、中文资料、英文资料,MAX4950CTO+真值表,MAX4950CTO+管脚等资料,希望可以帮助到广大的电子工程师们。

2023-08-15 18:42:42

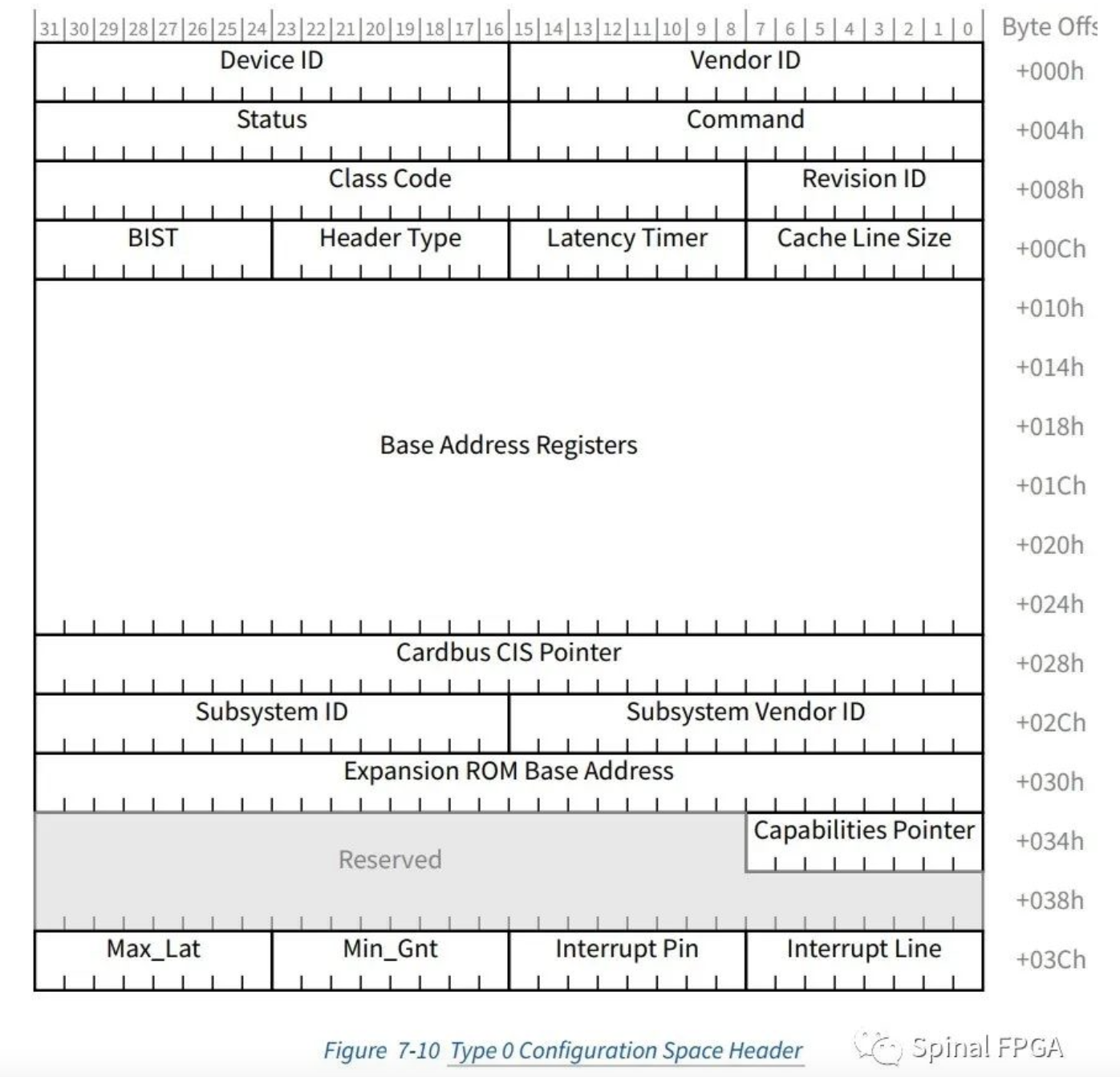

访问 PCI/PCIe 设备的流程 PCI/PCIe 设备的配置信息 PCI/PCIe 设备上有配置空间(配置寄存器),用来表明自己"需要多大的地址空间"。 注意,这是 PCI/PCIe 地址空间

2023-07-30 09:44:54 941

941 自2003年推出以来,PCIe发展至今已经从最初的1.0升级到了6.0,在上一篇文章中为大家介绍了PCIe基础知识:《什么是PCIe?》 ,本文则为大家简单介绍一下 PCIe 标准的演进历史以及

2023-07-26 08:05:01 867

867

要充分发挥PCIe 4.0的优势,需要具备兼容PCIe 4.0的主板和设备。如果你的设备只支持PCIe 3.0,那么你将无法享受到PCIe 4.0的速度和带宽优势。

2023-07-18 15:10:30 18123

18123 PCIe是一种高速串行计算机扩展总线标准,自2003年推出以来,已经成为服务器(Server)和PC上的重要接口。今天为大家简单介绍一下PCIe的发展历史以及它的工作原理。 一、PCIe的由来

2023-07-04 18:15:03 9759

9759 如果不是做主板类的工程师或者没有自己组装过电脑/服务器的,估计很多人并不了解PCIe是什么。

2023-07-04 09:30:03 5044

5044

最近在研究cocotbext-pcie的实现,对于学习PCIe还是挺有帮助的,陆陆续续做个总结,有时间也会在SpinalHDL下实现类似的方针功能。

2023-07-03 17:47:34 2282

2282

MAX13256具有可调过流门限,用于短路保护。不幸的是,这个阈值使得使用标准方法为设备设计缓冲器变得困难。本应用笔记介绍了如何为MAX13256设计电压缓冲器,同时考虑限流特性。

2023-06-25 14:22:18 582

582

PCIe 7.0规范的数据传输速率将再次倍增,达到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一个PCIe 7.0 x16通道可以支持512 GB

2023-06-25 10:48:38 506

506

✎ 编 者 按 读cocotbext-pcie源码,有部分牵涉到数据链路层。虽然自工作以来接触到PCIe还是蛮多的,但一般往往专注在TLP层,对于数据链路层还是接触的比较少的。PCIe

2023-06-25 10:31:17 1457

1457

PCIe 7.0规范的数据传输速率将再次倍增,达到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一个PCIe 7.0 x16通道可以支持512 GB

2023-06-21 11:32:14 494

494

PCIe M.2 接口规范

2023-06-19 10:02:30 18

18 refclk1(硬件上已固定),可参考下图:

4. 其他设置可保持默认,点击 Generate 生成 PCIE IP;:

5.关闭本工程,按此路径打开 Example 工程:

2

2023-06-13 15:50:05

我是一名PCIe新手,想了解以下问题:

1、如何测试PCIe?

2、如何读写PCIe(两块开发板通过PCIe线互连,分别配置为RC和EP)?

3.如何支持NTB?

2023-06-12 06:05:51

/class/pci_epc 中使用 pcie 端点控制器,并在根复合体端 (x86) 上使用 lspci 和 pcitest 测试接口。

问题是,PCIe端点控制器设备不存在(/sys/class

2023-06-09 08:23:25

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:30:21 526

526

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:29:55 805

805

Layerscape MPU 中是否有支持 PCIe GEN3 16 通道的 EVB?

2023-05-30 08:01:56

PCI Express® 6.0 (PCIe® 6.0) 规范由 PCI-SIG® 于 2022 年 1 月发布。最新一代的 PCIe 标准带来了许多激动人心的新功能,旨在提高计算密集型工作负载的性能,包括数据中心、 AI/ML 和 HPC 应用程序

2023-05-22 17:27:51 4386

4386

ZYNQ7045的PCIE电路设计,板卡使用插针式连接器,引出了PCIE信号,未使用金手指。为了插入机箱设计了扩展版,插座与插针对应,带有PCIE金手指。目前遇到的问题是,当板卡连接扩展板使用金手指

2023-05-16 11:07:40

有没有办法确认 i.MX6SX PCIe RX 终端的设置。我在 i.MX6SX 上看到 PCIe 实现的 PCIe RX SI 结果可能表明 RX 终端设置为 OFF,我正在寻找一种方法来确认。PCIe PHY 寄存器没有内存映射,我不确定控制器是否正在更改设置。

2023-05-12 06:40:33

差分探头是一种常用的测试仪器,在PCIE测试中也有广泛的应用。本文将介绍差分探头在PCIE测试上的应用及其优势。

2023-05-11 10:54:14 450

450 你好

作为我们在 ls1028 上努力的一部分

我们通过 pcie 将自定义 fpga 连接到 M.2 连接器(通道 C/2 - j16)

相关uboot日志:

U-Boot

2023-05-09 12:00:30

我们可以将多个 PCIe 设备 (IC) 连接到一般的单个 PCIe 控制器(在我们的案例中更具体地说是 NXP LS20xxA 处理器)吗?

例如,将四个不同的 PCIe x1 设备 (IC

2023-05-05 07:35:41

我们有将 SATA HDD 连接到 IMX8M Plus 处理器的要求,但我们只有单通道 PCIe 3.0 接口。

您能否建议从PCIe到sat接口的转换器以支持外部硬盘驱动器(最大 2TB)

2023-05-04 07:19:49

我们有两张 LS1028a 卡通过背板连接,一张卡运行 RCW,选择 PCIe_RC,另一张卡选择 PCIe_EP。这些卡与 Flexbuild v2012 U-Boot & Linux 一起移植。

如何证明这些处理器之间通过 PCIe 接口进行数据通信?

2023-05-04 06:04:29

液压缓冲器强度是否能够调节,取决于液压缓冲器的种类,目前市面上较为常用的液压缓冲器包括可调液压缓冲器、不可调液压缓冲器,这两种缓冲器调节强度的实际效果是不一样的。

2023-04-24 16:12:01 2147

2147 类型控制 PCIe 控制器设备类型、PHY 类型、SRIS 模式和手动通道翻转启用。0000b - 端点0100b - 根联合体的根端口0110b - 上游交换机端口所有其他值均保留。在我写入寄存器

2023-04-18 07:45:06

带 2GB DDR3 的定制 LS1043A 板。我们在 PCIe 通道和 2 GbE RGMII 端口上有一个 M.2 WiFi 卡。他们中的任何一个都会使用 iPerf 自行完成一个 Gb

2023-04-18 07:30:13

+ ) 已设置。但是设置这个寄存器的代码在两个不同版本的驱动程序中也有很大不同。有没有人设法让 PCIe 与主线内核驱动程序一起工作?我觉得它应该经过测试,并且应该有效。移植驱动程序似乎很麻烦,因为整个 phy 接口已经改变了很多。

2023-04-14 08:12:05

PCIe接口从2001年发展至今,在协议的完整性上已经建立足够高的"护城河",重新定义一个接口协议在性能上超越PCIe,短期内一方面没有企业会有这个动力,另一方面技术的维度,也没有可预期的雏形创新。

2023-04-13 11:10:00 2899

2899 IC CLOCK GENERATOR PCIE 42TQFN

2023-04-06 15:33:36

ICMUX/DEMUX2:1PCIE42TQFN

2023-04-06 15:33:30

ICMUX/DEMUX2:1PCIE42TQFN

2023-04-06 15:33:25

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:34:28

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:34:28

IC MUX DISPLAYPORT/PCIE 56TQFN

2023-04-06 11:33:53

我对第 3 代存储进行了测试。但是 LS1046A RDB 指示此存储是 Gen2。那么,我的问题是:LS1046ARDB 是否支持 PCIE 3.0?

2023-04-06 06:30:54

M31 PCIe 5.0 PHY IP,用于存储和高带宽连接 M31 PCIe 5.0 PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。PCIe 5.0 IP支持一系列PCIe

2023-04-03 19:57:12

用于存储和高带宽连接的M31 PCIe 4.0 PHY IP–具有16GT/s的最高速度PCIe 4.0 PHY IP M31 PCIe 4.0 PHY IP为高带宽应用提供高性能、多通道

2023-04-03 19:54:58

M31 PCIe 3.1 PHY IP M31 PCIe 3.1 PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。PCIe 3.1 IP支持一系列完整的PCIe 3.1基本应

2023-04-03 19:50:56

M31 PCIe 2.1 PHY IP M31 PCIe 2.1收发器IP提供了一系列完整的PCIe 2.1基本应用程序。它符合PIPE 3.0规范。该IP集成了高速混合信号电路,以支持

2023-04-03 19:47:28

是 VDD_PCIE_DIG_1P8_3P3引脚——我们在定制板中将其设置为 1v8。但是,MEK 板使用 3v3。定制板i.MX8QXP-MEK VDD_PCIE_DIG_1P8_3P3电压变化是否也需要更改设备树?PHY 链路问题是否是由模块和处理器之间的阻抗不匹配引起的?

2023-04-03 06:31:15

我在访问 PCIe BAR 空间时遇到 Async Serror。很奇怪。能帮忙看看是什么原因吗?谢谢。 〜#dmesg | grep pcie [0.000000] 内核命令行:console

2023-04-03 06:06:54

PI3PCIE2415EVALBOARD

2023-03-30 11:41:37

PI2PCIE2412-EVALUATIONBOARD1

2023-03-30 11:41:15

QM5i系列虹科Spectrum推出两款全新PCIe数字化仪卡。新产品凭借卓越的GHz信号采集和分析能力,使虹科M5i系列旗舰产品再度升级。单通道和双通道的新产品不仅拥有10GS/s的超快采样率

2023-03-30 10:40:48 488

488

PCIE-52P90H

2023-03-29 22:43:17

1、问题:RK3568平台开机后,插网线,lspci 查找不到PCIe设备,请问如何进一步定位问题点?2、dtsi配置vcc3v3_pcie: gpio-regulator {compatible

2023-03-29 15:01:34

PCIe 3.0,2 通道(4 通道),差分 2:1 Mux/DeMux。3.3V

2023-03-28 12:41:12

与PCI/PCIX桥在PCI/PCIX总线体系结构中的作用类似,PCI Express(PCIE)交换机的功能是扩展连接以允许PCIE串行互连中的主机控制器访问更多的终端设备建筑学16通道PCIe

2023-03-27 10:54:11 1

1 我想为我们的项目使用 LX2080A 处理器,它只有 2 个 USB 3.0 控制器。我的项目需要五个 USB 端口。我想知道我是否可以在其中一个 USB 控制器中使用 USB 集线器 IC(具有

2023-03-27 08:54:43

电子发烧友App

电子发烧友App

评论