1 kOhms ±1% 芯片电阻 0202(0505 公制) 射频,高频率 厚膜

2024-03-14 21:40:29

50 Ohms ±2% 125W 芯片电阻 射频,高频率 厚膜

2024-03-14 20:42:31

公司有没有稳固的网络系统?”来自一名金融类高频交易员的疑问。 针对以上疑问,可想而知一个精准的时间对金融行业的重要性。选用北斗卫星同步时钟可以保证时间的精准交易的可靠性。 GP/GNSS 卫星具有高精度的原子钟,因此

2024-03-05 10:03:46 90

90

我有一个基于 4046 IC 的 VCO 电路,可产生随输入电压变化的 TTL。

我想将这个变频信号转换为具有固定幅度(带宽小于 1MHz)的正弦波。

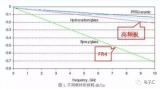

我尝试使用RC或LC滤波器,但是,振幅随频率

2024-03-01 09:07:18

detected on one of the USB endpoints. The event data will provide the endpoint number. 当高频率发送hid数据出现此

2024-02-28 06:06:30

ADF4377BCCZ 具有集成压控振荡器(VCO)的整数N相控阵锁定环路(PLL)非常适合数据转换器和混合信号前端(MxFE)时钟应用。该高性能PLL的优点是−239 dBc/Hz、超低

2024-02-26 09:29:37

XG5032HAN晶体振荡器通过其卓越的低抖动特性,为需要高频率精度和稳定性的电子设备提供了理想的解决方案。无论是在高性能的数据通信、精密测量XG5032HAN都能提供高质量、可靠的性能。同时,宽广

2024-02-23 15:52:51 0

0 和低通滤波器进行解调制。总延迟时间由内部VCO时钟频率决定,用户可以通过改变外部电阻来方便地改变VCO频率。PT2399具有低失真(THD

2024-02-21 14:37:15 0

0 可以使用直流和交流耦合来提供。不仅限于JESD204B应用,14个输出均可单独配置为传统高性能时钟系统输出。 超低噪声时钟抖动消除器SC6301具有高性能

2024-02-19 09:41:40

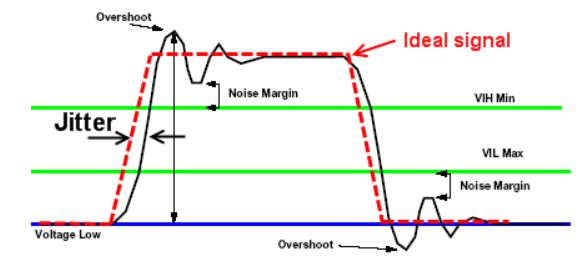

,通常低于 100 飞秒 (fs),以保持系统性能。这些时钟还必须长期保持低抖动规格,且不受温度和电压的影响。 某些抖动是由信号路径噪声和失真引起的,使用重复时钟和重定时技术可以在一定程度上减少抖动。不过,抖动也是由时钟源产生的,时钟源通常是振荡器。这是由于各

2024-02-13 17:47:00 621

621

在ILLD看到使用20M晶振能够达到200M,用40M晶振,可以达到400M,找不到最高频率的,好心人给说下,谢谢了

2024-02-05 09:08:55

锁相环中的压控振荡器的固定频率是怎么确定的?是要和电网频率一致吗? 锁相环(PLL)是一种常见的电路和控制系统,广泛应用于通信、信号处理、时钟同步等领域。锁相环中的压控振荡器(VCO)是其核心部件

2024-01-31 15:42:45 144

144 电子发烧友网站提供《毫微微时钟网络同步器、抖动衰减器和时钟发生器RC32112A 数据表.pdf》资料免费下载

2024-01-31 10:09:17 0

0 基于MG7050 HAN的声表差分多输出晶体振荡器(HCSL),采用两路或四路差分HCSL(高速电流驱动逻辑)输出,可以减少外部扇出缓冲区,特别适用于需要超低抖动、高频率范围内稳定工作的应用场

2024-01-29 15:37:22 0

0 相位抖动是从哪来的?通信中有哪些抖动? 相位抖动是指信号在传输过程中产生的相位变化,导致信号的相位偏离理想值的现象。它是由多种因素引起的,包括时钟不准确、传输介质不稳定、信号传输路径不确定等。 时钟

2024-01-25 15:29:28 171

171 会导致晶振的输出频率出现一定的不稳定性,从而影响到系统的时钟同步和信号处理。相位抖动常常以皮克-到-皮克的相位偏移量来衡量,通常以ps级别或fs级别来表示。相位抖动在通信系统、时钟系统和高精度测量设备中都是非常重要

2024-01-25 13:51:07 126

126 云计算机、高性能计算机、nVME存储、以太网络及AI加速器应用。 原理方框图典型特征◆符合PCIe 3.0◆PCIe 3.0相位抖动:0.48ps RMS(典型高频)◆兼容LVDS输出◆电源电压为

2024-01-24 17:31:16

晶振频率和时钟频率本质上有何区别呢?时钟频率有什么作用? 晶振频率和时钟频率是两个相关但又有所不同的概念。下面我们将逐一介绍这两个概念的含义、区别和作用。 首先,我们来了解晶振频率。晶振是一种

2024-01-24 16:11:35 307

307 EMC传导高频不过怎么改善? 电磁兼容性(EMC)是指不同电子设备在相互操作时,能够互不干扰且不受外界电磁干扰的能力。在实际场景中,高频传导是EMC问题中常见的一种情况。本文将详细介绍高频传导的原因

2024-01-23 13:53:03 1576

1576 ,包括时钟抖动、噪声抖动、跳变抖动和漂移抖动。 时钟抖动是指时钟信号在频率和相位上的变化。时钟信号是大多数电子系统中用于同步和定时的关键信号,其稳定性对系统的性能有着重要影响。时钟抖动会导致测量结果的不确定性

2024-01-19 15:01:31 253

253 飞秒 (fs))以保持系统性能。尽管温度和电压会发生变化,但它们还必须随着时间的推移保持其低抖动规格。 一些抖动是由信号路径噪声和失真引起的,使用时钟恢复和重定时技术可以在一定程度上减少抖动。然而,抖动也由时钟源产生,时钟源通常是一个振荡器。这

2024-01-01 13:55:00 264

264

我是用万用板做的电路.输出高频率的方波波形失真比较大.是不是采用万用板的原因??,有经验的指点一下,如何解决.谢谢!

2023-12-25 07:46:47

小型化高频率恒温晶振是一款尺寸为25.4*25.4*12.7mm的高稳定、高性价比OCXO。具有2E-10业内同级别最高的温度稳定性,日老化优于0.2ppb/天性能;广泛应用于基站、LTE、GSM

2023-12-22 11:02:38

注意哪些事项?次部分的参考地是否需进行与模拟/数字地进行一定的隔离处理?

疑问2:如果外部没有高精度的时钟源设备,是否有替代方案可以实现单端转差分时钟输出?并且时钟抖动质量可以在

2023-12-22 08:19:31

等应用已集成越来越多的PCIe终端,矽力杰新一代高性能PCIe时钟缓冲器SQ82100可以为系统提供20路超低附加抖动的LP-HCSL参考时钟,能够简化系统布局,进一步提高

2023-12-20 08:19:38 240

240

IC设计为什么需要仿真模拟?仿真模拟的重要性有哪些? IC设计(集成电路设计)是指利用EDA工具(电子设计自动化工具)设计出满足特定功能和性能要求的集成电路芯片。仿真模拟是IC设计过程中至关重要

2023-12-19 11:35:38 850

850 晶振标称频率是什么?如何区分高频率晶振和低频率晶振? 晶振标称频率是指晶振器在设计和生产过程中设定的频率,通常以赫兹(Hz)为单位表示。它表示了晶振器在正常工作条件下振荡的频率,也是晶振器用于计时

2023-12-18 14:30:52 373

373 同步整流芯片U7116是一款高频率、高性能、CCM 同步整流开关,可以在 GaN 系统中替代肖特基整流二极管以提高系统效率。

2023-12-14 16:32:19 352

352 、引脚等。

3、信号输出(白噪声)。

通常来说,晶体振荡器的相位噪声在远离中心频率的频率下有所改善。TCXO和OCXO振荡器以及其它利用基波或谐波方式的晶体振荡器具有最好的相位噪声性能。采用锁相环

2023-12-14 09:19:08

AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2023-12-12 14:25:17

你好,我们在设计中需要使用 hmc7044 产生一系列频率为 204MHz 且相位对齐的时钟,并且所有的 204MHz 时钟都由 外部VCO输入时钟 816MHz 所产生。

目前所有的时钟都已经获取

2023-12-01 10:15:39

的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。...

2023-11-28 14:33:57 0

0 电子发烧友网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

1 电子发烧友网站提供《时钟和频率合成的应用领域.pdf》资料免费下载

2023-11-27 10:41:13 2

2 同步整流是一种电力变换技术,用于将交流电转换为直流电。同步整流技术就是大大减少了开关电源输出端的整流损耗,从而提高转换效率,降低电源本身发热。U7612同步整流ic是一款高频率、高性能、CCM同步整流开关,可以在GaN系统中替代肖特基整流二极管以提高系统效率。典型应用于30W快充应用。

2023-11-15 09:38:55 272

272

STM32F103最高频率是72Mhz,mm32F103最高主频为96MHz。

2023-11-09 06:15:52

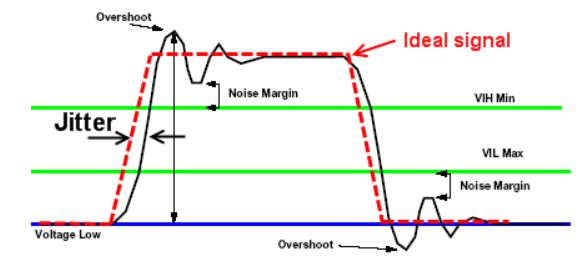

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

相位噪声和抖动是对时钟频谱纯度的两种表述形式,一个是频域一个是时域,从原理上来说,它们是等效的。

2023-10-30 16:02:46 686

686

频率的比例决定了锁定的频率倍数,因此对于VCO的频率稳定性要求比较高。 2. 延迟:VCO的输出延迟对于PLL系统的工作非常重要。如果VCO的输出延迟太大,则可能会导致锁定时间变长或者无法锁定。 3. 噪声:VCO的输出噪声会影响PLL系统的性能和稳定性。因此,要求VCO的输出噪声较

2023-10-30 10:46:44 358

358 电机驱动系统如何在提高频率的同时抑制噪声? 通过电机驱动系统在提高频率的同时抑制噪声是当今电力机械行业面临的一个普遍问题。为了满足客户的要求,提高电机驱动的效率和可靠性,同时减少噪声和振动,电机驱动

2023-10-29 16:23:53 555

555 至15V 这款高性能PLL可用于生成混频器本振(LO)频率或ADC/DAC时钟,适用于微波点对点系统、测试和测量设备或汽车雷达中的应用。 本应用笔记

2023-10-28 14:45:41 6895

6895 能检测较高频率振动传感器有哪些?震动频率1hz到1000hz,不知道加速度陀螺仪能否胜任。

2023-10-27 06:41:38

高频板是指电磁频率较高的特种线路板,用于高频率(频率大于300MHZ或者波长小于1米)与微波(频率大于3GHZ或者波长小于0.1米)领域的PCB,是在微波基材覆铜板上利用普通刚性线路板制造方法的部分工序或者采用特殊处理方法而生产的电路板。一般来说,高频板可定义为频率在1GHz以上线路板。

2023-10-26 17:21:47 2357

2357

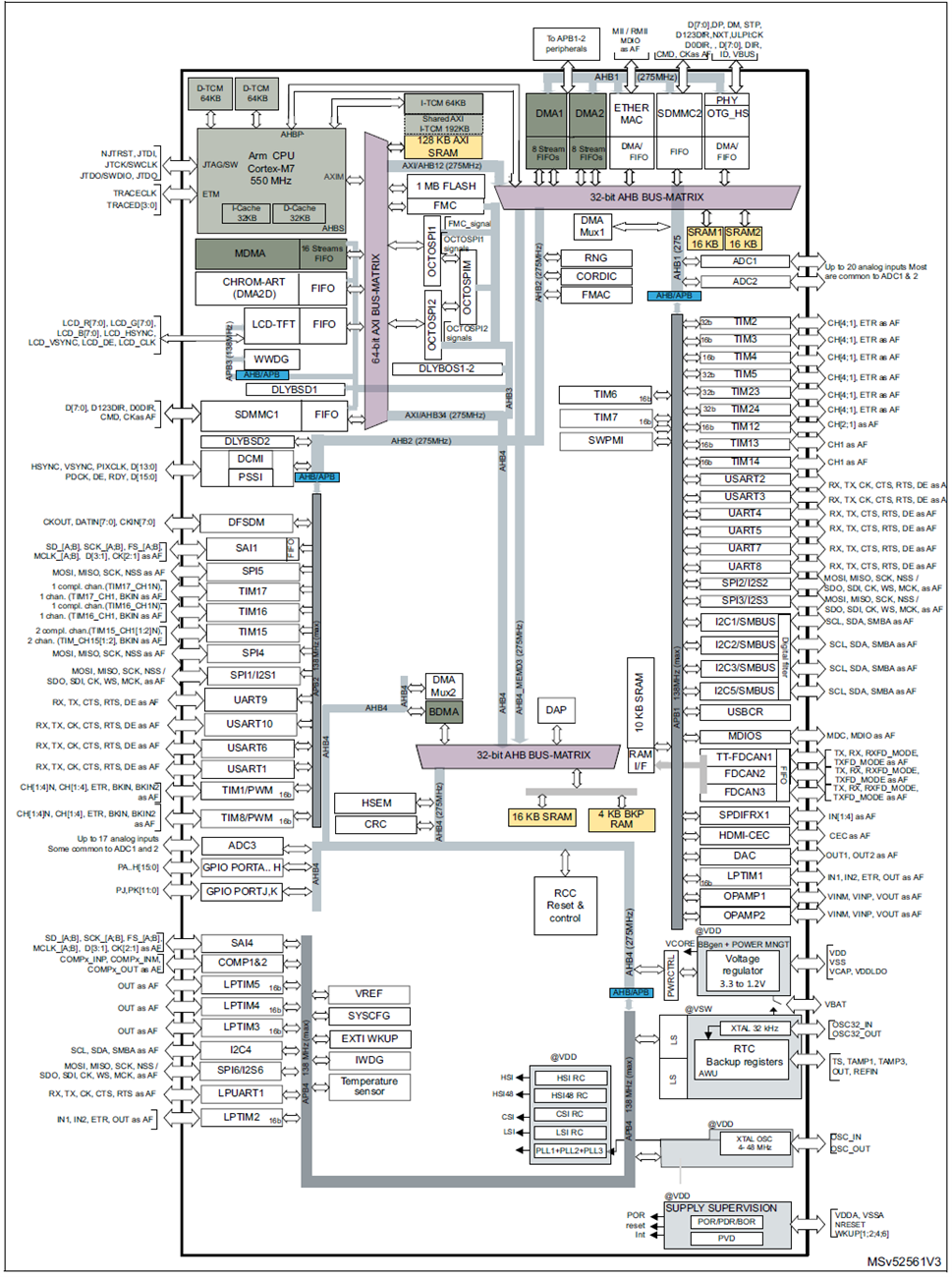

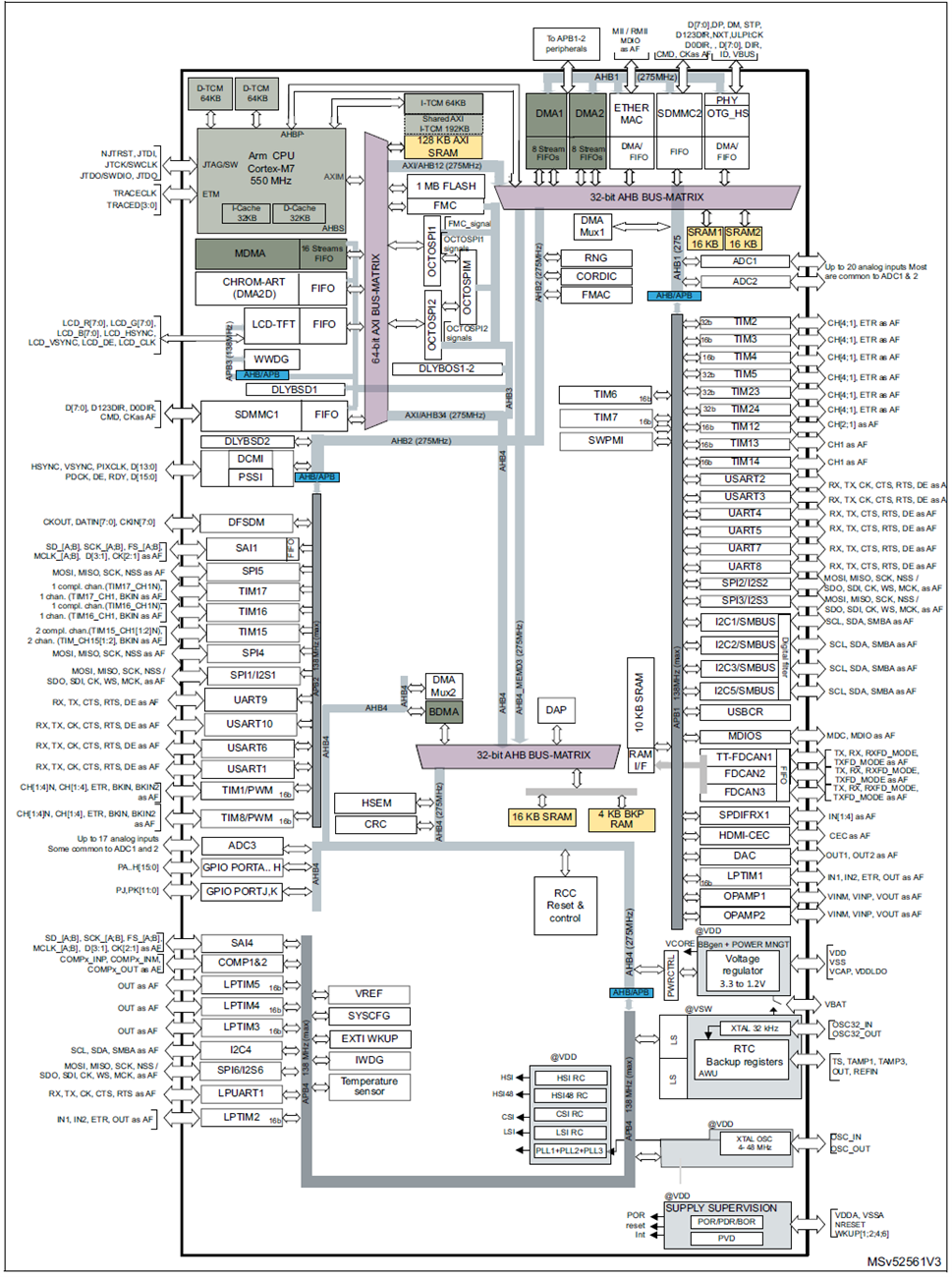

针对常规STM32系列性能测试所引起的准确度低、可靠性差、操作困难等问题,文中提出了一种关于I/O响应频率以及定时器最高频率的极限性能测试方法。通过对STM32H7时钟频率进行最高频率配置,分别

2023-10-24 14:51:18 666

666

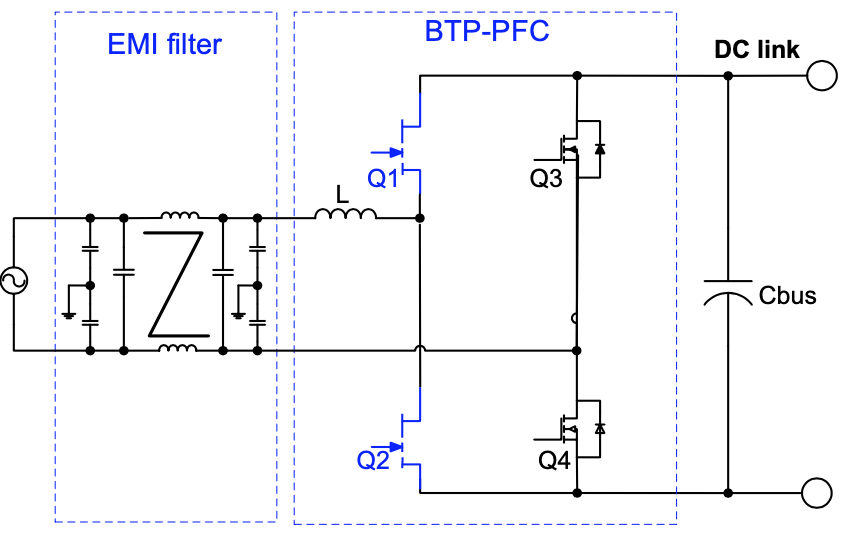

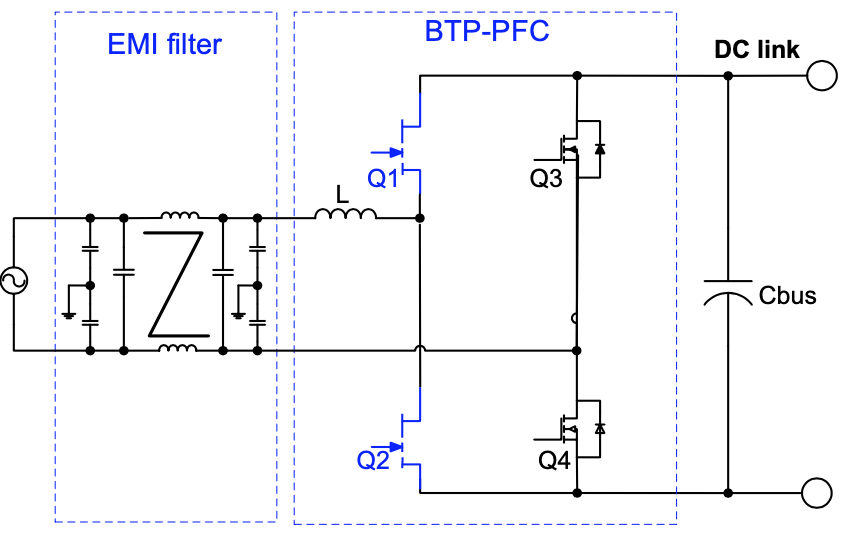

众所周知,氮化镓功率器件为电力电子系统提高频率运行,实现高功率密度和高效率带来可能。然而,在高频下需要对EMI性能进行评估以满足EMC法规(例如EN55022 B类标准)要求。

2023-10-16 14:32:45 1139

1139

at89c51的io输出pwm,级数256级,用定时器实现那么它的最高频率能到多少

2023-10-08 07:16:15

如果时钟是12mhz输入的话,那么捕获可以多高频率

2023-09-25 07:10:57

如果供电是3.6v,不考虑其他因素,能工作的最高频率是多少

2023-09-22 06:27:35

在之前的 IC 设计中,关注的参数主要是性能(timing)和面积(area)。 EDA 工具在满足性能要求的情况下,最小化面积。功耗是一个不怎么关心的问题。 CMOS 工艺在相对较低的时钟频率下

2023-09-21 07:38:14

在芯片设计中,为了便于定位故障,有时候需要确认部分时钟频率是否正确,需要部分debug手段。常见的方式是:将时钟信号引到芯片管脚,通过仪器测量。这类方式必须要测量仪器,并且需要熟练使用,耗时较长。还有一种简单的方式,通过时钟计数的方式判断时钟频率是否正确。

2023-09-20 14:17:06 384

384

太赫兹频率范围和甚高频率的区别 太赫兹频率范围和甚高频率(SHF)是电子工程中两个重要而又有区别的概念。在电磁波谱中,太赫兹频率范围介于毫米波和红外线之间,主要集中在0.1-10 THz范围内

2023-09-19 17:49:56 565

565 高频率的测试需求,并增加全新的“模拟特征分析”功能,通过图形快速分析元器件的好坏。R2 可手动操作使源阻抗从100Ω切换到1.4kΩ,提高了低电阻测量的稳定性。为

2023-09-17 21:05:43

时钟分频电路通过将输入的高频时钟信号分频,生成较低频率的时钟信号。它通常基于计数器和逻辑门实现,用于将高频时钟信号分解成系统所需的各种频率。

2023-09-14 14:53:57 4881

4881 如何确定滤波器共模插损的最高频率? 滤波器是一种通信系统中常用的电路元件,它可以滤除信号中不需要的频率成分,使得信号只包含期望的频率成分,在电路系统中有非常广泛的运用。 在滤波器

2023-09-12 11:50:09 322

322 的滤波器是非常重要的,因为过滤频率对电器设备的性能和安全性有直接影响。因此,本文将深入探讨如何依据电源线共模骚扰的最高频率来选择滤波器插损的最高频率。 1. 理解电源线共模骚扰 电源线共模骚扰是由于电力系统中所产生的

2023-09-12 11:48:05 426

426 时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 502

502

同步整流芯片U7612是一款高频率、高性能、CCM 同步整流开关,可以在GaN系统中替代肖特基整流二极管以提高系统效率。

2023-09-06 15:54:13 910

910 高频变压器频率对电压的影响 高频变压器是近年来越来越广泛使用于电子工业的一种电子元件。它是由磁性材料、绕组及铁芯组成,用来实现电压变换、隔离、阻抗匹配和电能传递的器件。与低频变压器相比,高频变压器

2023-09-04 17:23:44 1307

1307 数字频率和模拟频率的关系 数字频率和模拟频率是电子领域中经常涉及到的两个概念。这两个概念虽然有所相似,但在实际应用中又有所不同。数字频率以数字化信号为主要参考,而模拟频率则以连续变化的模拟

2023-08-27 15:37:02 4185

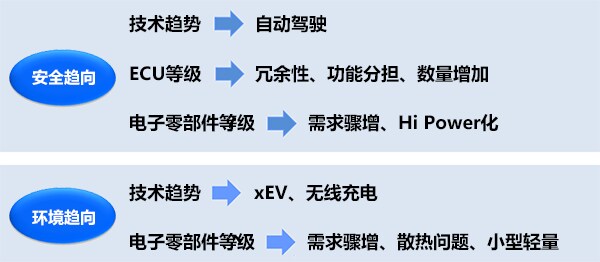

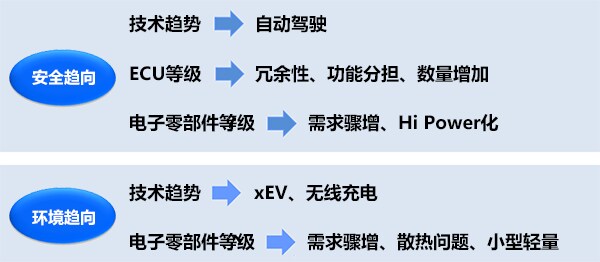

4185 车载可降低故障风险的高可靠性高频率功率电感器方案。 目次 汽车电子的动向 车载零部件要求的环境的变化 针对各种ECU分别提出最佳解决方案 高可靠性车载用高频率功率电感器的产品概述 高可靠性车载用高频率功率电感器的产品概要、

2023-08-22 16:26:24 371

371

基于FPGA的高频时钟的分频和分频设计

2023-08-16 11:42:47 0

0 电子发烧友网站提供《PI6C5913004最低输出抖动缓冲器IC 确保40GE/100GE设计性能.pdf》资料免费下载

2023-07-25 14:45:10 0

0 “全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错

2023-07-24 11:07:04 655

655

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 959

959

在电磁兼容的辐射发射测试中,最常见的就是时钟辐射超标,随着系统设计复杂性和集成度的大规模提高,电子系统的时钟频率越来越高,处理的难度也越来越大。时钟辐射的症结在于,时钟信号对应的频域为窄带频谱,能量

2023-06-27 14:45:22 649

649

、氧化锆等陶瓷材料为基板,通过特殊工艺制作而成的,具有耐高温、高频率、高稳定性等特点,是高频电路设计中不可替代的材料之一。

2023-06-19 16:45:58 670

670 ,经过内部的PLL倍频为较高频率,FPGA需要25M或一下的时钟输入。

我的问题是DSP和FPGA的时钟信号如何产生?

2023-06-19 06:43:17

桥式拓扑结构中放大了氮化镓的频率、密度和效率优势,如主动有源钳位反激式(ACF)、图腾柱PFC 和 LLC(CrCM 工作模式)。随着硬开关拓扑结构向软开关拓扑结构的转变,初级 FET 的一般损耗方程可以被最小化。更新后的简单方程使效率在 10 倍的高频率下得到改善。

2023-06-15 15:35:02

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 1121

1121

高性能的时钟器件是高带宽、高速率、高算力、大模型的基础。核芯互联近日推出面向下一代数据中心应用的超低抖动全新20路LP-HCSL差分时钟缓冲器CLB2000,其业界领先的附加抖动性能远超PCIe Gen 5和PCIe Gen 6的标准。

2023-06-08 15:29:55 805

805

如何改变spi的时钟频率? 改变SPI的时钟频率需要以下步骤: 1. 选择合适的时钟源和分频器:SPI接口的时钟源可以是内部时钟或外部时钟,需要根据具体情况选择;同时需要根据所需的SPI时钟频率

2023-06-03 16:36:02 2126

2126 高频响应压力变送器的种类很多,其中应用最早的是磁致伸缩爆震传感器,主要由磁芯、永磁体和感应线圈组成。高频响应压力变送器的作用是测量发动机抖动的程度,在发动机爆震时调整点火提前角。下面将介绍高频响应压力变送器的工作原理、工作频率、安装位置及故障维修。

2023-06-03 10:31:05 488

488

和大侠简单聊一聊数字电路设计中的抖动,话不多说,上货。

既然说到了抖动,那么什么是抖动?那首先我们就来了解一下什么是抖动。

一、抖动的几个重要概念

1、抖动的基本概

在理想情况下,一个频率固定

2023-06-02 17:53:10

首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 1020

1020

我们使用 RFID IC NXP MFRC 500-01T PACKAGE SOIC-32,我想要 MFRC 500-01T 的替代推荐 IC。

2023-05-30 13:23:41

) 以及其他通常要求时域抖动规范(如周期)的应用生成时钟- 周期和周期抖动。 然而,对于串行解串器 (SerDes)、千兆以太网 (GbE)、10 GbE、同步光网络/同步数字体系 (SONET/SDH) 和光纤通道等高速接口,情况就不同了。有严格的频域抖动要求。 为了正常运行,这些高速接口依赖于低频

2023-05-26 22:15:02 1385

1385 无线通信系统需要采用较高频率的信号的原因是什么?

2023-05-10 17:14:16

PD/QC快充电源ic U6648具有±5%的随机频率抖动功能,开关频率抖动分散了谐波扰动能量,获得良好的EMI特性。

2023-05-08 10:53:03 259

259 随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写出来的代码可能无法满足时序要求。

2023-05-06 09:33:27 773

773

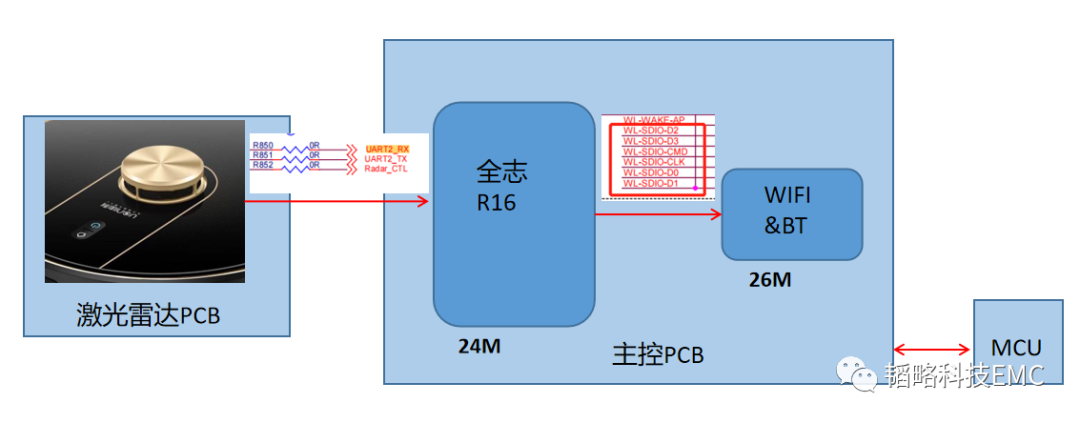

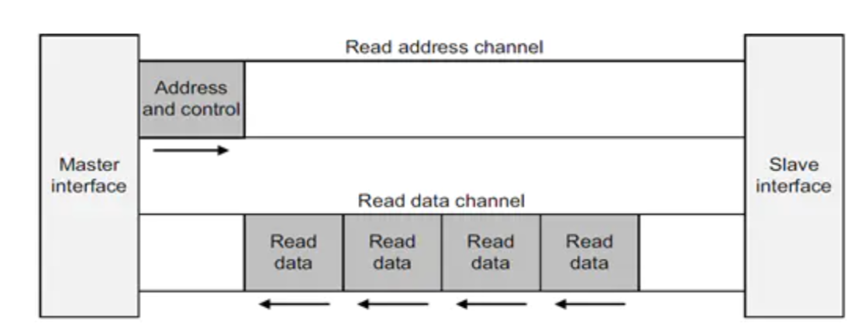

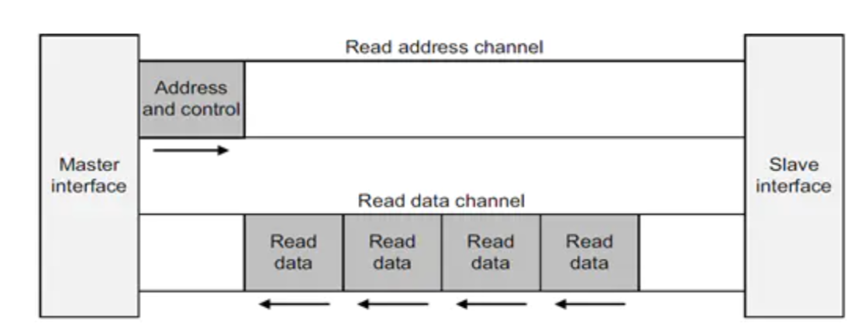

AMBA AXI协议支持用于主从模块之间通信的高性能、高频率系统设计。

2023-05-04 14:35:14 1246

1246

当锁相环达到锁定状态时,VCO输出频率与参考频率相等(假设没有分频),那么它们的相位是不是相等呢?还是保持恒定的相位差呢?如果是相位相等,那么是怎么使它们的初相相等的呢?如果是保持恒定的相位差,那么

2023-04-24 11:32:51

鉴频鉴相器,当两输入信号频率相同但相位不同的时候,有电压差输出,然后去控制VCO,改变反馈信号频率。这不是导致两输入频率不同了,这如何锁住相位啊,使VCO的频率等于参考信号的频率?求高人指点。

2023-04-24 10:23:02

) 频带内和频带外 (VCO) 噪声的影响。基准时钟发生器的相位噪声性能需要在PLL环路带宽内和带宽外都表现得很出色,以符合更加严格的抖动技术规格要求。

2023-04-17 10:37:30 357

357

展频IC在4M时钟上的应用

2023-04-14 10:12:27 0

0 需要保护模拟输出的瞬态过电与其产生的低压(<24V)和低频率(<10kHz)信号差异巨大。工业瞬态过电为高压(高达15kV)、高频率(通常时间短于100ns)。您的电路应当利用这些差别提供保护,同时不影响模拟输出的信号质量。

2023-04-13 09:23:46 564

564

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 810

810

模拟电路大佬,关于差分电路+环形振荡器结构,对比两种结构是否能够提高频率!!!图一为原电路,图二为改良电路。

2023-04-08 21:24:03

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1633

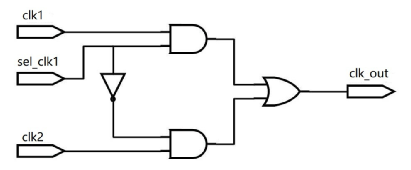

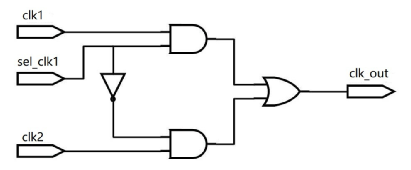

1633 随着各种应用场景的限制,芯片在运行时往往需要在不同的应用下切换不同的时钟源,例如低功耗和高性能模式就分别需要低频率和高频率的时钟。两个时钟源有可能是同源且频率比呈倍数关系,也有可能是不相关的。直接使用选择逻辑进行时钟切换大概率会导致分频时钟信号出现毛刺现象,所以时钟切换逻辑也需要进行特殊的处理。

2023-03-29 11:41:29 908

908

过滤器高频率 2200PF 0805

2023-03-28 15:00:04

抖动和相位噪声是晶振的非常重要指标,本文主要从抖动和相位噪声定义及原理出发,阐述其在不同场景下对数字系统、高速串行接口、数据转换器和射频系统的影响。

2023-03-26 09:09:11 693

693

电子发烧友App

电子发烧友App

评论