LMK6 时钟发生器 计时 评估板

2024-03-14 23:22:15

CS2200-CP 时钟发生器 时钟定时 mikroBUS™ Click™ 平台评估扩展板

2024-03-14 23:11:37

Si5350,Si5351 时钟发生器 计时 评估板

2024-03-14 22:30:46

Si5348 时钟发生器 计时 评估板

2024-03-14 22:30:44

Si50122-A5 时钟发生器 计时 评估板

2024-03-14 22:30:31

ICS501 时钟发生器 时钟定时 mikroBUS™ Click™ 平台评估扩展板

2024-03-14 22:03:12

Si5351A 时钟发生器 时钟定时 STEMMA QT 平台评估扩展板

2024-03-14 20:37:59

,ADC值相差不大,但是采用PLL异步时钟,复位后有概率ADC采样值发生偏差(所以我怀疑复位后ADC时钟出现了问题)。

补充:问题芯片具体是L431RCT6,我还有一块L431CCT6的芯片,同样的配置,同样的代码逻辑,ADC采样值就很准确且稳定。

以下是时钟树与ADC配置(PLL时钟)

2024-03-08 07:32:15

电子发烧友网站提供《CDCE6214超低功率时钟发生器数据表.pdf》资料免费下载

2024-02-28 15:38:40 0

0 函数发生器和信号发生器是电子工程领域常用的两种设备,它们在实验室和工业制造领域中扮演着重要的角色。尽管两者在名称和功能上有一定的相似性,但它们的原理和应用有所不同。本文将详细探讨函数发生器和信号

2024-02-23 16:10:50 214

214 国芯思辰SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻辑设备。SYSREF

2024-02-19 09:41:40

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2024-02-04 11:41:14

小视频,波形不停地在左右抖动,并且整周期的AD采样值也会发生相位移动,我们怀疑这个相位波动是导致上层算法出现较大误差的原因,采用外部信号发生器做对比试验误差则缩小10倍。我们不清楚这个正弦发生器的内部原理,所以想请问一下,问什么会出现相位波动的情况?谢谢

2024-02-04 08:59:00

电子发烧友网站提供《毫微微时钟网络同步器、抖动衰减器和时钟发生器RC32112A 数据表.pdf》资料免费下载

2024-01-31 10:09:17 0

0 会导致晶振的输出频率出现一定的不稳定性,从而影响到系统的时钟同步和信号处理。相位抖动常常以皮克-到-皮克的相位偏移量来衡量,通常以ps级别或fs级别来表示。相位抖动在通信系统、时钟系统和高精度测量设备中都是非常重要

2024-01-25 13:51:07 126

126 RS2CG5705B是一款符合PCI Express 3.0和以太网要求的扩频时钟发生器。该电路用于PC或嵌入式系统,以显著减少电磁干扰(EMI)。RS2CG5705B提供

2024-01-25 09:41:32 0

0 RS2CG5705B是一款符合PCI Express 3.0和以太网要求的扩频时钟发生器。该电路用于PC或嵌入式系统,以显著减少电磁干扰(EMI)。RS2CG5705B提供4对差分(HCSL)或

2024-01-24 17:31:16

波特率发生器是一种用于控制串行数据通信速率的设备,它可以生成特定波特率的时钟信号。在嵌入式系统、通信设备和计算机硬件中,波特率发生器的使用十分常见。波特率发生器通常使用定时器来实现时钟信号的生成

2024-01-24 09:56:20 265

265 产品介绍:斯坦福数字延迟发生器DG535美国SRS/DG535 4通道数字延迟/脉冲发生器详细说明规格时滞频道四个独立的延迟输出范围0到999.999,999,999,995秒分辨率5 PS精度

2024-01-20 15:15:32

信号发生器是一种电子测试仪器,用于产生各种类型的电信号。它可以在实验室、工厂和其他领域提供标准化的、可重复的信号,用于测试和验证其他电子设备的性能。信号发生器的使用方法有很多种,下面将详细介绍

2024-01-19 14:51:02 402

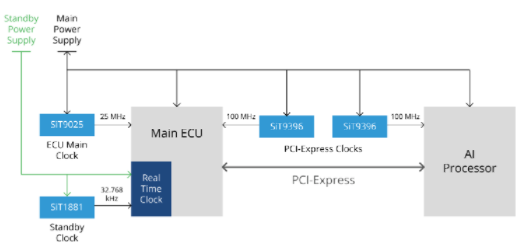

402 核芯互联近日发布了一款专为高性能服务器和计算中心应用打造的支持PCIe 6.0的高性能时钟发生器——CLG440。这款产品符合CK440Q标准,旨在满足下一代服务器和数据中心的需求。

2024-01-16 16:09:07 445

445 “核芯互联CLG440是一颗专为高性能服务器、计算中心应用推出的支持PCIe 6.0、符合CK440Q标准的高性能时钟发生器。

2024-01-16 15:57:40 279

279

电子发烧友网站提供《FemtoClock2抖动衰减器和时钟发生器RC325008A数据手册.pdf》资料免费下载

2024-01-14 10:55:06 0

0 时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2023-12-29 09:29:50

时钟缓冲器芯片时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能。可输出差分

2023-12-28 13:46:09

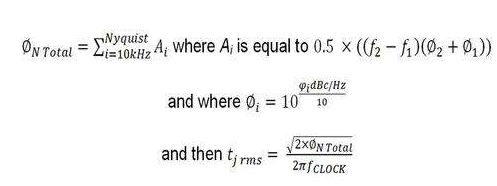

100fs-300fs之间?

疑问3:是不是使用PLL类型的时钟发生器芯片带来的抖动误差会比较大?针对14位的ADC输入差分时钟有此类型的参考吗?

模拟输入部分:

疑问1:参考文档中使用AD8138差分驱动芯片

2023-12-22 08:19:31

原本打算使用FPGA的PLL输出端口得到AD的输入时钟,但发现FPGA的时钟输出jitter过大(600ps),远大于得到优秀SNR所需的抖动水平

如图为AD9233的推荐的时钟输入方法

2023-12-22 06:29:38

信号发生器的特点 信号发生器可以产生哪些波形? 信号发生器是一种用于产生各种频率、振幅和波形的电信号的设备。它是电子测试仪器中常用的一种,广泛应用于科研、生产和教学等领域。信号发生器具有以下几个特点

2023-12-21 15:05:42 503

503 信号发生器如何发出双脉冲? 信号发生器是一种用于产生各种信号波形的仪器。双脉冲信号是一种特殊的信号波形,由两个脉冲组成,通常用于测试和测量系统的响应和性能。在本文中,将详细介绍信号发生器如何发出

2023-12-21 15:03:35 442

442 信号发生器的占空比是什么 信号发生器占空比怎么设置 信号发生器的占空比是指方波波形中高电平和低电平的时间比例。它是描述信号发生器输出方波的高低电平持续时间的一个重要参数。在数字电子技术和通信系统

2023-12-21 14:02:26 982

982 直流高压发生器的原理 直流高压发生器的使用方法 直流高压发生器有自动保护吗 直流高压发生器是一种能够产生高电压直流输出的设备。其原理是基于电子器件的整流和倍压原理。下面将详细介绍直流高压发生器

2023-12-20 15:01:33 508

508 AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2023-12-12 14:25:17

83650BAgilent 83650B信号发生器,HP-83650B 50G信号发生器|10MHz至50GHz美国安捷伦Agilent 惠普HP产品规格 提供+20dbm

2023-12-11 11:00:38

Agilent安捷伦E4432B ESG-D系列数字 RF 信号发生器, 3 GHz带宽。安捷伦E4432B信号发生器/Agilent E4432B特点250 kHz 至 3 GHz 频率范围RF

2023-12-07 14:39:09

的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。...

2023-11-28 14:33:57 0

0 电子发烧友网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

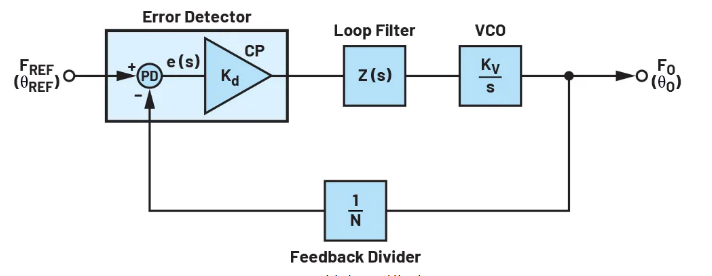

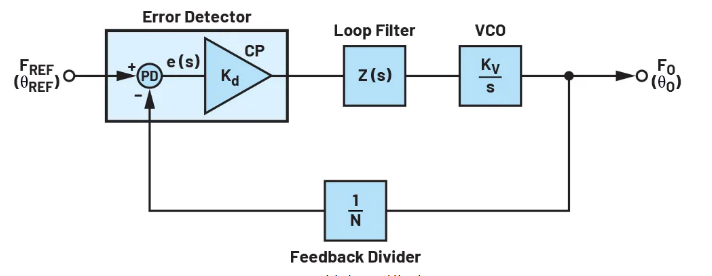

1 RF信号发生器,尤其是微波频率的RF信号发生器,是基于锁相环(PLL)合成器产生的。[1]PLL允许从低频参考产生稳定的高频。图1给出了一个基本的PLL模型。该模型由一个反馈系统组成,该系统由一个改变输出频率的压控振荡器、一个比较输入参考频率和输出频率的误差检测器以及分频器组成。

2023-11-23 15:52:52 292

292

静电放电发生器原理 静电放电发生器的主要用途 静电发生器怎么使用 静电放电发生器(Electrostatic Discharge Generator)是一种用于模拟和测试电子器件和系统在静电放电

2023-11-23 10:07:22 664

664 81110A81110A 脉冲/码型发生器|Agilent|安捷伦脉冲信号发生器|165MHz安捷伦 | Agilent | 惠普 | HP与外部时钟同步(固定和可变延迟)2ns可变跃变时间,在50

2023-11-16 18:00:00

时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56 298

298 时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

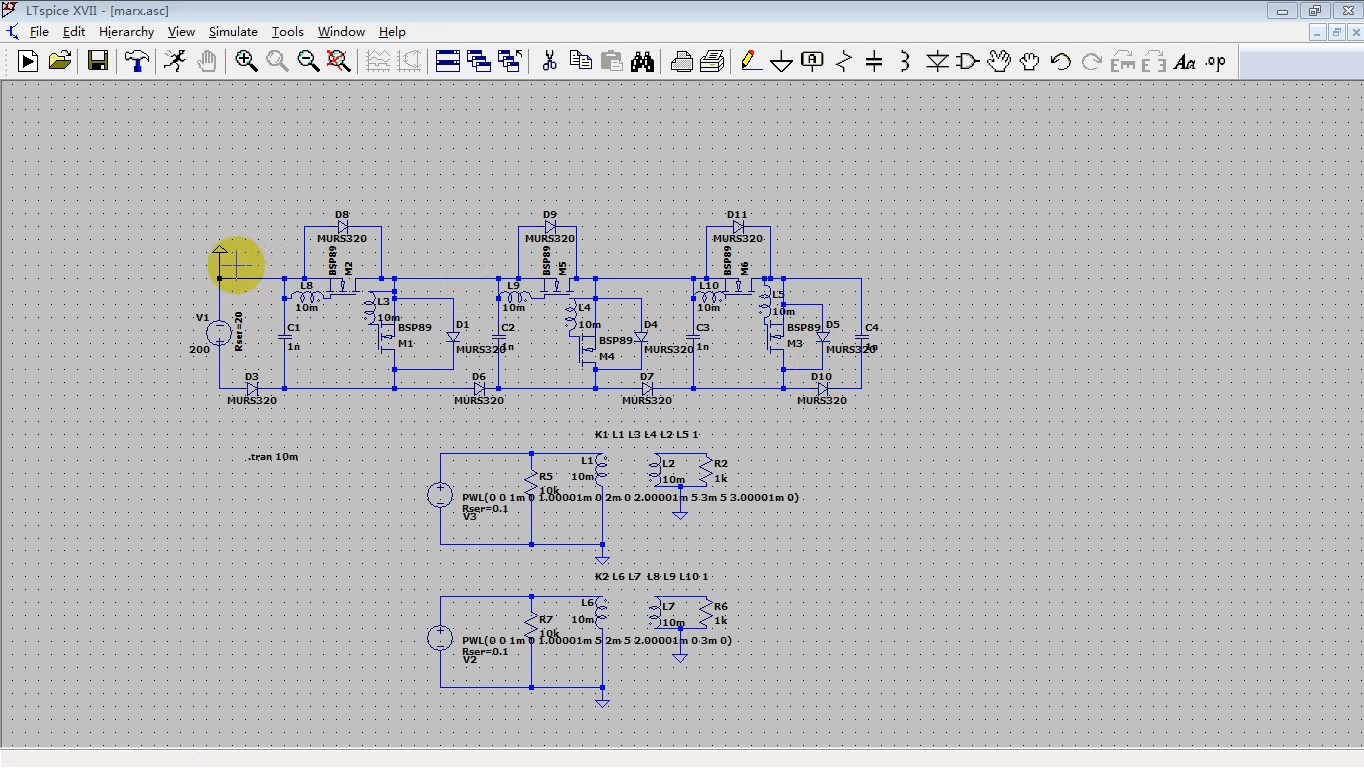

本应用笔记详细介绍了具有外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL (MAX2880)、基于运算放大器的有源环路滤波器(MAX

2023-10-28 14:45:41 6895

6895 ;SI5338Q-B-GMSi5338是一款高性能、低抖动的时钟发生器,能够在设备的四个输出驱动器中的每一个上合成任何频率。这个时间IC能够更换多达四个不同频率的

2023-10-17 17:02:33

时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 443

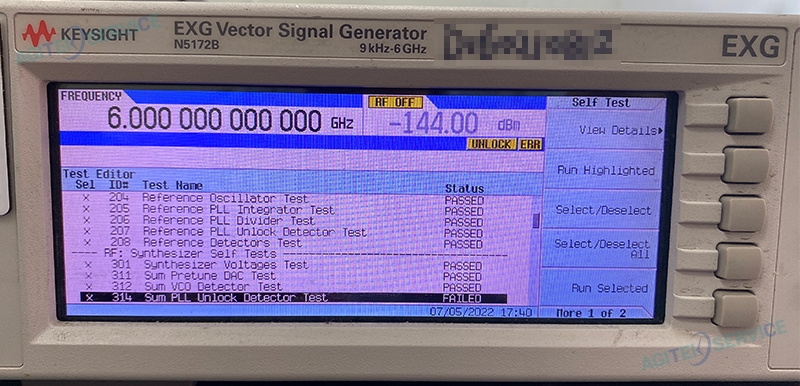

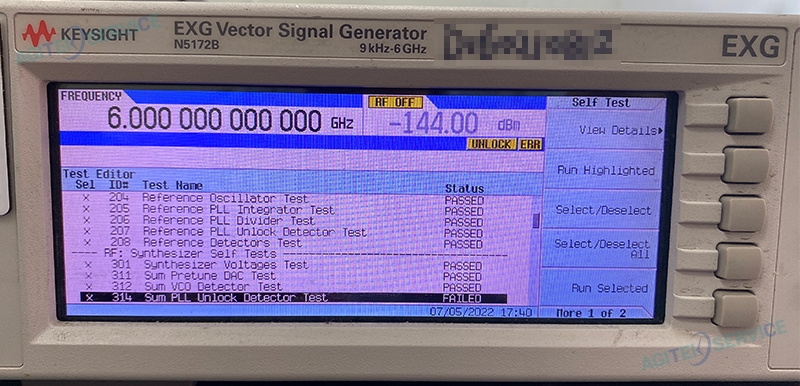

443 维修情况 安捷伦信号发生器 N5172BMP1报钉头反接维修 一、信号发生器 维修型号:安捷伦-N5172B。 二、报修故障:MP1报钉头反接。 三、故障检测:700MHz以下信号抖动。经过工程师拆机检测,对内部元件进行详细检测,发现仪器射频板损坏。 四、维修措施:更换射

2023-10-10 17:07:36 492

492

81110A81110A 脉冲/码型发生器|Agilent|安捷伦脉冲信号发生器|165MHz安捷伦 | Agilent | 惠普 | HP与外部时钟同步(固定和可变延迟)2ns可变跃变时间,在50

2023-09-25 10:32:47

早期制作的电视信号发生器基本上是由分频器和门电路构成 ,所用元器件较多、电路复杂 ,自制起来相当麻烦 ,要想增加显示图像的种类或改变信号的时序就更困难了。高速单片机的出现给信号发生器的设计制作带来

2023-09-19 07:27:23

时钟发生器IC 200MHz 2 MSOP10_3X3MM

2023-09-18 15:10:50

时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 502

502

用FPGA的锁相环PLL给外围芯片提供时钟 FPGA锁相环PLL(Phase-Locked Loop)是一种广泛使用的时钟管理电路,可以对输入时钟信号进行精确控制和提高稳定性,以满足各种应用场

2023-09-02 15:12:34 1319

1319 风冷雕刻电主轴发生抖动的原因?|深圳恒兴隆机电

2023-08-28 11:24:23 325

325

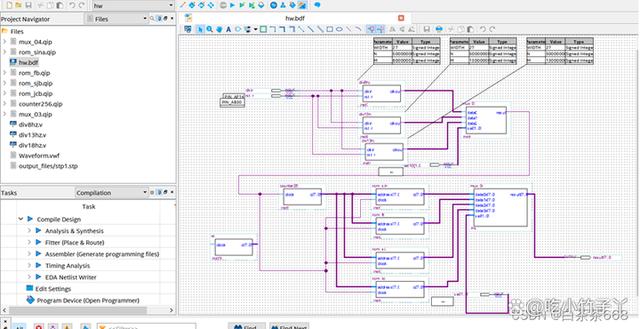

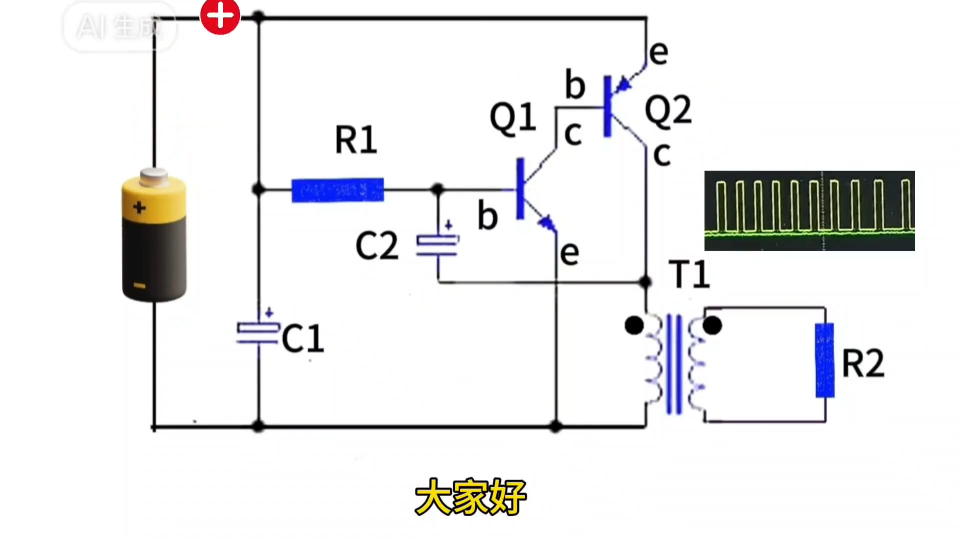

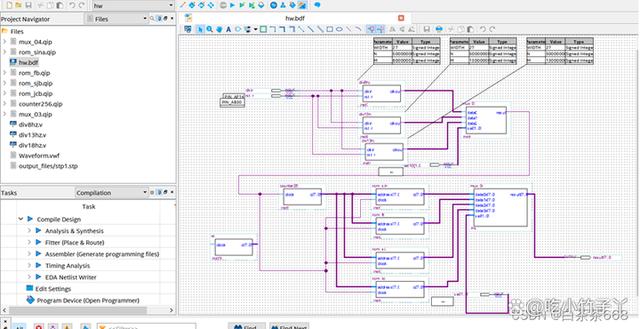

多功能信号发生器的原理框图如图所示。其中,CLKGEN是分频器,提供的50MHz的主频率进行分频,以得到满足多功能信号发生器设计需要的时钟频率。

2023-08-25 16:34:51 1291

1291

,在很多应用场景中都可以用来构建序列发生器。本文将介绍使用D触发器设计序列发生器的方法和步骤。 首先,我们需要了解D触发器的基本原理和性质。D触发器是一种时序电路,它可以存储和延迟一个输入信号,并在时钟信号到来时输出

2023-08-24 15:50:17 2728

2728 简易信号发生器的设计 信号发生器是一种能够产生可靠、标准化的交替电流、交流电压和脉冲的电子设备。在电子测试和测量、频率标准校准等领域中,信号发生器都是不可或缺的仪器。然而,通常市面上的信号发生器

2023-08-24 15:49:50 1159

1159 脉冲发生器是什么意思?脉冲发生器怎么使用? 脉冲发生器是一种电子设备,可以生成不同类型的脉冲信号。这些信号可以被用于各种测试、测量和控制应用,包括电子、通信、无线电、雷达、医疗等领域。它通常由多个

2023-08-24 15:18:09 2127

2127 脉冲发生器输出是1吗?信号发生器怎么只发一个脉冲? 脉冲发生器和信号发生器是常用的电子测量仪器,用于产生脉冲和不同类型的信号。在实际应用中,人们通常会误解它们的作用和输出特性,因此需要进行详细的解释

2023-08-24 15:18:06 882

882 信号发生器系列波形发生器你知道多少?虹科信号发生器系列波形发生器:波形发生器是用于产生各种形状和频率电信号波形的电子测量仪器。根据用户配置,可以输出不同频率、振幅、相位和波形的信号。波形发生器既可以

2023-08-05 08:07:41 1817

1817

型 号:33522B名 称:波形发生器,30 MHz,2 通道,具有任意波形生成能力品 牌:是徳(KEYSIGHT)分 类:通用电子测试 > 信号

2023-08-04 16:38:50

电子发烧友网为你提供Maxim(Maxim)MAX3625BEUG+T相关产品参数、数据手册,更有MAX3625BEUG+T的引脚图、接线图、封装手册、中文资料、英文资料,MAX3625BEUG+T真值表,MAX3625BEUG+T管脚等资料,希望可以帮助到广大的电子工程师们。

2023-07-28 18:45:33

电子发烧友网为你提供Maxim(Maxim)MAX3625BEUG+相关产品参数、数据手册,更有MAX3625BEUG+的引脚图、接线图、封装手册、中文资料、英文资料,MAX3625BEUG+真值表,MAX3625BEUG+管脚等资料,希望可以帮助到广大的电子工程师们。

2023-07-28 18:45:18

产品概况: SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7

2023-07-25 17:06:53

需要。将波形发生器产生的信号注入到设备中,以便在测试期间进行分析、发现设备问题或确认正常运行。 4.2 GS/s 采样率模拟高达 2.1 GHz 的真实信号 2 个 2.0 ps 的标记;RMS

2023-07-12 14:24:57 235

235

需要。将波形发生器产生的信号注入到设备中,以便在测试期间进行分析、发现设备问题或确认正常运行。 附加的功能: 一个通道,10 位垂直分辨率 外部时钟输入允许抖动插入和同步 10 通道、1 GHz 数字数据生成(选项 03) 实时噪声生成 支持直接外部时钟和 10 MHz 参考

2023-07-12 11:28:49 248

248

9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-07-07 19:19:11 0

0 本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 959

959

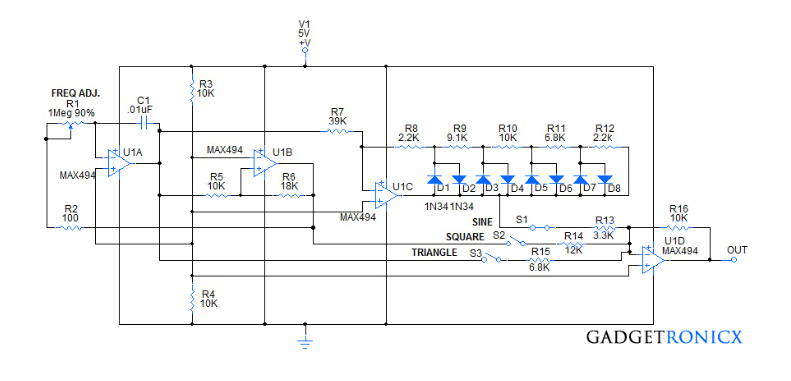

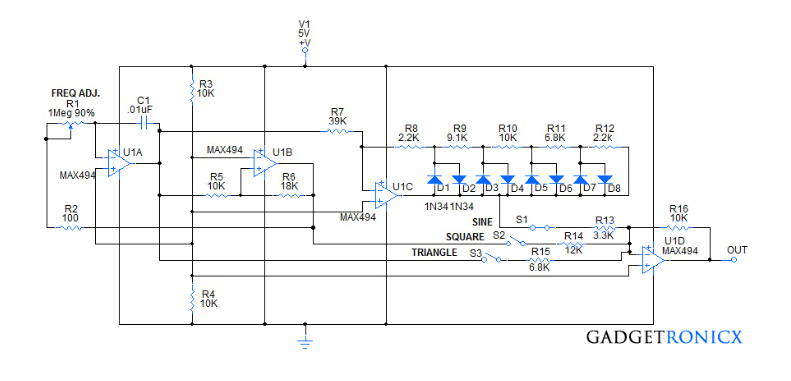

函数发生器(又名FG)在许多音频和模拟电路中广泛使用。FG能够生成正弦波、方波、锯齿波和三角波。但是,没有多少电子爱好者能够负担得起购买FG用于实验目的。对于那些想要自己构建简单具有成本效益的函数发生器的人来说,这种函数发生器电路将派上用场。

2023-07-02 10:41:56 420

420

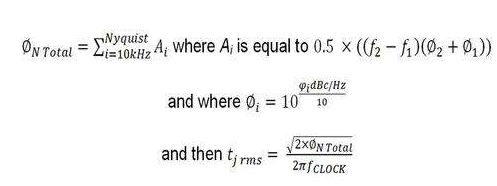

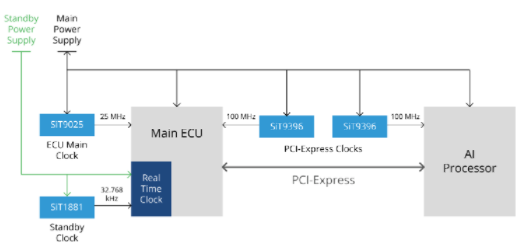

在本例中,我们将研究如何利用低抖动时钟发生器AD9643对双通道14位250 MSPS ADC进行计时。使用这些特定产品的常见时钟频率为9523.245 MHz,因此我们将为AD76使用30.72 MHz基准电压源(外部振荡器),并设置内部寄存器,为AD9523生成低抖动时钟输出。

2023-06-30 16:59:52 798

798

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 1121

1121

安捷伦33621A任意波形发生器 33621A 是安捷伦的任意波形发生器。任意波形发生器 (AWG) 是人们用来生成重复或单次电波形的一种电子测试设备。单次波形需要内部或外部触发源,而重复波形

2023-06-06 15:21:29 648

648

首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 1024

1024

) 以及其他通常要求时域抖动规范(如周期)的应用生成时钟- 周期和周期抖动。 然而,对于串行解串器 (SerDes)、千兆以太网 (GbE)、10 GbE、同步光网络/同步数字体系 (SONET/SDH) 和光纤通道等高速接口,情况就不同了。有严格的频域抖动要求。 为了正常运行,这些高速接口依赖于低频

2023-05-26 22:15:02 1385

1385 无源谐振器和有源振荡器是众所周知的定时元件。更复杂的组件包括时钟发生器、同步器和抖动衰减器。汽车系统中时序的主要目的是为每个数字集成电路提供稳定的参考,同步大量数据的传输,并实现V2X和5G通信。

2023-05-04 11:42:28 1025

1025

CLG5908是一颗高性能的任意频率任意输出格式通用时钟发生器,可以支持1~750M任意频点输出,频率精度 < 0.001 PPM,并且jitter性能优越,通常模式下RMS jitter<200fs,同时支持Down-Spread和Center-Spread SSC。

2023-04-23 14:43:12 626

626

) 频带内和频带外 (VCO) 噪声的影响。基准时钟发生器的相位噪声性能需要在PLL环路带宽内和带宽外都表现得很出色,以符合更加严格的抖动技术规格要求。

2023-04-17 10:37:30 357

357

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 810

810

时钟发生器/PLL频率合成器 VQFN32_5X5MM_EP 3V~3.6V 683.28MHz

2023-04-06 12:10:37

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1633

1633 斯坦福SRS DG535 延迟发生器脉冲发生器产品介绍:斯坦福数字延迟发生器DG535美国SRS/DG535 4通道数字延迟/脉冲发生器详细说明规格时滞频道四个独立的延迟输出范围0到

2023-04-03 17:54:44

利用运算放大器构成的脉冲序列发生器和积分器构成三角波发生器。可是我怎么将匹配器件的参数,调出三角波的波形呢。现在怎么调都 没法弄在线性工作区。。。。

2023-03-31 13:53:44

KIT EVALUATION MAX MAX3625B

2023-03-30 11:46:01

12 LVPECL/24 CMOS输出时钟发生器,集成2 GHz VCO

2023-03-28 18:26:07

CDCM61002 1:2 超低抖动晶体时钟发生器

2023-03-28 18:26:06

时钟发生器/PLL频率合成器 QFN24_4X4MM_EP 3~5.2V 8GHz

2023-03-28 18:26:06

14输出时钟发生器,集成2.0 GHz VCO

2023-03-28 18:12:38

时钟发生器 MSOP10 3~3.6V

2023-03-28 12:54:08

嘿,不幸的是,我必须为我的应用程序使用 LVPECL 时钟发生器,并且我试图弄清楚如何最好地将其转换为 DIFF_SYSCLK/DIFF_SYSCLK_B 输入的 LVDS 电平,这让我有些困惑。在

2023-03-27 08:00:13

时钟发生器/PLL频率合成器 QFN-24 2.7~5.5V 8GHz 1:1 CMOS CMOS

2023-03-23 05:01:32

结合时钟发生器输出和FTDICHIP-ID TM安全加密狗

2023-03-23 04:59:11

电子发烧友App

电子发烧友App

评论