泰科电子推出DDR3双列直插式內存模组(DIMM)插槽

- DDR3(41693)

- DI(33066)

- 內存(7359)

相关推荐

金航标和萨科微

在不断的增长。金航标kinghelm(www.kinghelm.net)一直在向国外连接器巨头安费诺、泰科TE、莫仕Molex、广濑、立讯精密、富士康(鸿海)、Yazaki、JAE和国内的贵州航天

2024-03-18 11:39:25

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?

2021 年,JEDEC 宣布发布 JESD79-5 DDR5 SDRAM 标准,标志着行业向 DDR5 dual-inline memory modules (DIMM) 的过渡。

2024-03-17 09:50:37 429

429

429

429

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

电子发烧友网站提供《完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表.pdf》资料免费下载

2024-03-13 13:58:12 0

0

0

0适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表

电子发烧友网站提供《适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表.pdf》资料免费下载

2024-03-13 13:53:03 0

0

0

0具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表

电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:24:34 0

0

0

0具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表

电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表.pdf》资料免费下载

2024-03-13 11:13:44 0

0

0

0完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

电子发烧友网站提供《完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表.pdf》资料免费下载

2024-03-13 10:16:45 0

0

0

0agp和pcie插槽区别 agp插槽插的组件是什么

,并详细描述AGP插槽的组件。 首先,AGP和PCIe插槽的区别包括设计架构、传输速度和功能性。 设计架构 AGP插槽是Intel推出的一种专门用于连接显卡的接口,通过直接连接图形单元和主板内存,提供

2024-01-24 10:32:53 481

481

481

481使用SC584外扩DDR3,程序均在adi_gic_GetIntSecurityStatus函数出现异常的原因?

使用SC584外扩DDR3,no_boot启动模式,开发环境CCES-2.2.0版本,在线调试过程,程序可正常下载,但是在A5预加载过程中会出现SYS_FAULT拉高现象,经实际汇编单步调试发现

2024-01-12 08:11:46

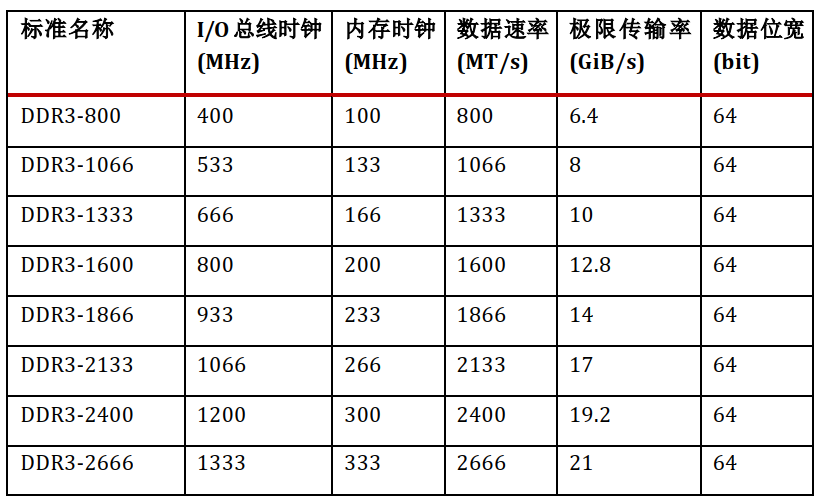

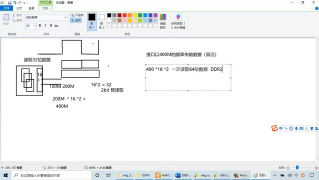

DDR1/2/3数据预取技术原理详解

时钟频率:可通过倍频技术升级的核心频率。时钟频率可以理解为IO Buffer的实际工作频率,DDR2中时钟频率为核心频率的2倍,DDR3 DDR4中时钟频率为核心频率的4倍。

2023-12-25 18:18:47 1188

1188

1188

1188

DDR3存储厂迎涨价商机 华邦、钰创、晶豪科等订单涌进

法人方面解释说:“标准型dram和nand目前由三星、sk hynix、美光等跨国企业主导,因此,中台湾企业在半导体制造方面无法与之抗衡。”在ddr3 ddr3的情况下,台湾制造企业表现出强势。ddr3的价格也随之上涨,给台湾半导体企业带来了很大的帮助。

2023-11-14 11:29:36 405

405

405

405DDR4和DDR3内存都有哪些区别?

DDR4和DDR3内存都有哪些区别? 随着计算机的日益发展,内存也越来越重要。DDR3和DDR4是两种用于计算机内存的标准。随着DDR4内存的逐渐普及,更多的人开始对两者有了更多的关注。 DDR3

2023-10-30 09:22:00 3885

3885

3885

3885阐述DDR3读写分离的方法

DDR3是2007年推出的,预计2022年DDR3的市场份额将降至8%或以下。但原理都是一样的,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。

2023-10-18 16:03:56 516

516

516

516

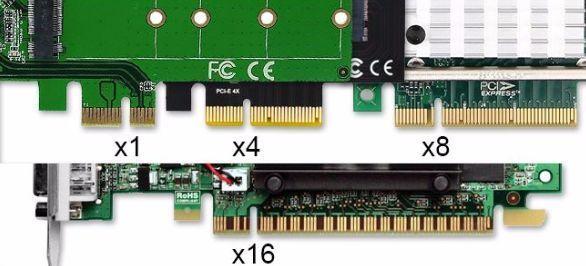

如何选择合适的插槽?PCIe插槽的规格有哪些?

数据交换,大大提高了传输效率。在新一代硬件中,PCIe插槽的应用更是广泛,成为了很多设备的首选连接方式。如何选择合适的插槽?PCIe插槽的规格有哪些?所有主板的PCI扩展插槽都是一样的吗?下面就随苏州研讯电子科技有限公司一起来看看吧。 研华工控机 PCIe插

2023-09-28 10:55:48 1173

1173

1173

1173

DDR3和DDR4的技术特性对比

摘要:本文将对DDR3和DDR4两种内存技术进行详细的比较,分析它们的技术特性、性能差异以及适用场景。通过对比这两种内存技术,为读者在购买和使用内存产品时提供参考依据。

2023-09-27 17:42:10 1088

1088

1088

1088【紫光同创PGL50H】小眼睛科技盘古50K开发板试用体验之测测DDR3

时,就需要外扩DDR SRAM二级存储来满足需求。

本期的主角盘古PGL50H FPGA就贴心的在核心板上,为我们配备了两片DDR3的芯片,来完成二级存储的需求。

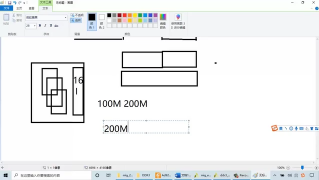

两片DDR3组成32bit的总线数据

2023-09-21 23:37:30

DDR4与DDR3的不同之处 DDR4设计与仿真案例

相对于DDR3, DDR4首先在外表上就有一些变化,比如DDR4将内存下部设计为中间稍微突出,边缘变矮的形状,在中央的高点和两端的低点以平滑曲线过渡,这样的设计可以保证金手指和内存插槽有足够的接触面

2023-09-19 14:49:44 1478

1478

1478

1478

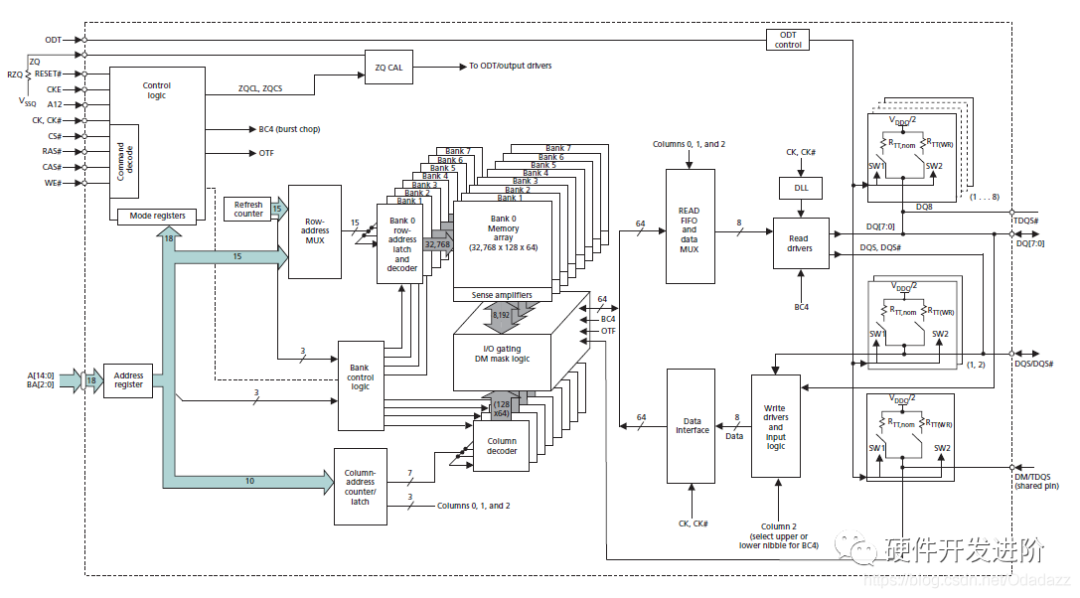

DDR3的规格书解读

以MT41J128M型号为举例:128Mbit=16Mbit*8banks 该DDR是个8bit的DDR3,每个bank的大小为16Mbit,一共有8个bank。

2023-09-15 15:30:09 629

629

629

629

为什么DDR3/4不需要设置input delay呢?

内置校准: DDR3和DDR4控制器通常具有内置的校准机制,如ODT (On-Die Termination)、ZQ校准和DLL (Delay Locked Loop)。这些机制可以自动调整驱动和接收电路的特性,以优化信号完整性和时序。

2023-09-11 09:14:34 420

420

420

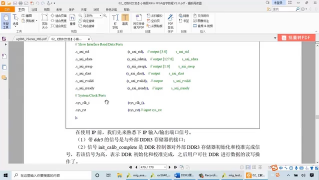

420基于AXI总线的DDR3读写测试

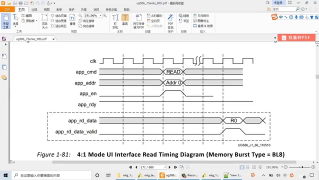

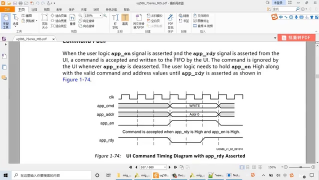

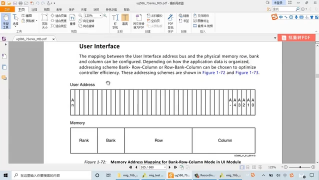

本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

2023-09-01 16:20:37 1887

1887

1887

1887

关于MCU200T的DDR3的配置和原理图的问题

MCU200T的DDR3在官方给的如下图两份文件中都没有详细的介绍。

在introduction文件中只有简略的如下图的一句话的介绍

在schematic文件中也没有明确表明每个接口的具体信息

2023-08-17 07:37:34

从里可以找到DDR200T的DDR3的配置和约束文件?

在配置DDR200T的DDR3时,一些关键参数的选择在手册中并没有给出,以及.ucf引脚约束文件也没有提供,请问这些信息应该从哪里得到?

2023-08-16 07:02:57

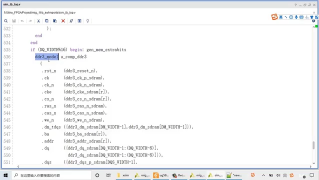

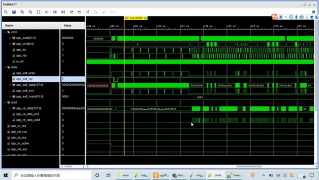

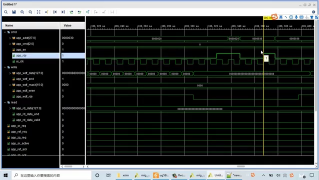

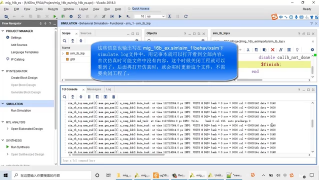

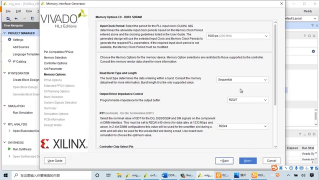

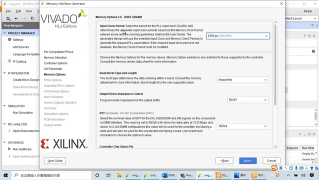

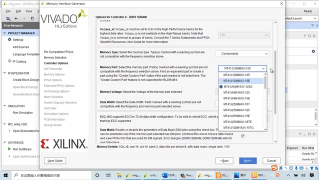

DDR3缓存模块仿真平台构建步骤

复制Vivado工程路径vivado_prj\at7.srcs\sources_1\ip\mig_7series_0下的mig_7series_0文件夹。粘贴到仿真路径testbench\tb_ddr3_cache(新建用于DDR3仿真的文件夹)下。

2023-08-12 11:08:27 735

735

735

735ARM Mps3 FPGA原型板入门指南

Arm MPS3 FPGA原型板配有SO-DIMM存储模块。该模块未在工厂安装,以减少其在运输过程中损坏的可能性。要安装内存模块,首先将其以一定角度滑入插槽(如图2所示),使模块边缘连接器中的插槽

2023-08-10 07:10:30

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR5

DDR5的主板不支持使用DDR4内存。DDR5(第五代双倍数据率)和DDR4(第四代双倍数据率)是两种不同规格的内存技术,它们在电气特性和引脚布局上存在明显差异。因此,DDR5内存模块无法插入DDR4主板插槽中,也不兼容DDR4内存控制器。

2023-08-09 15:36:25 12792

12792

12792

12792PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用

电子发烧友网站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用.pdf》资料免费下载

2023-07-24 09:50:47 0

0

0

0DDR、DDR2、DDR3、DDR4、LPDDR的区别

DDR是Double Data Rate的缩写,即“双倍速率同步动态随机存储器”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台湾以及欧美,工程师习惯用DRAM来称呼。

2023-07-16 15:27:10 3362

3362

3362

3362

新品发布 | 瑞萨电子推出业界首款客户端时钟驱动器CKD和第3代RCD,以支持严苛的DDR5客户端与服务器DIMMs应用

新品速递 全球半导体解决方案供应商瑞萨电子(TSE:6723)宣布面向新兴的DDR5 DRAM服务器和客户端系统推出客户端时钟驱动器(CKD)和第三代DDR5寄存时钟驱动器(RCD)。凭借这些全新

2023-06-29 18:15:03 359

359

359

359从零开始学习紫光同创FPGA——PGL22G开发板之DDR3 IP简单读写测试(六)

1.DDR3 IP简单读写测试实验例程

1.1** 实验目的**

MES22GP 开发板上有一片 Micron 的 DDR3(MT41K256M16 TW107:P)内存组件,拥有 16bit 位宽

2023-06-25 17:10:00

基于FPGA的DDR3多端口读写存储管理系统设计

视频图形显示系统理想的架构选择。视频处理和图形生成需要存储海量数据,FPGA内部的存储资源无法满足存储需求,因此需要配置外部存储器。 与DDR2 SDRAM相比,DDR3 SDRAM带宽更好高、传输速率更快且更省电,能够满足吞吐量大、功耗低的需求,因此

2023-06-08 03:35:01 1024

1024

1024

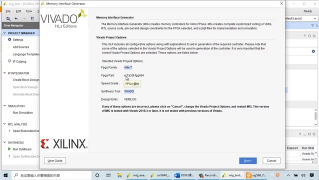

1024紫光同创FPGA入门指导:DDR3 读写——紫光盘古系列50K开发板实验教程

一、实验要求

生成 DDR3 IP 官方例程,实现 DDR3 的读写控制,了解其工作原理和用户接口。

二、DDR3 控制器简介

PGL50H 为用户提供一套完整的 DDR memory 控制器

2023-05-31 17:45:39

使用带有ECC芯片的4GB DDR3 RAM连接到T1040处理器DDR控制器,未能成功生成DDR地址奇偶校验错误的原因?

我正在使用带有 ECC 芯片的 4GB DDR3 RAM 连接到 T1040 处理器 DDR 控制器。

我尝试了这个序列,但未能成功生成 DDR 地址奇偶校验错误:

步骤1:

ERR_INT_EN

2023-05-31 06:13:03

紫光同创FPGA入门指导:DDR3 读写——紫光盘古系列50K开发板实验教程

MES50HP 开发板简介

MES50HP 开发板集成两颗 4Gbit(512MB)DDR3 芯片,型号为 MT41K256M16。DDR3 的总线宽度共为 32bit。DDR3 SDRAM 的最高

2023-05-19 14:28:45

千呼万唤始出来的DDR5 DIMM插槽连接器,买它!

发展。为了更好地助力数据传输的带宽,DDR5 DIMM插槽应运而生。 早先这款升级产品即将面世消息一出,我们收到了非常多客户询问,好消息是, 现在DDR5 DIMM插槽已全面开放订购 !大家可以即刻下单,先人一步畅享更快的数据传输体验。 TE的DDR DIMM插槽连接器从第一代发展至今,每次升级都能

2023-05-06 17:33:42 1392

1392

1392

1392

深圳泰科智能机械臂RJS14机器人关节模组

泰科关节机器人具备哪些优势? 一、编程简单可以让无编程经验的操作人员能快速设置和操作我们的直观、3D 可视化协作式机器人。只需将机器人手臂移动至需要的位置,或触摸方便易用的触屏

2023-04-19 15:13:28

深圳泰科智能RJSII系列机器人关节模组

RJS-II系列关节模组是泰科智能推出的一款基于模块化理念设计、轻巧、高精度的协作机器人关节,一体化集成的RJS-II不仅结构尺寸更小,性价比更高,为您解决机器人在更多复杂环境中的适应性和稳定性

2023-04-19 14:54:26

关节型机器人-深圳泰科智能机器人

深圳泰科智能TA6系列协作机器人是泰科智能自主研发的6自由度的协作机器人,具有拖动示教、安全防碰撞等功能,可以直接与人协同工作。 采用自主设计的RJS系列关节模组,既轻便灵活、运行平滑柔顺,同时满足

2023-04-19 11:14:26

深圳泰科智能机械臂 TB6系列六轴桌面协作机器人

深圳泰科智能TB6系列协作机器人是泰科智能自主研发的6轴轻型协作机器人,具有拖动示教、安全防碰撞等功能,可以直接与人协同工作。采用自主设计研发RJSII系列关节模组,既轻便灵活、运行平滑柔顺,同时

2023-04-19 10:05:39

工业协作机器人-深圳泰科智能机器人

深圳泰科智能TB6系列协作机器人是泰科智能自主研发的6轴轻型协作机器人,具有拖动示教、安全防碰撞等功能,可以直接与人协同工作。采用自主设计研发RJSII系列关节模组,既轻便灵活、运行平滑柔顺,同时

2023-04-17 15:31:15

柔性关节机器人-深圳泰科智能机器人

深圳泰科智能TB6系列协作机器人是泰科智能自主研发的6轴轻型协作机器人,具有拖动示教、安全防碰撞等功能,可以直接与人协同工作。采用自主设计研发RJSII系列关节模组,既轻便灵活、运行平滑柔顺,同时

2023-04-17 15:25:07

深圳泰科智能RJSII系列机器人关节模组

RJS-II系列关节模组是泰科智能推出的一款基于模块化理念设计、轻巧、高精度的协作机器人关节,一体化集成的RJS-II不仅结构尺寸更小,性价比更高,为您解决机器人在更多复杂环境中的适应性和稳定性

2023-04-17 15:07:26

DDR SDRAM与SDRAM的区别

DDR内存1代已经淡出市场,直接学习DDR3 SDRAM感觉有点跳跃;如下是DDR1、DDR2以及DDR3之间的对比。

2023-04-04 17:08:47 2867

2867

2867

2867

电子发烧友App

电子发烧友App

评论