STM32L072是低功耗MCU, 但是用内部时钟,通过锁相环倍频到主频32MHz后,执行main函数,SystemClock_Config();函数后,单片机有7mA的功耗,为啥这么大?应该怎么样

2024-03-15 06:03:28

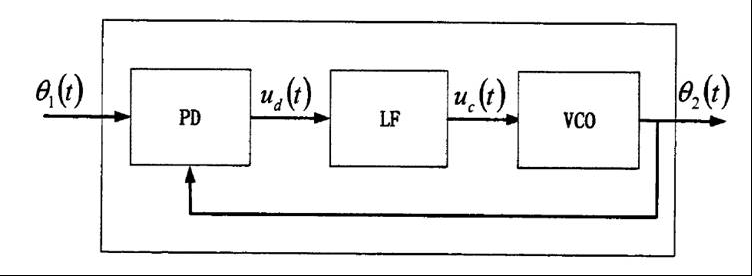

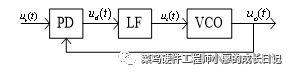

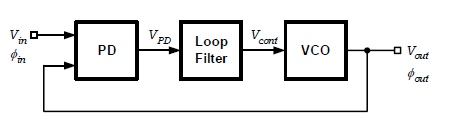

怎么有了RC滤波器,锁相环就是二阶了?传递函数明明只有一阶啊?还有一阶?是的,那一阶存在于VCO中。

2024-03-04 14:18:53 54

54

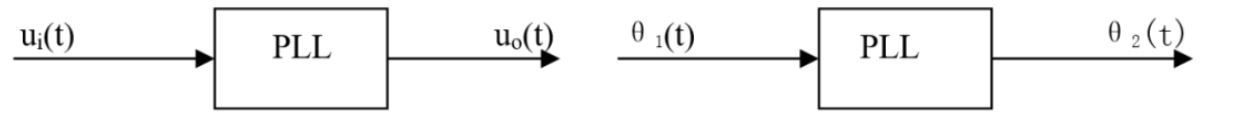

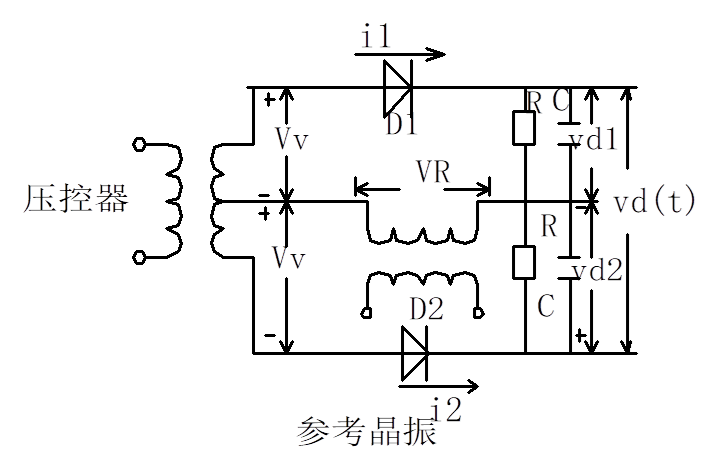

请问在电子电路中锁相环和鉴相器的电路结构是什么样的?它是如何实现此电路功能的?可否详细解释一下?

2024-02-29 22:34:45

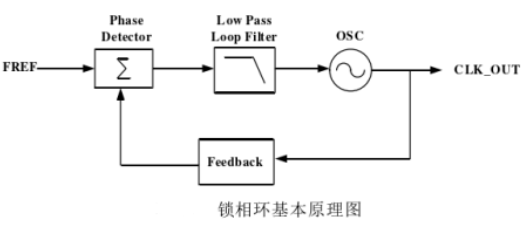

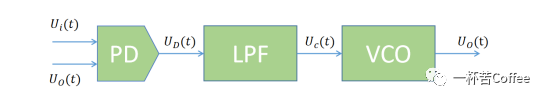

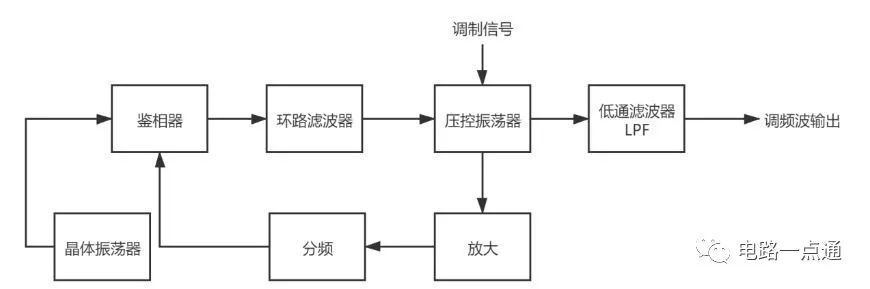

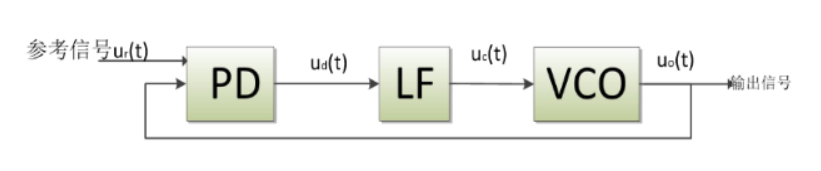

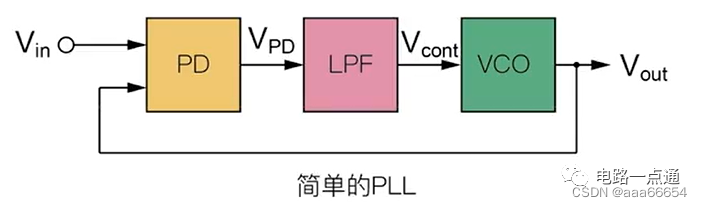

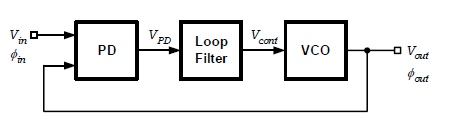

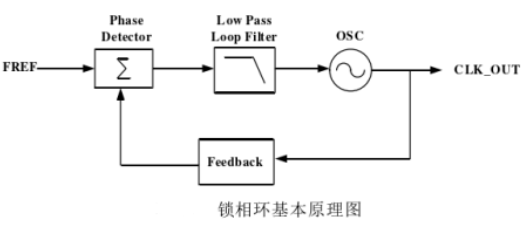

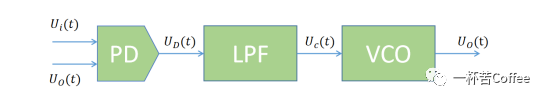

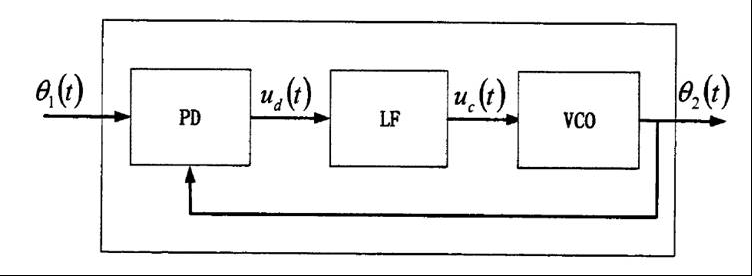

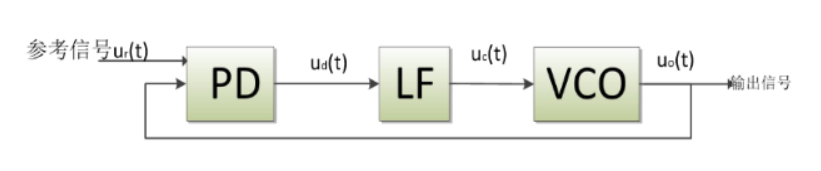

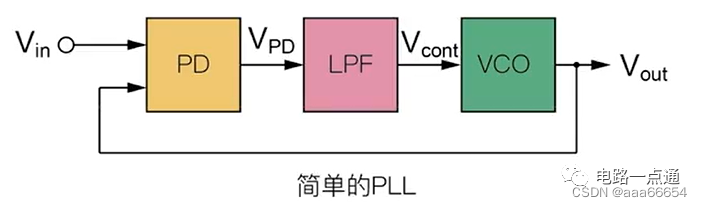

基本锁相环通常由锁相检测器(Phase Detector)、低通滤波器(Loop Filter)和令牌圈振荡器(VCO)组成。它是最简单的锁相环形式,用于频率和相位同步。

2024-01-31 16:00:55 217

217

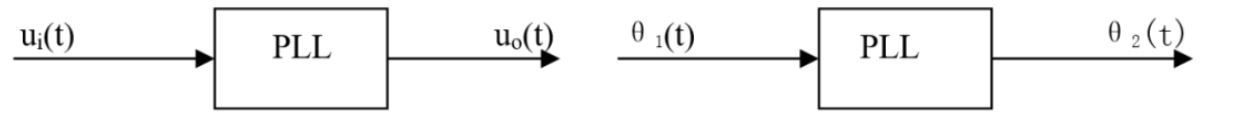

锁相环是保证相位一致,还是相位差一致?锁相环的输入输出相位一致吗? 锁相环(PLL)是一种回路控制系统,用于保持输出信号的相位与参考信号的相位之间的恒定关系。简单来说,锁相环的目的是保证相位一致

2024-01-31 15:45:48 202

202 锁相环锁定后一定不存在频差吗? 锁相环是一种常用的控制系统,用于将输入信号与参考信号之间的相位误差维持在一个可接受的范围内。它通过调节输出信号的相位和频率来实现这个目标。然而,锁相环锁定后并不能完全

2024-01-31 15:25:05 162

162 锁相环到底锁相还是锁频? 锁相环(PLL)是一种常用的控制系统,主要用于同步时钟。它通过将被控信号的相位与稳定的参考信号进行比较,并产生相应的控制信号,使被控信号的相位保持与参考信号同步。这种控制

2024-01-31 15:25:00 233

233 锁相环路与自动频率控制电路有何区别?为什么说锁相环相当于一个窄带跟踪滤波器 锁相环路(PLL)和自动频率控制电路(AFC)是常见的频率调节电路,它们的主要区别在于功能和应用场景。 首先,我们来探讨

2024-01-31 15:24:57 176

176 锁相环同步带与捕获带有区别吗? 锁相环(简称PLL)同步带和捕获带是锁相环中两个重要的工作模式,它们在功能和应用上存在一些区别。 1. 定义和原理: - 锁相环同步带:同步带是锁相环的一种工作模式

2024-01-31 11:31:47 180

180 ADF4378BCCZ是一款高性能、超低抖动、整数N 具有集成电压控制的相控阵锁相环(PLL) 理想情况下,振荡器(VCO)和系统参考(SYSREF)重定时器 适用于数据转换器和混合信号前端

2024-01-04 19:31:37

本人在使用ADF4372芯片时,运用RF16输出口,锁相环正常锁定,但是输出幅度只有-28dbm,这是为什么,请求解答谢谢。没有在VDDX1加7.4nH电感。

2024-01-03 07:39:15

数字锁相环(DigitalPhase-LockedLoop,简称DPLL)是一种基于反馈控制的技术,用于实现精确的时序控制和相位同步。通过相位比较、频率差计算、频率控制、滤波和循环控制,它能够完成

2024-01-02 17:20:25 693

693

在锁相环(PLL)中,低通滤波器通常用于滤除锁相环环路中的高频噪声,并平滑锁相环的控制信号。

2023-12-22 18:15:04 284

284 32M,在第一版的PCB上跑,AD9963的DLL输出频率就是32M,但是在第二版PCB上跑时,AD9963的输出频率有的时候自己就变成了64M,并且和32M是随机出现的。配置锁相环是根据手册上的例子配置的,求大家帮帮忙,最近项目很急。

2023-12-22 07:42:34

合成器产生输出频率的振荡器比采用非锁相环技术的振荡器一般呈现较差的相位噪声性能。例如,对于需要低噪声、稳定和精确时钟源的工业级设备(比如收发器模块或数据中心),可选择150fs小型塑封石英PLL振荡器;而

2023-12-14 09:19:08

AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2023-12-12 14:25:17

今天想来聊一下芯片设计中的一个重要macro——PLL,全称Phase lock loop,锁相环。我主要就介绍一下它是什么以及它是如何工作的。

2023-12-06 15:21:13 386

386 外部参考时钟为90MHz,需要的到一个110MHz的中频信号,因此使用AD9779内部锁相环,进行8倍插值处理。reg01配置为11001000,reg8配置为01111100,reg9配置为

2023-12-04 08:29:29

锁相环是一种 反馈系统 ,其中电压控制振荡器和相位比较器相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率或相位调制信号的频率。锁相环可用来从固定的低频信号生成稳定的输出频率信号。首批锁相环

2023-11-30 15:01:08 680

680

版主好:

现在使用AD9518-1,REF1输入频率为40M,R

divider设置为8,A=0,B=15,P=32

想用内部锁相环和VCO输出2.4G,内部锁相环已经设置为on。VCO也已经可以

2023-11-30 06:40:23

锁相环技术解析(上)

2023-11-29 16:51:25 322

322

锁相环技术解析(下)

2023-11-29 16:39:56 213

213

电子发烧友网站提供《锁相环基本结构及原理.pdf》资料免费下载

2023-11-29 11:23:37 1

1 电子发烧友网站提供《利用数字锁相环(DPLL)实现相位增建和无中断切换.pdf》资料免费下载

2023-11-24 09:36:17 0

0 有没有不需要单片机直接在外部引脚加高低电平就能输出预定信号的锁相环芯片?

2023-11-16 08:23:51

用AD8675做锁相环有源环路滤波时,出现开关机运放锁死(正向端电压1.6V左右,负向端电压0.9V左右)。运放正向端采用两个1KΩ电阻分压给偏置,负向端接电荷泵输出。运放供电15V以下,不会出现这个现象,高于20V以后,出现次数很多。什么原因????急等

2023-11-16 08:07:18

电子发烧友网站提供《基于VHDL的全数字锁相环的设计.pdf》资料免费下载

2023-11-10 09:47:34 0

0 电子发烧友网站提供《数字锁相环状态检测电路.pdf》资料免费下载

2023-11-10 09:43:18 0

0 锁相环路(Phase Locked Loop)是一个闭环的相位控制系统,它的输出信号的相位能自动跟踪输入信号相

位。

2023-11-09 15:20:46 0

0 简介:锁相环路的工作原理

§1-2 锁相环路的工作原理

锁相环路实质上是一个相差自动调节系统。为了掌握环境的工作原理,理解环 路工作过程中发生的物理现象,必须导出环路的相位

2023-11-09 15:16:24 0

0 在现代数字通信中, 数据传输中一个很重要的问题就是同步问题。而同步系统中的核心技 术就是锁相环。锁相环有模拟锁相环、模拟ö数字混合环、全数字锁相环等。前二种环路都要采 用压控振荡器V CO , 利用

2023-11-09 08:31:40 1

1 时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

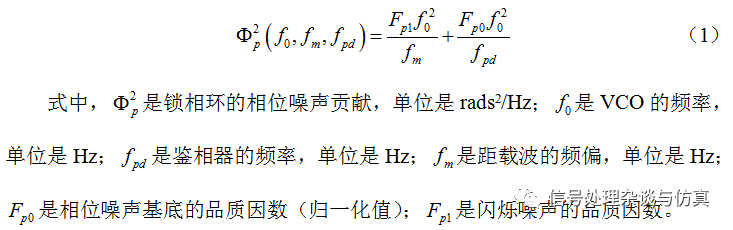

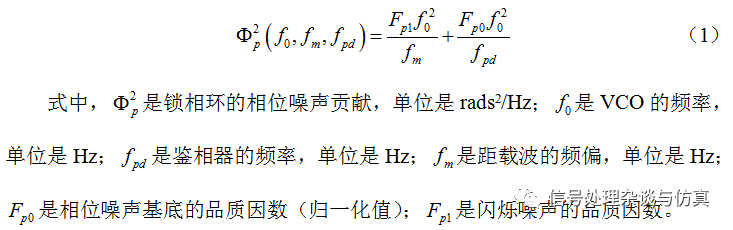

锁相环性能度量标准包括品质因数、噪声基底、闪烁噪声模型。

2023-10-31 10:36:42 377

377

为何不用一根导线代替锁相环? 锁相环(PLL)是一种广泛使用的电路,用于同步和追踪时钟和数据信号。它通常由一个锁相环振荡器(VCO)、一个相锁环(PLL)和一个数字控制器(DCO)组成。 PLL

2023-10-31 10:33:15 191

191 锁相环性能度量标准包括品质因数、噪声基底、闪烁噪声模型。

2023-10-30 17:19:51 318

318

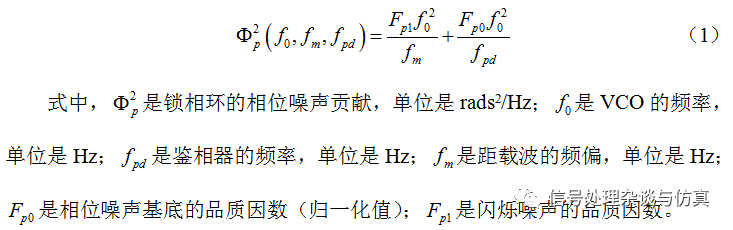

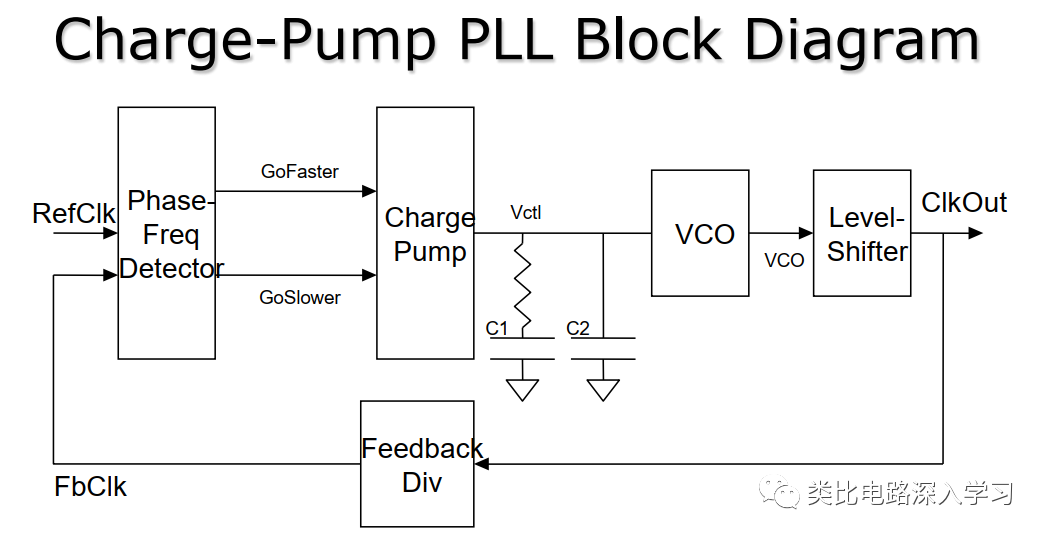

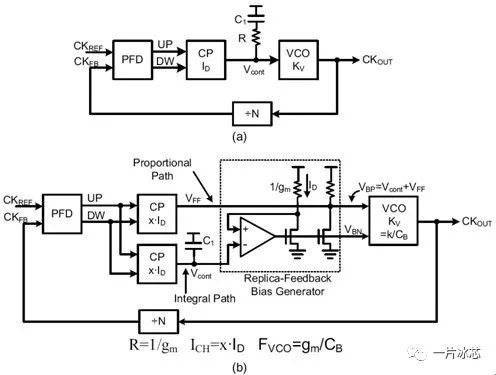

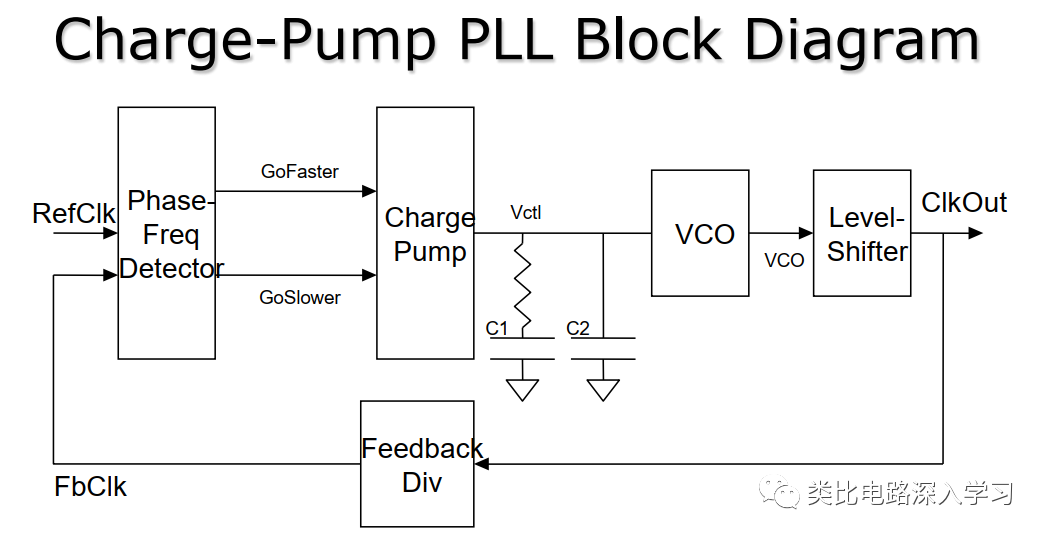

传统锁相环,环路带宽、相位裕度与电荷泵电流、滤波器RC参数、分频比、参考频率等参数相关。

2023-10-30 16:47:58 693

693

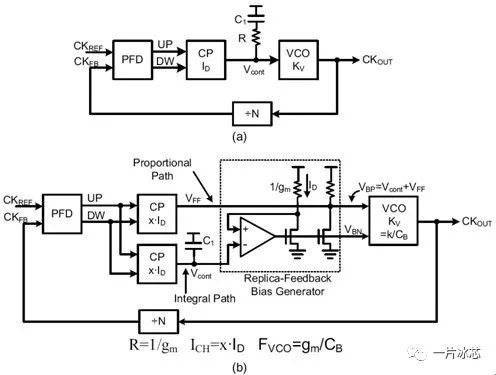

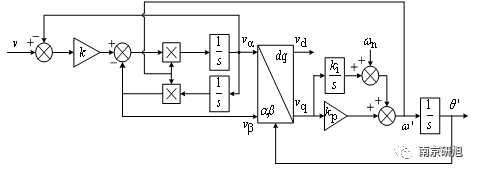

针对电网普遍存在的直流偏移和谐波干扰问题,提出一种基于二阶广义积分器锁相环(SOGI-PLL)的改进型锁相环算法。

2023-10-30 15:48:04 743

743

如何用锁相环恢复载波同步信号? 锁相环(PLL)是一种电路,可用于恢复和跟踪输入信号的频率和相位。PLL常用于电信、通讯和控制系统中,以恢复和跟踪载波同步信号。本文将介绍锁相环如何恢复载波同步信号

2023-10-30 10:56:38 356

356 载波同步电路中的锁相环设计的关键点 锁相环(Phase-Locked Loop,PLL)是一种广泛应用于通信、电视、雷达、计算机等领域的电路,可用于频率合成、频率解调、时钟生成、数字信号处理等多种

2023-10-30 10:51:28 259

259 频繁地开关锁相环芯片的电源会对锁相环有何影响? 锁相环(PLL)是一种被广泛应用在现代电子技术中的集成电路,它是一种反馈控制系统,可以将输入信号和本地参考信号同步。锁相环可用于电子时钟、数字信号处理

2023-10-30 10:16:40 267

267 当锁相环无法锁定时,该怎么处理的呢?如何解决锁相环无法锁定? 锁相环作为一种常见的电路设计,具有广泛的应用领域。然而,在一些情况下,由于种种原因,锁相环可能无法正常锁定,这时需要进行一系列的测试

2023-10-30 10:16:33 969

969 锁相环是一种能够自动跟踪输入信号相位和频率的负反馈系统,应用广泛。

2023-10-29 16:48:33 1097

1097

锁相环在相位检测中的应用 锁相环(PLL)是一种电子技术中广泛应用的电路,用于调整一个输出信号的相位来精确匹配一个参考信号。锁相环在各种不同的应用领域都有着广泛的应用,例如通信系统、控制系统、测量

2023-10-29 11:35:19 352

352 电子发烧友网站提供《锁相环在微机保护中的应用.pdf》资料免费下载

2023-10-27 11:05:35 0

0 电子发烧友网站提供《应用于数字锁相环的NCO设计.pdf》资料免费下载

2023-10-26 10:33:45 1

1 了解锁相环(PLL)瞬态响应 如何优化锁相环(PLL)的瞬态响应? 锁相环(PLL)是一种广泛应用于数字通信、计算机网络、无线传输等领域的重要电路。PLL主要用于时钟恢复、频率合成、时钟同步等领域

2023-10-23 10:10:20 869

869 锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢? 锁相环(Phase Locked Loop, PLL)是一种电路系统,它可以将输入信号的相位锁定到参考信号的相位。在锁相环中,反馈回路

2023-10-23 10:10:15 1352

1352 Altera的FPGA中,只有从专用时钟管脚(Dedicated clock)进去的信号,才能接片内锁相环(PLL)吗? 在Altera的FPGA中,专用时钟管脚是经过特殊处理的单独管脚,其用途

2023-10-13 17:40:00 297

297 软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办? 锁相环(PLL)是一种用于在电路中生成稳定频率的技术。它是在1960年代开发的,并被广泛应用于通信、雷达、卫星技术等领域中。锁相环的主要作用

2023-10-13 17:39:58 721

721 )常作为电力系统中的一种重要控制策略。三相锁相环(PLL)是一种基于锁相环原理的控制系统,它能够将输入的三相电压信号转化成可用于控制其他系统的数字信号。 三相锁相环(PLL)的作用是使得输出电压与输入电压之间保持恒定的相位差,这样可以得到一个相对稳定的输出电压。

2023-10-13 17:39:56 482

482 什么是锁相环?PLL和DLL都是锁相环区别在哪里? 锁相环(Phase Locked Loop,PLL)是一种基于反馈的控制系统,用于提供稳定的时钟信号。它可以将参考信号的相位与输出信号的相位进行

2023-10-13 17:39:53 665

665 时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 443

443 pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 1098

1098 电子发烧友网站提供《基于超前-滞后控制器的单相数字锁相环研究.pdf》资料免费下载

2023-10-09 15:01:40 0

0 关于锁相环怎么选型,1MHz以下的自动频率跟踪,应该选择哪种锁相环比较好?

2023-10-08 08:00:22

我有一个锁相环电路的pcb板和proteus仿真电路。

2023-10-04 07:58:55

锁相环(Phase Locked Loop, PLL)是一种广泛应用于通信系统、频率合成、数字信号处理等领域的关键电路。本文将介绍锁相环的基本原理、分类及应用,以期帮助读者更好地理解和掌握这一技术。

2023-09-14 17:29:12 2983

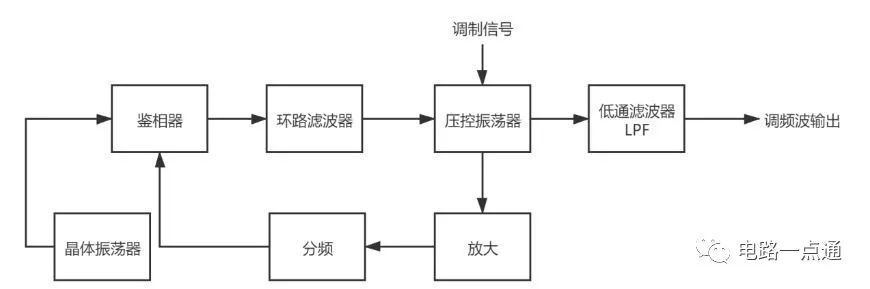

2983 最基础的锁相环系统主要包含三个基本模块:鉴相器(Phase Detector:PD)、环路滤波器(L00P Filter:LF)其实也就是低通滤波器,和压控振荡器(Voltage

2023-09-03 12:01:12 853

853

景下的时序要求。尤其对于需要高速数据传输、信号采集处理等场景的数字信号处理系统而言,FPGA PLL的应用更是至关重要。本文将介绍FPGA锁相环PLL的基本原理、设计流程、常见问题及解决方法,以及该技术在外围芯片时钟提供方面的应用实例。 一、FPGA锁相环PLL基本原理 1.时钟频率的调

2023-09-02 15:12:34 1319

1319 锁相环倍频器锁在基频怎么办? 锁相环倍频器是一种基于相位锁定原理的电子设备,它能够将输入信号的频率倍增。然而,有时候锁相环倍频器会锁在基频上,导致无法达到所要求的倍频效果。这时候,我们需要采取一些

2023-09-02 15:12:31 369

369 输出信号的频率和相位,使得二者保持同步。在数字信号处理器(DSP)芯片中,锁相环起着至关重要的作用。 锁相环的基本原理是通过一个反馈环路来实现频率和相位的同步。反馈信号一般由一个包含参考信号和被控制信号的相位检测器产生,

2023-09-02 15:06:34 1688

1688 锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 1594

1594 锁相环频率合成器的优缺点 锁相环频率合成器,又称为PLL(Phase Locked Loop),是一种广泛应用的电路,能够将输入信号的频率合成为电路所需要的频率,并且能够实现对信号的相位和频率

2023-09-02 14:59:33 1212

1212 pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 1503

1503 硬件锁相环电路怎么设计?硬件锁相环电路的设计通常包括以下步骤。

2023-08-08 11:16:46 443

443 大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 1522

1522

锁相环电路,是调频电路的重要组成之一,锁相环电路的原理的认识是DDS学习的一个重点之一。

2023-07-24 15:37:05 1758

1758

锁相环接收一个它所锁定的信号,然后可以从其内部的VCO输出这个信号。乍一看,这可能不是特别有用,但是在你完全明白它,就有可能开发出大量的锁相环应用。

2023-07-17 09:09:37 738

738

锁相环是一种消除频率误差为目的的反馈控制电路,它的基本原理是比较输入信号和反馈输入信号,提取二者的相位差,把此相位差转换频率控制信号,消除它们的频差。

2023-07-12 16:17:58 2878

2878

锁相环:在通信领域中,锁相环是一种利用反馈控制原理实现的频率及相位同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。

2023-06-30 15:53:39 2702

2702

锁相环是一种利用相位同步产生电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。

2023-06-25 09:22:03 5043

5043

及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,锁相环使用教程。话不多

2023-06-14 18:09:08

Skyworks Solutions 的 SKY72300-362 是一款锁相环,频率为 100-2100 MHz,相位噪声 -91

2023-06-12 17:30:57

Skyworks Solutions 的 SKY72301-22 是一款锁相环,频率为 100-1000 MHz,相位噪声 -96

2023-06-12 17:29:24

Skyworks Solutions 的 SKY74038-21 是一款锁相环,频率为 100-2600 MHz

2023-06-12 17:24:47

Skyworks Solutions 的 SKY72302-21 是一款锁相环,频率为 400-6100 MHz,相位噪声 -80

2023-06-12 17:22:25

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 1121

1121

应用一阶差分运算,可以得到周期间抖动。这个指标在分析锁相环性质的时候具有明显的意义

有些特殊的应用(比如针对DDR2/3的时钟信号)还定义了N-cycle jitter,即相邻N个时钟周期的抖动变化

2023-06-02 17:53:10

锁相环(PLL),作为Analog基础IP、混合信号IP、数字系统必备IP,广泛存在于各类电子产品中。

2023-06-02 15:25:14 3548

3548

) 以及其他通常要求时域抖动规范(如周期)的应用生成时钟- 周期和周期抖动。 然而,对于串行解串器 (SerDes)、千兆以太网 (GbE)、10 GbE、同步光网络/同步数字体系 (SONET/SDH) 和光纤通道等高速接口,情况就不同了。有严格的频域抖动要求。 为了正常运行,这些高速接口依赖于低频

2023-05-26 22:15:02 1385

1385 请教大神单相并网逆变器可以不使用锁相环吗?

2023-05-06 16:31:45

锁相环英文名称PLL(Phase Locked Loop),中文名称相位锁栓回路,现在简单介绍一下锁相环的工作原理。

2023-04-28 09:57:31 4374

4374

锁相环在锁定状态时,vco输出波形相对输入波形是否有相位移动?

2023-04-24 11:34:10

当锁相环达到锁定状态时,VCO输出频率与参考频率相等(假设没有分频),那么它们的相位是不是相等呢?还是保持恒定的相位差呢?如果是相位相等,那么是怎么使它们的初相相等的呢?如果是保持恒定的相位差,那么

2023-04-24 11:32:51

锁相环未锁定前,两个频率不同,如何表示环路的瞬时频差和瞬时相差?

2023-04-24 11:31:07

模拟锁相环与数字锁相环的主要区别在哪里?

2023-04-24 10:48:52

如果我输入的信号里面有高频和低频噪声,假设离我要提取的基频信号较远。锁相环怎么能识别我要的基频信号,而不是去跟踪高频或者低频噪声信号?看书没看明白,请解答。谢谢。

2023-04-24 10:20:49

请教一下大神锁相环是如何实现倍频的?

2023-04-24 10:15:39

听说锁相环可以倍频,倍频时输入输出频率都不一样,如何锁相呢?

2023-04-24 10:14:34

锁相环锁定与失锁的标志是什么?

2023-04-24 10:12:07

请问一下锁相环无法锁定怎么办?

2023-04-24 10:09:02

锁相环(Phase Locking Loop)作为无线通信系统的关键电路模块,有着广泛的应用。

2023-04-24 09:31:38 4940

4940

电子发烧友App

电子发烧友App

评论