保护等功能。当检测到异常情况时,芯片会关闭开关管,以防止损坏。

H6392升压恒压DC3.7V升5V 3.7V升9V 3.7V升12V电源芯片

产品描述

H6392是一款外围简单的电流模式升压

2024-03-12 10:04:27

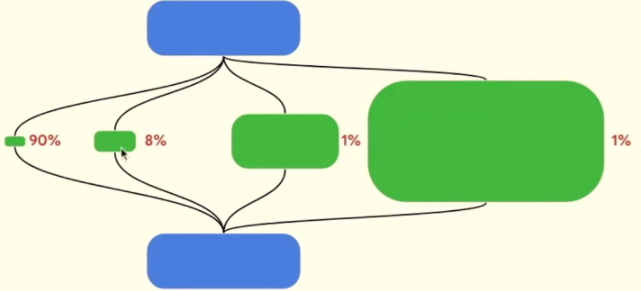

颜色识别出现这种样的左右边框可能是什么原因?我感觉代码好像没有问题上下边界能画出来左右边界就画不出来

2024-03-08 17:29:05

ADMV4530BCCZADMV4530BCCZ 特性RF 输出频率范围:27 GHz 至 31 GHz两种升频转换模式从差分基带 I/Q 直接进行升频转换(I/Q 模式)单上边带升频转换

2024-02-28 20:35:35

边界矢量数据是一种用于描述地理空间边界的格式。它包含了一系列的数据点,这些点按照一定的顺序连接起来,形成了一条封闭的线,来表示地理区域的边界。 边界矢量数据通常以矢量文件的形式存在,矢量文件是由许多

2024-02-25 15:16:57 206

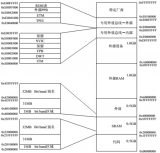

206 。时钟发生器芯片厂家可输出差分100MHz,125MHz,156.25MHz和单端33.33MHz CPU时钟,同时输出6路25MHz缓冲参考时钟。Ø 主要特性l 7路单

2024-02-04 11:41:14

芯片为什么要时钟信号 时钟芯片的作用是什么? 时钟信号在芯片中起着非常重要的作用。它是芯片的“心脏”,相当于人体的心脏,用于同步和控制芯片中的各个功能模块之间的操作。时钟信号可以提供一个稳定的时间

2024-01-29 18:11:31 621

621 时钟Buffer芯片是什么?其作用是啥?它被用在什么地方? 时钟Buffer芯片是一种用于管理和增强电子设备中的时钟信号的集成电路。时钟信号在数字电子设备中非常重要,它用于同步各个模块的工作,确保

2024-01-16 15:10:16 810

810 时钟芯片是一种微型电子器件,其作用是在电子设备中提供精确的时间基准。它能够产生稳定的电子脉冲,用于同步和控制设备中的各种操作和功能。

2024-01-11 18:20:03 640

640 时钟芯片是一种集成电路,用于产生和控制电子产品的时钟信号。它是电子产品中的关键部件,用来确保各个组件和子系统之间的同步和顺序操作。时钟芯片的原理是利用晶体振荡器产生稳定的频率信号,并通过分频和倍频

2024-01-10 14:16:47

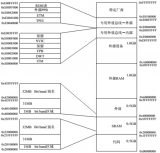

描述:AT32F403A引脚比较紧张,XMC(类似于STM32 FSMC)只支持复用模式,就是A0-A15和D0-D15都用一个引脚,如果要用,只能用锁存器将地址锁存,实现地址线和数据线的分离,目前

2024-01-04 10:46:19

高精度时钟同步芯片高精度时钟芯片典型应用场景:·核心网路由器、交换机·同步以太网设备·电信级边界时钟(T-BCS)和从时钟设备(TimeSlave)·高速以太网端口设备·时钟时间源设备BITS、时间

2023-12-29 09:37:02

。时钟发生器芯片厂家可输出差分100MHz,125MHz,156.25MHz和单端33.33MHz CPU时钟,同时输出6路25MHz缓冲参考时钟。Ø 主要特性l 7路单

2023-12-29 09:29:50

请问在使用16488A时,通过DIO4引入外部时钟,时钟频率为100Hz,会对最终传感器的输出有什么影响?对数据就绪信号DRY有什么影响呢?

手册中看到了可能会造成角度变化的寄存器值溢出,但我用不到这个量。谢谢了!

2023-12-29 06:19:30

100MHz,125MHz,156.25MHz和单端33.33MHz CPU时钟,同时输出6路25MHz缓冲参考时钟。时钟缓冲器芯片Ø 主要特性l 7路单端LVCM

2023-12-28 13:46:09

最近在使用AD9640进行硬件设计

差分时钟部分:

疑问1:datasheet在差分时钟部分提供的参数芯片是95xx系列,这些芯片是不是对输入的时钟信号质量要求也很高?在时钟次系列芯片的时候需要

2023-12-22 08:19:31

问题1:AD9705在只使用单端时钟时,14引脚CLKCOM是否需要接地,数据手册中只说明单端时钟应用时需要将15引脚和14引脚连接;

问题2:请帮忙查看一下在PIN模式下外围电路是否有错误。

2023-12-20 06:15:02

我想用AD9235-65芯片,我的输入信号频率50K左右,输入信号经过滤波后,离AD9235的距离很近,是不是就不需要单端转差分输入了?我的信号本来是单端的。或者更进一步,在什么情况下才需要单端转差分信号?谢谢!

2023-12-14 07:57:13

AD7790数据手册15页中单次转换模式中描述”AD7790上电,执行单次转换,然后返回关断模式。转换需要的时间长度为2*tADC。”这里更新速率采用16.6Hz,正常工作模式不分频单次转换的时间

2023-12-11 06:39:28

的问题。所以我就直接用信号发生器,按照单端1.8 V CMOS输入时钟的接法,输入了一个40Mhz的正弦波。但是还是同样的现象。

有没有人能帮我看看是不是硬件上哪里接错了,还是我的引脚配置有问题。

这个是芯片的原理图:

这是我的测试程序:

2023-12-08 07:14:56

大家好!最近在用AD7768-4采集数据,用的引脚控制,当配置在单次转换模式的时候,SYNC_IN脚由单片机提供周期信号,然后DOUT和DRDY脚没有输出,DCLK脚有时钟信号输出。请问大家在用单次模式的时候是怎么配置的,有哪些注意事项?非常感谢了!

2023-12-07 07:20:38

您好,我利用NXP K10芯片(M4内核)硬件SPI 从机模式与AD7779 主机模式进行通讯读取AD7779 DOUT模式下第0,1两个通道的数据。

AD7779配置为:dclk: 1米 抽取率

2023-12-07 06:30:31

今天想来聊一聊芯片设计中的一个非常基础的概念——时钟。对于外行来说听到这个词可能会感觉迷茫,猜一个大概意思吧可能也不太准。

2023-12-06 14:41:00 303

303 近期在使用AD9162时,配置的模式不成功,测试时钟CLK发现,CLK±单端信号共模电压接近0V,手册上是0.6V,但测试9162-FMC-EZB参考板上的CLK也是共模电压为0V,请问这个会有什么影响吗?

我们现在测试配置JESD204B接口模式不正确,不确定是否CLK的影响?

2023-12-05 06:14:24

将详细介绍Zookeeper引入的机制,包括分布式数据结构、ZAB协议、事务处理、选举算法、观察机制以及ACL安全机制。 分布式数据结构: Zookeeper引入了一些分布式数据结构来支持分布式系统的协调和管理。其中最重要的是Zookeeper的核心数据结构ZooKeeper数据树(Z

2023-12-03 16:38:11 518

518 宝马530e 车型和宝马550e xDrive车型采用了最新的宝马eDrive电驱系统,其中专门为混合动力车型驱动系统开发的电机与其功率元器件被集成到8速Steptronic Sport运动型手自一体变速器中

2023-11-30 16:38:48 360

360 为了像51单片机一样能够对某个管脚单独操作,引入了位带操作这样的操作机制。

2023-11-29 14:36:00 389

389

6-8.4V升9V 12V升24V 1A-2A内置MOS升压芯片DC-DC内置MOS管升压芯片是将较低的电压转换为较高的电压的电子元件,通常用于电源电路中。其中,6-8.4V升9V、12V升24V

2023-11-27 20:21:48

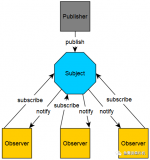

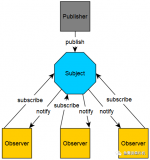

nRF5 SDK从版本14开始,对事件回调机制做了更新,引入了观察者模式,以解耦不同BLE Layer对BLE事件的回调函数。

2023-11-27 10:07:17 258

258

一、引言在电子工程中,B628是一款经典的升压芯片,广泛应用于各种电源管理系统中。本文将对B628升压芯片的参数进行详细解析,帮助读者更好地理解和应用这款芯片。二、B628升压芯片的主要参数1.

2023-11-24 23:56:43

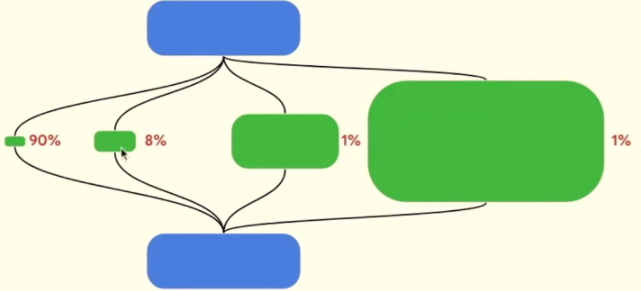

人工智能涵盖了从训练算法到推理的方方面面。它包括大量的训练计划,以及可以适应微型物联网设备的tinyML算法。此外,它越来越多地用于芯片设计的许多方面,以及在晶圆厂中,以关联来自这些芯片的制造、检查、计量和测试的数据。它甚至在现场用于识别故障模式,这些模式可以反馈到未来的设计和制造过程中。

2023-11-23 15:27:25 116

116

华芯微特SWM166D8U6 是一颗主要应用于屏幕驱动的32位MCU,内嵌 ARM® Cortex®-M0 内核,凭借其出色的性能以及高可靠性、低功耗、代码密度大等突出特点,可应用于工业控制、电机

2023-11-20 16:52:25

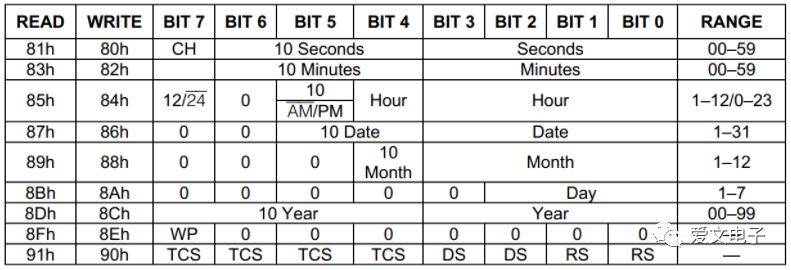

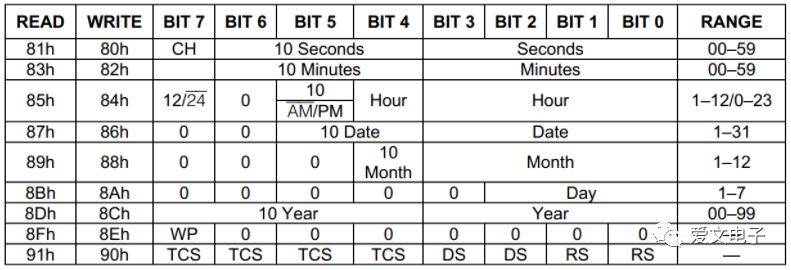

DS1302时钟芯片内部的时钟电路原理是基于晶振的振荡原理。晶振是一种利用晶体的共振特性产生稳定的振荡信号的元件。在DS1302中,晶振的频率为32.768kHz,这是一个非常稳定的频率,适合用于实时时钟应用。

2023-11-18 09:40:41 893

893 DS1302时钟芯片是一种实时时钟芯片,采用三线串行接口与微处理器相连,可以提供年、月、日、时、分、秒等时间信息。

2023-11-18 09:39:40 1187

1187 现在要为da芯片提供1000M的转换时钟信号,原始信号是单端的,但DA芯片是差分输入,所以要加一个单端转差分的差分放大器。问下这个芯片怎么选啊,是不是只要带宽大于1000M就可以了,LMH6552芯片可以吗?

2023-11-17 16:18:09

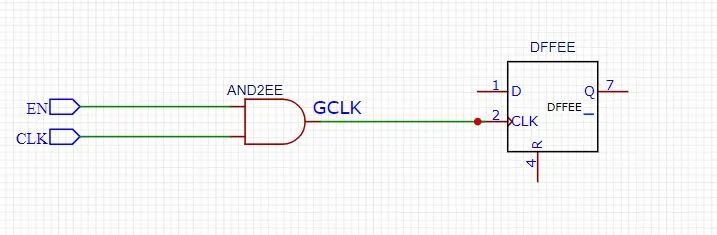

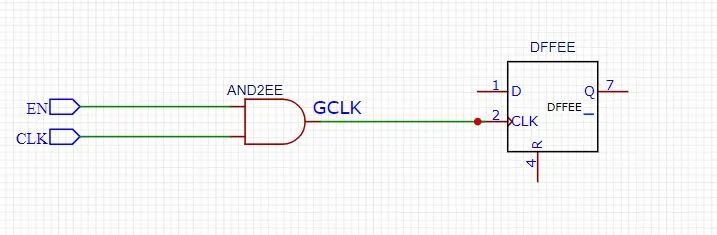

高密度数字CMOS工艺提供的低晶圆成本使其成为混合信号ASIC的首选,特别是对于片上系统设计。能够在对芯片面积影响最小的情况下添加大量亚微米逻辑门,这意味着时钟逻辑覆盖了典型混合信号内核不断增加

2023-11-10 15:41:32 188

188 小规模测试来提供的。这种方法不需要大型实验室设施;然而,它在试样中引入了理想化的应力和应变状态,因此没有考虑复杂应力状态下的材料行为以及整个结构中不同材料与接头、轴承和其他关键细节之间的相互作用

2023-11-06 19:34:14

、高可靠性等特点。但嵌入式Flash的边界主要包括以下几个方面。 首先,嵌入式Flash的物理存储空间是有限的,这个边界可以根据存储芯片的型号和容量来确定。通常,嵌入式Flash的存储容量不如普通闪存存储器,一般在数百兆到几个G之间,因此需要谨

2023-10-29 17:29:44 250

250 AT32F系列单周期模式演示AT32F系列TMR单周期模式的使用方法。

2023-10-27 06:58:38

AT32F4xx SPI使用单工模式通讯演示AT32F403Axx SPI使用单工模式通讯,其余系列使用方式与此类似。

2023-10-27 06:14:26

FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢? FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据不同需要编程,实现不同的功能。在FPGA

2023-10-25 15:14:20 1037

1037 芯片的操作。如果芯片时钟不稳定,设备可能会出现各种问题,甚至在某些情况下,芯片可能根本无法正常工作。在本文中,我们将探讨芯片时钟不稳定的原因以及其影响。 芯片内部时钟紊乱的原因 芯片内部时钟可能会出现不稳定的原

2023-10-25 15:07:59 1145

1145 什么是时钟芯片?时钟芯片的工作原理 时钟芯片的作用 时钟芯片是一种用于计算机或其他电子设备中的集成电路,它提供精准的时钟信号。时钟信号是计算机进行各种操作的基础,比如数据传输、运算等等,所以时钟芯片

2023-10-25 15:02:33 2309

2309 AT32定时器外部时钟模式B+挂起模式本示例代码基于AT32F403A,展示了如何使用AT32 的外部时钟模式B和挂起模式。

2023-10-19 06:20:13

请问下各位大佬,凌力尔特LTC4020芯片CSOUT无输出是什么原因,能充电,且CSP/CSN有差值,之前出现过小电流充电,后来确认受到干扰,增加电容滤波后能大电流充电。

2023-10-08 11:42:45

在芯片设计中,时钟作为一种关键元素,发挥着重要作用。

2023-10-07 16:44:29 1099

1099 时钟芯片的应用非常广泛,例如时钟电路、数据传输和同步,以及计算机、手机和手表等很多电子设备。对这些设备日益增长的需求,推动了时钟芯片市场的增长,预计到2026年,市场规模将增长至约115亿美元。

2023-09-28 14:27:58 1598

1598

一般均内置了可编程的实时日历时钟,用于设定以及保存时间。其采用备份电池供电,在系统断电时仍可以工作,因此时间值不会丢失。另外,实时时钟芯片一般内置闰年补偿系统,计时很准确。实时时钟芯片的这些优点,使得其

2023-09-26 08:27:51

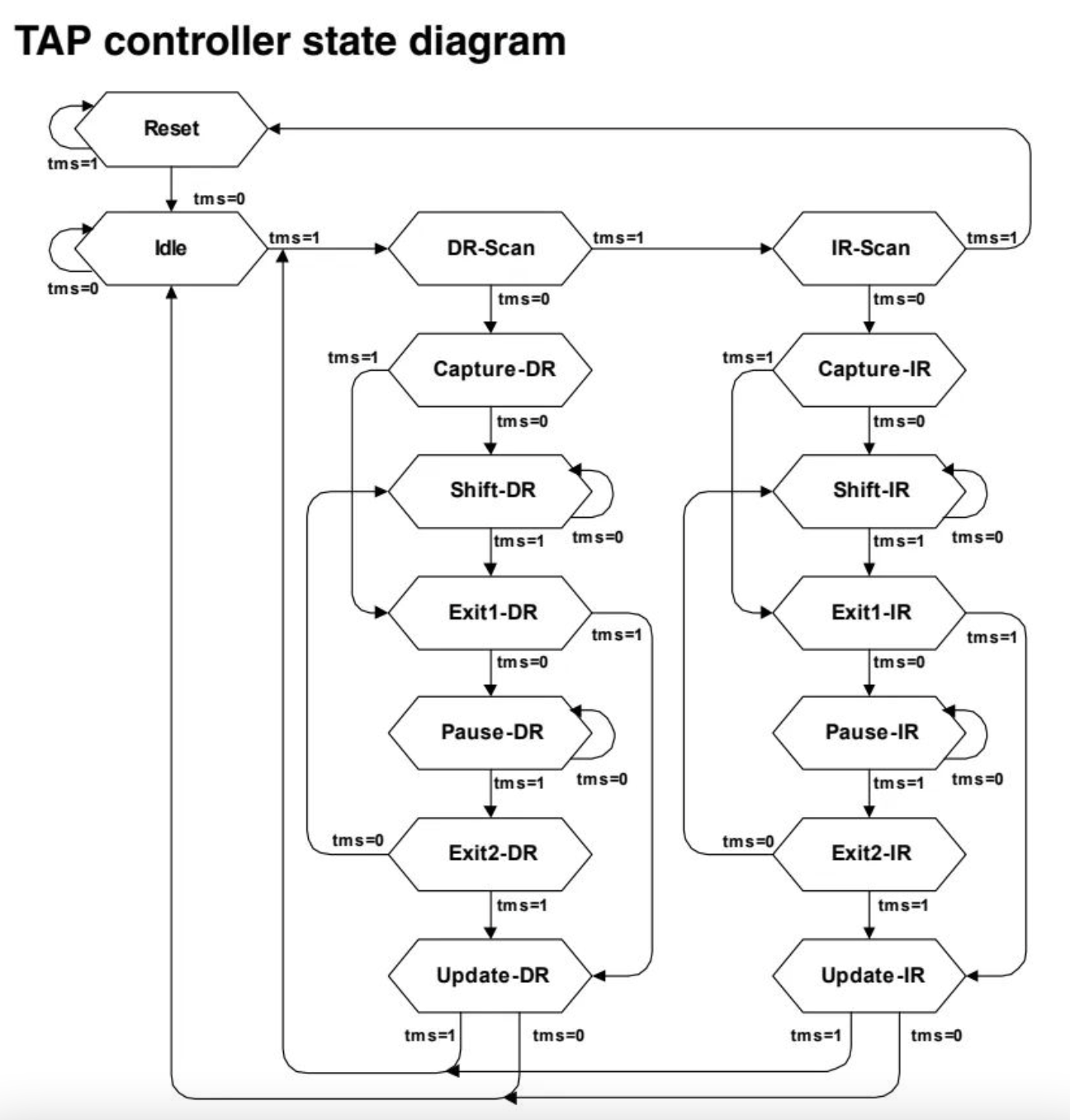

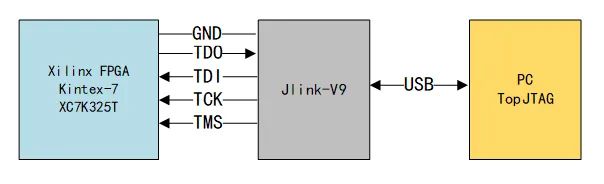

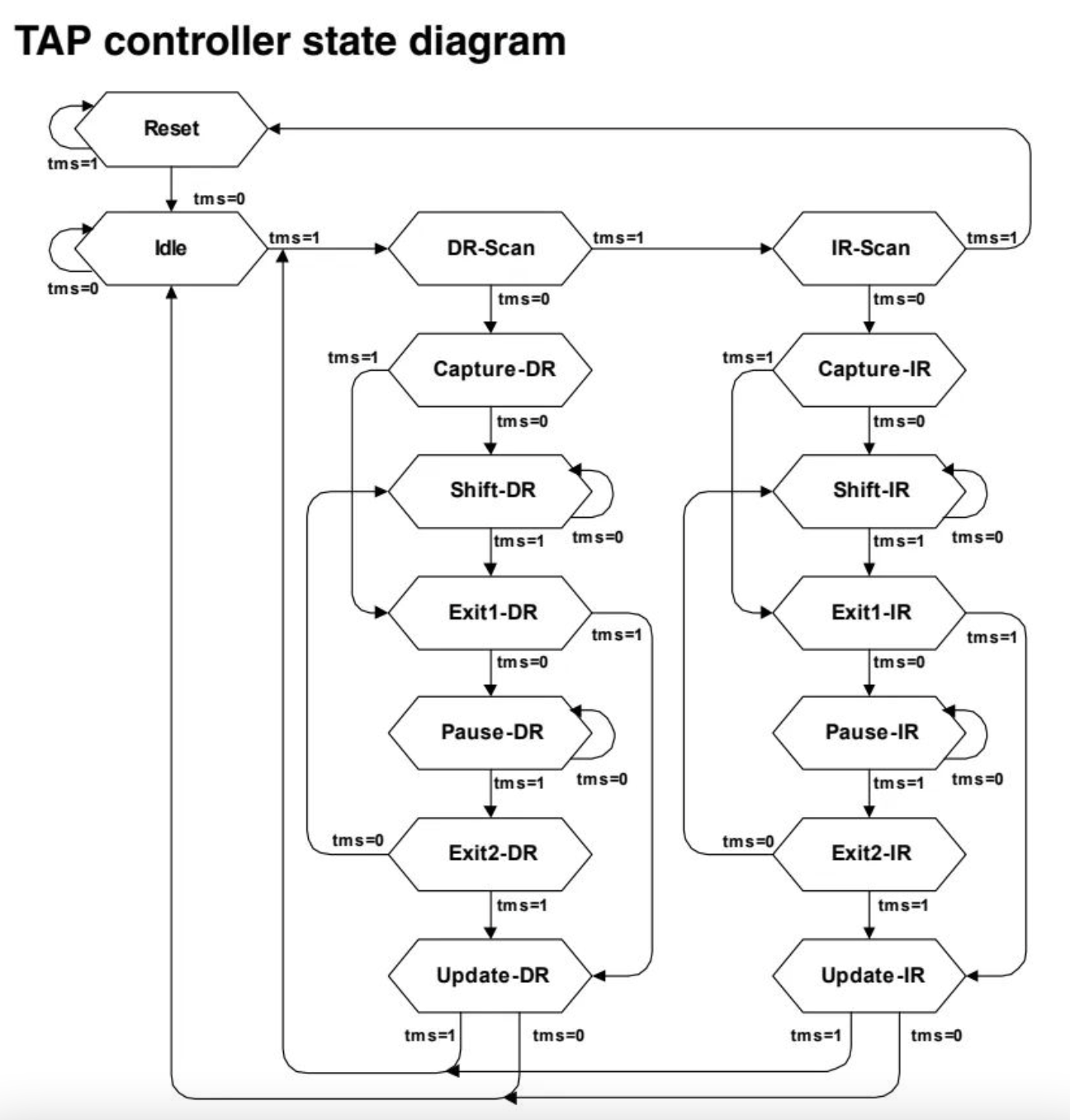

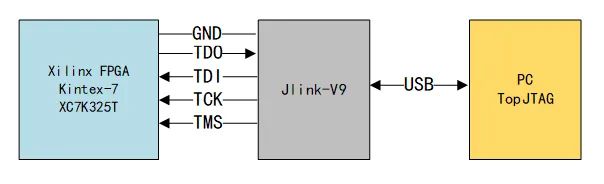

提到边界扫描,就不得不提JTAG,因为边界扫描是JTAG接口的功能之一。

2023-09-22 14:12:17 1495

1495

EG1252是一款高性价比电流模式PWM控制器,适合于中、大等功率反激电源方案以及正激电源方案。EG1252内置抖频功能,具有优良的EMI特性。芯片采用绿色节能模式和打嗝模式控制轻负载和零负载

2023-09-20 17:35:21 1360

1360

中,我们将详细介绍时钟芯片和晶振的区别以及它们在电子设备中的作用和应用。 一、时钟芯片和晶振的定义 时钟芯片是一种集成电路,它能够在电子设备中生成准确的时间信号,可以用来控制电子设备中各个组件的运作时间。它通常

2023-09-15 16:28:20 2859

2859 芯片为什么需要时钟信号? 在我们日常生活中,我们所使用的各种电子设备都需要一个时钟信号来进行计时和同步,例如:手机、电脑、电视、汽车、机器人、智能家居等设备都需要时钟信号。对于各种这些电子设备

2023-09-15 16:28:14 1366

1366 本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1941

1941

上一篇文章,介绍了基于STM32F103的JTAG边界扫描应用,演示了TopJTAG Probe软件的应用,以及边界扫描的基本功能。本文介绍基于Xilinx FPGA的边界扫描应用,两者几乎是一样。

2023-09-13 12:29:37 654

654

前面两篇文章介绍了边界扫描的基本原理和BSDL文件,本文文章介绍边界扫描测试实际使用的两款软件工具,在后面的实战应用部分,会演示基于STM32和FPGA的边界扫描测试应用。

2023-09-11 14:34:56 1278

1278

景下的时序要求。尤其对于需要高速数据传输、信号采集处理等场景的数字信号处理系统而言,FPGA PLL的应用更是至关重要。本文将介绍FPGA锁相环PLL的基本原理、设计流程、常见问题及解决方法,以及该技术在外围芯片时钟提供方面的应用实例。 一、FPGA锁相环PLL基本原理 1.时钟频率的调

2023-09-02 15:12:34 1319

1319 芯片为什么要时钟信号 芯片是现代电子设备的核心组成部分,广泛应用于计算机、手机、电视等各个领域。芯片内部有着复杂的电子元件和电路结构,这些元件和电路结构需要进行同步操作,以实现正确的工作。因此,芯片

2023-09-01 15:38:11 1374

1374 本篇将详细介绍如何使用RA6T2 16位ADC在混合模式(Hybrid mode)下应用采样保持功能进行AD采样,以及后台功能(background)的具体应用。本篇使用FSP建立应用工程,详细讲解

2023-09-01 12:24:01 493

493

如果差分对做单端时钟输出,如P端作为时钟输出,另一端应该如何使用。

2023-08-11 07:26:13

,

程序重启初始化后,自动又进入了中断,经过Debug调试推测是,再由外部中断唤醒的时候定时器扫描又识别了按键按下,又一次进入了STOP模式,那么问题了来,我明明已经关闭了时钟,关闭了定时器,为什么还能

2023-08-05 07:50:57

在 SPI 中,主机可以选择时钟极性和时钟相位。在空闲状态期间,CPOL 为设置时钟信号的极性。空闲状态是指传输开始时 CS 为高电平且在向低电平转变的期间,以及传输结束时 CS 为低电平

2023-07-21 10:08:55 2920

2920

混合器芯片是一种常见的电子元件,用于将不同频率的信号进行混合或分离。在电子设备维修或研发过程中,了解混合器芯片的型号是非常重要的。本文将介绍几种常见的方法,帮助您查看混合器芯片的型号。

2023-07-20 09:47:54 292

292 我觉得称时钟树为芯片的大动脉一点也不夸张,因为所有flipflop 翻转都要受到它的控制。而时钟树的设计到实现是一个很复杂的过程,从流程上说,它牵扯到使用的工具,流程,flow等。从人的角度

2023-07-15 09:28:09 2709

2709

“以芯格物,立诺微行”。随着创新能力和研发能力的不断提高,在国内高性能数模混合信号芯片领域中,芯格诺将以其产品特点、团队建设以及技术优势等差异化特性在以始为终的强大信念下占据一席之位。

2023-07-11 13:37:39 373

373 芯片功耗组成中,有高达40%甚至更多是由时钟树消耗掉的。这个结果的原因也很直观,因为这些时钟树在系统中具有最高的切换频率,而且有很多时钟buffer,而且为了最小化时钟延时,它们通常具有很高的驱动强度。

2023-06-29 15:33:18 1510

1510

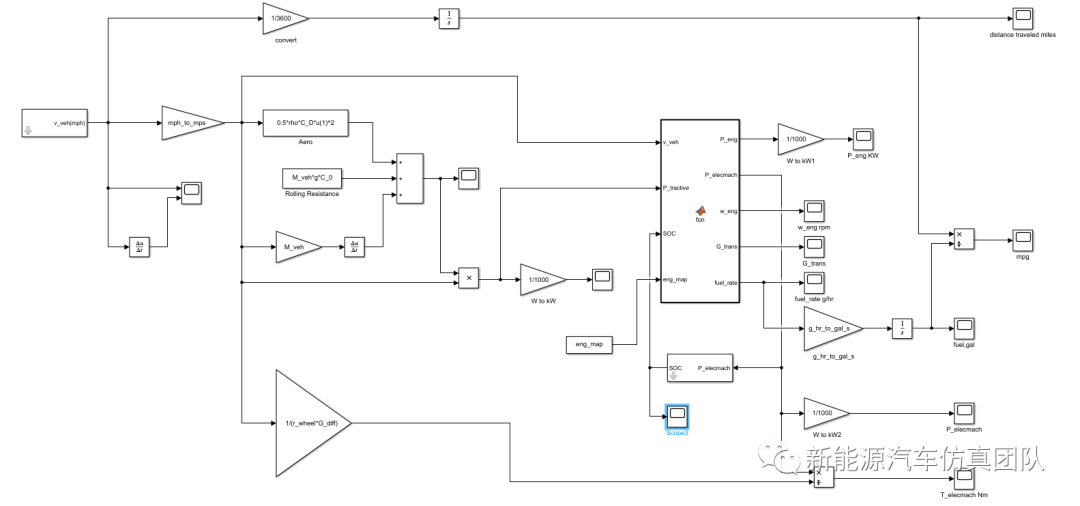

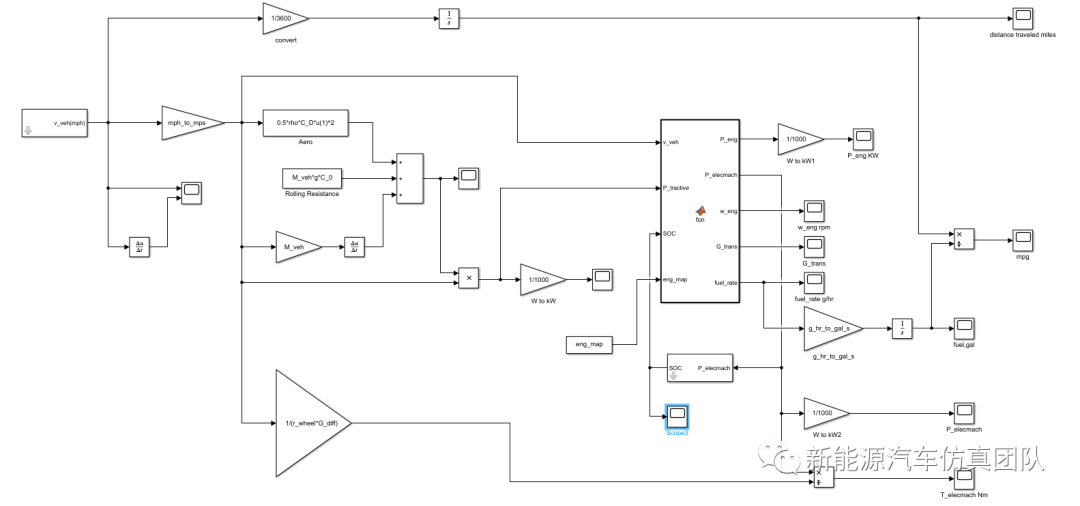

并联混合动力汽车的工作模式可以分为六种。纯电动模式、纯发动机模式、混合驱动模式、充电模式、再生制动模式、怠速停车模式。

2023-06-28 11:21:27 789

789

,内嵌512KB FLASH 128KB ROM以及138KB SRAM,以串口为烧录接口。外国电路简单,射频电路是内嵌在芯片里的,拥有前沿射频电路的设计理念。

512KB系统Flash

128KB

2023-06-27 17:30:17

定时器控制器提供单周期模式、周期模式、双态模式与连续计数模式,还提供由外部脚位来对事件计数功能,以及用来捕捉或重置定时器的输入捕捉功能。

2023-06-26 08:05:00

现在打算使用新唐M451LG6AE芯片设计产品,因为在产品生产后需要经过ICT测试,ICT又需要使用芯片的边界扫描功能。但是在手册中没有找到关于边界扫描的描述,也不知道应该预留哪几个引脚来支持边界扫描。

2023-06-26 06:15:37

M261芯片如何进入睡眠和深度睡眠模式,以及如何退出来?有没有C语言参考?

2023-06-20 07:19:33

电子发烧友网站提供《如何控制IoT ONE Nixie时钟背光—开/关以及颜色和亮度.zip》资料免费下载

2023-06-14 14:26:27 0

0 DS1302是DALLAS公司推出的一款时钟芯片,内部包括时钟/日历寄存器和31字节的数据暂存寄存器,数据通信只需要一根串行输入输出口。

2023-06-13 17:25:59 1376

1376

它有两种操作模式:时钟和设置。时钟模式是标准模式,在此模式下,当前时间显示在数码管上。

2023-06-12 09:01:51 552

552

当为已安装的桌面 Web 应用程序启用无边界模式之后,Web 应用的整个窗口会扩展到覆盖整个浏览器 —— 包括浏览器的标题栏区域和窗口控制按钮(关闭、最大化、最小化)。Web 应用程序开发人员负责整个窗口的绘制和输入处理。

2023-06-05 16:04:42 318

318

,但它导致了目前价值数十亿美元的FPGA产业。由于其重要性,XC2064被列入芯片名人堂。在这篇文章中,我们对Xilinx的XC2064进行了逆向工程,解释了它的内部电路(上图)以及 "比特流

2023-06-02 14:03:57

“在同步下一代电子产品方面,使用传统时钟架构的技术扩展遇到了瓶颈。Stathera的技术引入了一种集成和制造时钟器件的新方法。”Stathera首席执行官(CEO)兼联合创始人George Xereas表示,“我们很高兴成为唯一一家拥有最先进DualMode频率技术的公司

2023-05-22 15:17:25 506

506

1.基本介绍MS1861 单颗芯片集成了HDMI、LVDS 和数字视频信号输入; 输出端可以驱动MIPI(DSI-2)、 LVDS 、Mini-LVDS 以及 TTL 类型 TFT-LCD

2023-05-20 11:51:15

SoC的顶层的约束适用于FPGA到其各自时钟域中的各个Flip_Flop,如果定义了跨时钟域,也适用于FPGA之间。当我们可以确保每个FPGA边界都有一个IOFF,它与SoC中相应的元素对齐时,这一点对于性能而言非常重要。

2023-05-13 09:38:09 1352

1352

时钟同步的组网

有了时钟源,还需要一个网络,把时钟分发下去。根据组网的不同,可分为集中式和分布式这两种方式。

集中式时钟同步的代表为基于分组网络的同步以太网(SyncE),1588v2等技术

2023-05-10 17:09:50

在Fluent分析中边界条件的设定是非常重要的,可对Fluent中的边界条件进行简易分类为进出口边界条件、壁面条件、内部单元边界、内部表面边界等;

2023-05-02 15:20:00 3167

3167

本章教程主要在SPI单工通信方式下进行1条时钟线和1条单向数据线配置,并进行主机接收从机发送。 1、SPI简介及相关函数介绍关于SPI单工通信模式下1条时钟线和1条单向数据线配置介绍,在第46章已经

2023-04-25 16:50:41

本章教程主要在SPI单工通信方式下进行1条时钟线和1条双向数据线配置,并进行主机接收从机发送。 1、SPI简介及相关函数介绍关于SPI单工通信模式下1条时钟线和1条双向数据线配置介绍,在第46章已经

2023-04-25 16:48:14

本章教程主要在SPI单工通信方式下进行1条时钟线和1条双向数据线配置,并进行主机发送从机接收。 1、SPI简介及相关函数介绍SPI支持以三线同步串行模式进行数据交互,加上片选线支持硬件切换主从模式

2023-04-25 16:47:06

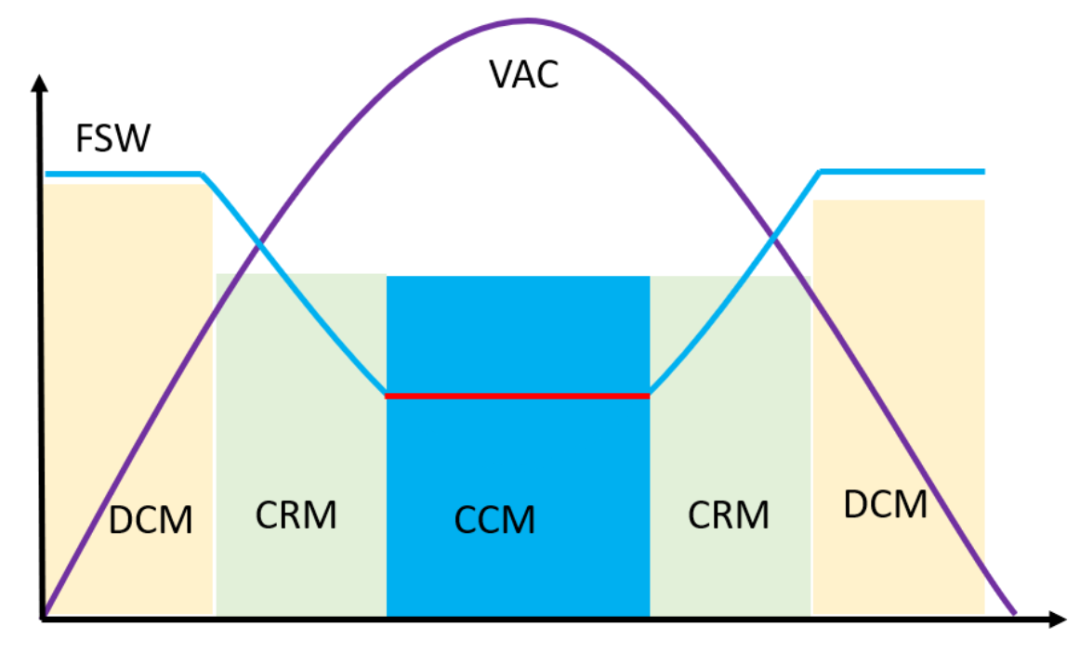

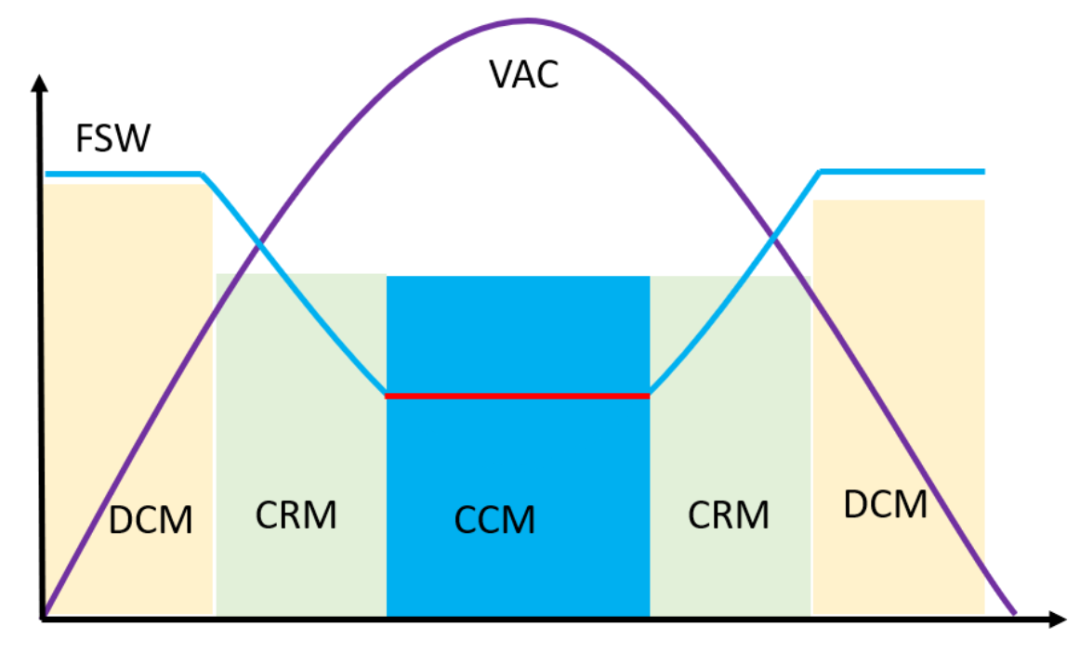

简单地说,混合PFC的控制策略就是操纵开关频率在正弦电压内进行变化来进行跨越多个区域,难点是多模式区域的增益不会统一,实现多模式优秀的电流控制效果就是难题

2023-04-25 14:20:29 1013

1013

JLINK调试雅特力AT32F403Avc的问题,无法发现芯片(在keil下可以),如何解决?我把芯片型号切换城STM32F103vc就可以

2023-04-17 17:43:42

近日,数模混合信号链和时钟芯片设计公司核芯互联,宣布完成数亿元B轮融资,本轮融资由招商资本,华强创投和老股东东方富海联合投资。 核芯互联成立于2018年,在北京、青岛、上海、成都设有研发中心

2023-04-04 17:20:06 1427

1427 的 2000 个虚拟时钟。我唯一没有做的是在 IOCONFIG 寄存器中设置 TDR 数据,因为应用笔记(在 BSDL 文件中提到)不可用!有人可以发布 TDR 模式吗?我尝试使用 NXP 的 LS1028 评估板设置边界扫描。结果是一样的。还有其他建议吗?

2023-03-31 06:52:45

我正在使用 IMX8m Plus 构建定制板,我想使用边界扫描来测试板的连接。为此,我正在 (8MPLUSLPD4-EVK) 上进行试验,以检查 JTAG 连接以及进入边界扫描模式需要执行的操作。我

2023-03-29 06:05:21

电子发烧友App

电子发烧友App

评论