Achronix的Speedster7t支持PCIe Gen5和112G Serdes,而AMD的高端系列Virtex Ultrascale+也仅仅支持到PCIe Gen4,也只在最高端的FPGA中支持到58Gb的GTM,大多数Virtex Ultrascale+仅仅支持32.75Gb的GTY。

2024-03-18 10:55:34 34

34

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

“基于OpenHarmony的团结引擎应用开发赛”是开放原子全球开源大赛下开设的新兴及应用赛的赛题之一,本次赛题旨在鼓励更多开发者基于OpenHarmony 4.x版本,使用Unity中国团结引擎

2024-03-13 10:45:10

逻辑模块和 85,000 个晶体管,门数量不超过 1000 个。对比 2016 年赛灵思发布的 VIRTEX UltraScale,16nm 制程,系统逻辑单元最高达378 万个。FPGA 制程迭代在

2024-03-08 14:57:22

美光科技股份有限公司(Micron Technology, Inc.)是全球内存与存储解决方案的领先供应商,近日宣布已经开始量产其HBM3E高带宽内存解决方案。这一重要的里程碑式进展再次证明了美光在内存技术领域的行业领先地位。

2024-03-05 09:16:28 307

307 VisionFive 2 生态进展双周报

赛昉新闻速递

赛昉计划逐步把Linux kernel的维护重心从v6.1迁移至v6.6,预计将在今年5月完成。届时,赛昉官方维护的kernel版本将为

2024-02-29 15:45:08

我们用的主平台是赛灵思,想要通过CYUSB3014+FPGA实现OTG的功能,有几个问题,想请教一下。

1.是否有可以验证功能的EVK呢,我找了下FX3 DVK似乎买不到

2024-02-29 07:20:21

cy7c68013a和FPGA采用同步slfifo模式通讯,当上位机使用control center发送2个字节时,FPGA收到数据正确,当发送4个以上字节时会出现头两个字节丢失,后两个字节重复的现象,百思不得其解?固件使用官网的slavefifo的固件未更改。

2024-02-28 08:25:09

我现在正在使用CY7C68013A开发一个摄像头产品,首先PC上位机传输300K左右的配置数据传输给FPGA(通过CY7C68013A的端口6,端口位OUT),然后FPGA开始采集图像并把采集到图像

2024-02-27 08:00:01

CYT2B7 can id filter设置指定id 0x7A1,不能识别。但设置为0xA1可以正常识别。是否对id有限制?原因是什么?

2024-02-27 07:47:54

中数据阻塞丢失。固件设置buffer个数为2,大小为1024。传输的数据为32位,根据signalTap抓取的信号(见下图)可以发现,开始发送数据后,填满第一个buffer时,FLAG_A拉低,但很快

2024-02-27 06:37:31

基于Lattice MXO2 LPC的小脚丫FPGA核心板 - Type C接口

开发板的硬件规格如下:

核心器件:Lattice LCMXO2-4000HC-4MG132

132脚BGA封装

2024-01-31 21:01:32

本次测试采用了Cisco NCS 1014 C波段2.4T WDM转发器线路卡与Acacia的相干互连模块CIM 8(业界首个1.2Tbps面板可插拔相干解决方案)设备。

2024-01-31 12:38:07 202

202 AMD开始交付其首批用于AI和HPC的Instinct MI300X GPU。据LaminiAI首席执行官Sharon Zhou透露,该公司已经收到了这批GPU,并计划使用它们来运行大型

2024-01-24 16:57:58 314

314 芯片电路图方案

2024-01-12 18:19:16

目前想要通过DDR200T开发板做一个基于FPGA的卷积神经网络软硬协同加速器

DDR200T开发板中FPGA模块用的是xc7a200t和gd32vf103(mcu)之间是通过什么传输数据的?

是通过AXI总线进行传输的么?有没有大佬有DDR200t开发板这两个模块的交互原理图,求解答

2024-01-10 06:28:53

,最主流的FPGA开发软件有两个,就是赛灵思/AMD的Vivado,还有英特尔的Quartus。这里又来一个二选一,大家要根据自身情况去选择,比如你们学校教的是谁家的FPGA,或者你用谁家的开发板,或者

2024-01-02 23:03:31

首先,FPGA开发工程师是一个相对高薪的工作,但是,很多同学在刚入门时都会有一种无从下手的感觉,尤其是将FPGA作为第一个要掌握的开发板时,更是感觉苦恼;本人也是如此,以下就本人学习FPGA开发的一些情况做一些介绍,希望后来者能够少走弯路。

2023-12-28 09:50:32 196

196 模数转换器AD9625的评估板AD-FMCADC3-EBZ能不能和赛灵思的Virtex7系列FPGA开发板连接,我看到他们都具备JESD204B接口,物理接口上能直接连吗?还是说需要在使用转换接口来连接?

2023-12-08 08:25:12

现在的项目用到了AD2S1210,用FPGA和这个片子通过SPI通信,现在调试过程中发现如下问题:周期性对该AD芯片的激励频率设置寄存器(0x91)设置不同频率并回读该寄存器,发现设置值小于0x40时,回读时返回值不正确,有工程师遇到过类似问题么?

工作条件:配置模式,控制寄存器设置为0x7F;

2023-12-07 08:05:27

用ad5220数字电位计模拟测温电阻上升过程,使用时为什么一用数字表测量阻值,芯片就开始发烫?重新上电后恢复中值并冷却。

up/down 悬空有影响么?up/downcs plus 需要加限流电阻么?手册里好像说内部已经有1k电阻了。

2023-12-06 08:31:48

] = (UCHAR_T)(cmd >> 8);

buf[1] = (UCHAR_T)(cmd & 0x00FF);

buf[2] = (UCHAR_T

2023-12-01 22:55:07

xilinx的FPGA,BANK引脚VREF,VRN,VRP都是什么意思?如何使用,DATASHEET没看明白,谢谢请帮忙解答谢谢!

补充一下:Virtex II Pro,XC2VP4,谢谢

2023-11-28 07:19:03

/tuyaos-development-board-t2/main/tools/bk_writer_gui_V1.7.5.zip

下载QIO文件,起始==0x00000000==

下载UA文件,起始==0x00011000==

七

2023-11-25 23:38:02

可以商用的集成全域硬2D NoC的FPGA器件,以每通道512Gbps的速率和超过2Tbps的总带宽来与所有系统接口和FPGA逻辑阵列互连。

2023-11-24 16:19:45 184

184 分享易灵思FPGA

2023-11-19 16:13:03

描述 Kintex®-7 FPGA 为您的设计在 28nm 节点实现最佳成本/性能/功耗平衡,同时提供高 DSP 率、高性价比封装,并支持 PCIe® Gen3 和 10 Gigabit

2023-11-10 14:22:14

时间一般晚 于对应商业级器件 3-5 年,长期落后于当时最领先的器件 1-2 个代际, 10-15 年前的 FPGA 依然在航天器上广 泛使用。然而,近两年来,我们看到 FPGA 龙头赛灵思加快了宇航

2023-11-09 14:09:46

概念和特点比较简单,没有完全形成气候。

赛灵思:重点布局深耕中国市场

赛灵思公司目前在中国内地设有6家办事处,公司很多项重要的区域性业务均以中国为基地。例如,亚太区技术支持中心设在上海。另外,针对

2023-11-08 17:19:01

、连续打卡一周(7天):电子发烧友月度VIP

2、连续打卡两周(14天):三合一数据线

3、连续打卡三周(21天)(需在FPGA技术社区至少发布文章x1,问答x1):精美开发板+电子发烧友月度

2023-11-06 18:28:59

电子发烧友网站提供《基于Virtex-5FPGA的系统监测器设计.pdf》资料免费下载

2023-10-19 10:49:30 0

0 超声波时灵使不灵,怎么办呢??

2023-10-19 06:22:18

推断开发平台,它可以帮助开发者在赛灵思的 FPGA 和自适应 SoC 上实现高效的 AI 应用部署。它是一个强大而灵活的 AI 开发平台,它可以让您充分利用赛灵思硬件平台的优势,实现高性能、低功耗

2023-10-14 15:34:26

速率133MHz。GPMC是AM62x、AM64x、AM437x、AM335x、AM57x等处理器专用于与外部存储器设备的接口,如:(1)FPGA器件(2)ADC器件(3)SRAM内存(4)NOR

2023-09-30 23:43:29

蔚来手机9月28日开始发货 NIO Phone起售价6499 蔚来造手机、小米造车,不知道以后华为会要造什么?或者苹果造车? 蔚来用户需要一款与蔚来汽车无缝连接的手机。所以蔚来手机来了

2023-09-26 18:39:43 525

525 SDK 是一种构建在开源且被广泛采用的 GStreamer 框架上的应用框架。这种SDK 设计上支持跨

所有赛灵思平台的无缝开发,包括赛灵思 FPGA、SoC、Alveo 卡,当然还有 Kria

2023-09-26 15:17:29

最高到 400MHz,2 颗 DDR3 的数据位宽为 32bit,总数据带宽最高 25600(800×32)Mbps,充分满足高速多路数据存储的需求。

PGL50HFPGA带有4路HSST高速收发器

2023-09-20 17:34:13

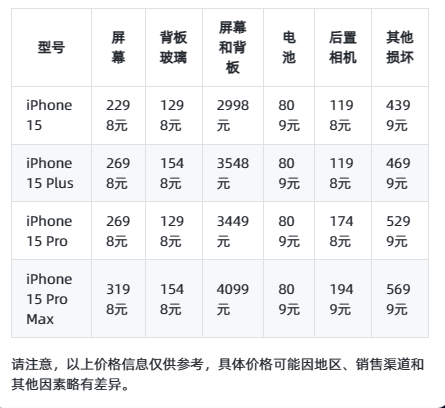

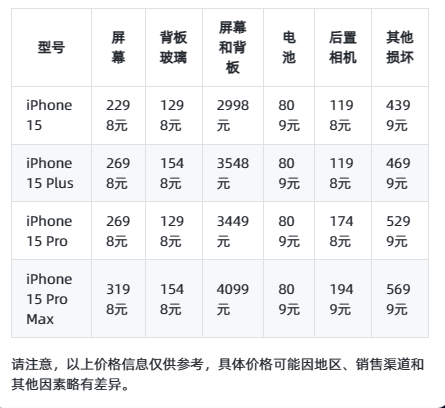

苹果公司于9月13日凌晨推出了iPhone 15系列智能手机,上周五正式开始接受消费者的预订,而在本周五将开始发货。与此同时,苹果官网公布了iPhone 15系列四款新机的维修价格。

2023-09-19 17:47:18 2245

2245

盘古50Pro核心板是一款基于紫光同创Logos2系列PG2L50H-FBG484主控芯片的全新国产高性能FPGA核心板,相较于第一代盘古50K器件全新升级,具有高数据带宽、高存储容量的特点,适用于

2023-09-18 17:02:58

电子发烧友网站提供《Artix-7 FPGA:成本优化器件中的性能和带宽.pdf》资料免费下载

2023-09-18 10:07:35 0

0 电子发烧友网站提供《在Virtex-6 FPGA中使用全数字VCXO替换技术实现三倍速率SDI直通.pdf》资料免费下载

2023-09-14 14:52:17 3

3 电子发烧友网站提供《Virtex UltraScale+ FPGA数据手册:DC和AC开关特性.pdf》资料免费下载

2023-09-13 09:45:36 0

0 很多朋友反映 ST 官网的例程 stsw-stm32060(也就是 STM32F2x7 的以太网例程)中的FreeRTOS 驱动有问题,表现为在网络压力测试下向 STM32 进行 ping 测试

2023-09-11 06:51:54

x8,LA、HA、HB接口。

单组GTH引脚分布不要跨越FPGA Bank。

在板卡布局时建议分散布局,更容易适配子卡。

2)FPGA 外接2 QSFP+接口。

3)FPGA 外接1个

2023-09-08 15:07:12

描述 Artix®-7 器件在单个成本优化的 FPGA 中提供了最高性能功耗比结构、 收发器线速、DSP 处理能力以及 AMS 集成。包含 MicroBlaze™ 软处理器和 1,066

2023-09-01 10:47:25

描述 Virtex®-7 FPGA 针对 28nm 系统性能与集成进行了优化,可为您的设计带来业界最佳的功耗性能比架构、DSP 性能以及 I/O 带宽。 该系列可用于 10G 至 100G

2023-09-01 10:41:54

描述 Kintex® UltraScale™ 器件在 20nm 节点提供最佳成本/性能/功耗比,包括在中端器件、下一代收发器和低成本封装中的最高信号处理带宽,实现性能与成本效益的最佳组合

2023-09-01 10:24:44

郭明錤表示,台玻生产的玻纤布,到今年第二季度的3季度开始发货给台光电主要包括ai相关产品的AI服务器(训练与推理)、光学模组等,客户包括微软、亚马逊等

2023-08-31 10:40:38 314

314 速率133MHz。GPMC是AM62x、AM64x、AM437x、AM335x、AM57x等处理器专用于与外部存储器设备的接口,如:

(1)FPGA器件

(2)ADC器件

(3)SRAM内存

2023-08-22 10:58:39

来自微型电路的T2-1-X65+是频率0.07至200兆赫的巴伦,插入损耗0.42至2.74分贝,电流30毫安,功率0.25瓦,返回损耗4.14至20.44分贝。标签:插入,不平衡到平衡。

2023-08-21 14:22:56

与openKylin社区技术专家经过长期开发、调试,克服诸多挑战,最终实现了首批ROMA笔记本电脑的量产交付,这是RISC-V芯片原厂、开源社区与终端设备厂商通力合作的里程碑式的突破!

8月23日下午,ROMA

2023-08-21 13:41:21

来自微型电路的T2-1-2W-X65+是频率为5-120兆赫的巴伦,插入损耗0.37至0.71分贝,电流30mA,功率2W,返回损耗12.01至20.02分贝。标签:插入,平衡。

2023-08-21 10:53:42

本板卡基于Xilinx公司的FPGA XC7VX690T-FFG1761 芯片,支持PCIeX8、两组 64bit DDR3容量8GByte,HPC的FMC连接器,板卡支持各种FMC子卡扩展。软件支持windows,Linux操作系统。

2023-08-17 11:12:01 913

913

kv260采用的FPGA型号是什么 KV260采用的FPGA型号是Xilinx Virtex-6 XC6VLX760。 FPGA(Field-Programmable Gate Array)是一种

2023-08-16 11:15:40 717

717 本板卡基于Xilinx公司的FPGA XC7VX690T-FFG1761 芯片,支持PCIeX8、两组 64bit DDR3容量8GByte,HPC的FMC连接器,板卡支持各种FMC子卡扩展。软件支持windows,Linux操作系统。

2023-08-14 21:33:37 839

839

开发板:正点原子达芬奇Pro开发板FPGA Artix-7 XC7A100T

调试器:Sipeed USB-JTAG/TTL RISC-V调试器

OpenOCD报错如下:

Open On-Chip

2023-08-12 07:42:11

描述 Spartan®-6 器件可提供各种业界领先的连接特性,如高逻辑引脚比、小型封装、MicroBlaze™ 软处理器、800Mb/s DDR3 支持以及各种多样化支持性 I/O 协议等。这些器件采用 45nm 技术构建,是汽车信息娱乐、消费类以及工业自动化中各种高级桥接应用的理想选择。 特性 可编程的系统集成 I/

2023-08-08 11:55:55

描述 最新 Virtex® UltraScale+ 器件基于 UltraScale 架构,可在 FinFET 节点上提供最高的性能及集成功能,包括 58G 的最高串行 I/O 以及 DSP

2023-08-07 10:41:14

在高通滤波器中,通带带宽是指允许通过的频率范围。通带带宽定义为从滤波器的下截止频率开始,到无穷大频率为止的频率范围。

2023-08-03 09:38:12 782

782 M690SDM Final 数据表

2023-07-26 18:30:56 0

0 Kintex®-7 FPGA系列为您的设计提供28nm技术最好性价比, 同时为您提供高DSP比率, 高性价比封装, 以及支持PCIe® Gen3与10千兆以太网等主流标准. 与前一代相比, 新一代

2023-07-25 14:50:00

概述详情:Virtex@-7 T和XT FPGAs可在-3、-2、-1和-2L级速度等级,其中-3级性能最高。-2L器件在VCCINT=1.0V时工作,并被屏蔽以获得较低的最大静态功率。速度规格

2023-07-25 14:46:49

原理图s for the VIRTEX5MEZPWREV1Z 评估板

2023-07-07 19:59:21 0

0 XC7VX690T-2FFG1158IIntroduction Virtex®-7 T and XT FPGAs are available in -3 -2 -1 and -2L speed

2023-07-07 14:32:20 0

0 由于 FPGA 具有 可 编 程 和 可 重 配置, 因此 可以 为 加快 设计 过程 铺平 道路, 因为 您 可以 随着 设计 要求 的 变化 轻松 进行调整。然而,开发支持FPGA的电源可能非常具有挑战性。

2023-06-29 09:14:48 747

747 电子发烧友网站提供《在Spartan 6 FPGA上从头开始实现全加器.zip》资料免费下载

2023-06-15 10:13:28 0

0 跪求新唐M0518SD2AE,LQFP64(7x7)的AD封装

2023-06-15 08:07:04

传感器,基于IIC通信。其通信原理比较简单,可以直接参考HS300x的数据手册。

其IIC地址为0x44,想知道其原理,可以参考我之前发布的帖子【RA4M2设计挑战赛】2. 硬件IIC读取HS3003

2023-06-07 21:45:10

大家好,我的需求是将FPGA(赛灵思K7)采集的数据发送至工控机(Linux),数据量为每秒5M字节,并解析工控机发送的控制指令(50字节/秒),有同个问题如下:

1.ARM选什么型号比较好

2023-06-02 18:25:04

【瑞萨RA MCU创意氛围赛】1. PWM驱动LED以及STLINK下载配置【瑞萨RA MCU创意氛围赛】2. KEIL下串口重定向printf和scanf

前言

OLED是单片机开发中会

2023-05-26 14:06:17

连接器)接口进行通信,支持多板级联,模块为100%国产化设计(同时也兼容进口器件)。FPGA芯片可选上海复旦微或深圳国微的V7-690T,两组DDR3的存储容量分别可配置为2~4GByte。板载有1个

2023-05-21 18:27:41

测量温度一段时间后,传感器开始发送错误数据(指示温度为 -147,湿度为 100)。我已经修改了代码,以便在进行测量后传感器关闭并且在下一个循环之前不会再次打开,但结果是相同的。目前我不知道如何解决这个错误。

2023-05-15 06:56:27

FPGA, Artix-7, MMCM, PLL, 285 I/O, 628 MHz, 101440单元, 950 mV至1.05 V, FBGA-484Xilinx Artix®-7 FPGA系列

2023-05-10 16:03:24

的K7-325T或K7-410T FPGA,DDR3的存储容量可选配2GByte或4GByte。板载有1个FMC-HPC全互联的接口,可以适配大多数ADC/DAC FMC子卡。

应用行业1)无线电监测与测向定位

2023-05-09 20:07:51

VIRTEX5MEZPWREV1Z 用户指南

2023-04-26 19:04:43 0

0 是指一个国家或地区连接国际互联网所拥有的带宽资源。随着数字经济的不断发展,国际带宽的需求量不断增长。目前,全球国际带宽的总量已经超过了1Tbps,其中美洲和亚洲的国际带宽占比最高,分别为34%和31%。同时,全球云计算市场的不

2023-04-26 14:30:31 534

534 2SJ690 数据表

2023-04-20 19:30:10 0

0 M690SDM Final 数据表

2023-04-12 18:55:40 0

0 。如下为创龙科技异构多核部分产品列表:图 34款“旗舰”新品全志T113-i双核Cortex-A7@1.2GHz含税99元起全志T3/A40i + 紫光同创Logos业界首款国产ARM + FPGA瑞芯微RK3568J/B2全能工业平台TI AM62xAM335x升级平台之经典再造

2023-03-31 16:19:06

Cortex-A7 + 紫光同创Logos PGL25G/PGL50G FPGA设计的异构多核国产工业开发板,ARM Cortex-A7处理器单元主频高达1.2GHz。评估板由核心板和评估底板组成,核心板CPU

2023-03-31 15:35:28

Virtex® UltraScale™ FPGA Evaluation Board

2023-03-30 11:49:38

Virtex® UltraScale™ FPGA Evaluation Board

2023-03-30 11:49:37

VIRTEX-7 VC707 EVAL KIT

2023-03-30 11:49:36

VIRTEX-7 VC707 EVAL KIT JAPAN

2023-03-30 11:49:36

KIT FOR VIRTEX ULTRASCLE FPGA

2023-03-30 11:49:31

EVAL BOARD VIRTEX-7 CHARACTER

2023-03-30 11:49:31

EVAL BOARD VIRTEX-7 CHARACTER

2023-03-30 11:49:31

Virtex®-7 VX485T-2 Virtex®-7 FPGA Evaluation Board

2023-03-30 11:49:31

VIRTEX-6 FPGA CONNECTIVITY KIT

2023-03-30 11:49:30

LR690-N

2023-03-29 21:52:23

VIRTEX-7 FBGA BLOCK FBGA484

2023-03-23 08:06:50

电子发烧友App

电子发烧友App

评论