CXL(Compute Express Link)是一种业界支持的高速缓存一致性互连协议,用于处理器、内存扩展和加速器之间的通信。

2024-03-20 13:56:53 52

52

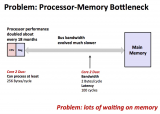

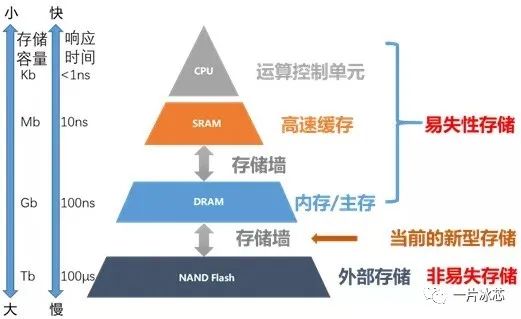

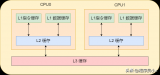

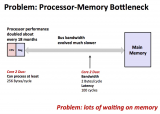

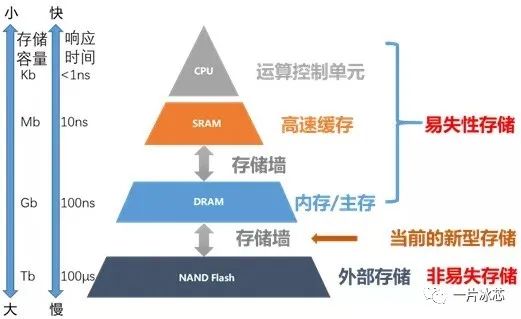

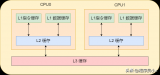

高速缓存(Cache)主要是为了解决CPU运算速度与内存(Memory)读写速度不匹配的矛盾而存在, 是CPU与存储设备之间的临时存贮器,容量小,但是交换速度比内存快。内置高速缓存通常对CPU的性能提升具有较大作用。

2024-01-22 16:07:33 489

489

结合5nm和6nm工艺节点,采用先进的小芯片(Chiplets)设计,全新的计算单元和第二代AMD高速缓存技术,相比AMD RDNA 2架构的每瓦性能提高54%;

2024-01-04 16:27:36 509

509

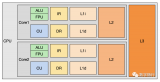

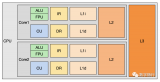

CPU的核心功能包括数据运算和指令控制。CPU运算的数据和执行的指令全部存储在CPU的寄存器中,这些数据和指令又都来自于CPU高速缓存。

2024-01-02 16:01:48 662

662

缓存预热就是系统上线后,提前将相关的缓存数据直接加载到缓存系统。

2023-12-25 09:41:02 250

250

靠近 CPU 的小、快速的高速缓存存储器(cache memory)做为一部分存储在相对慢速的主存储器(main memory)中数据和指令的缓冲区域。

2023-12-25 09:21:50 241

241

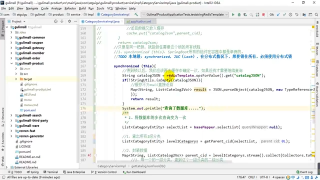

MyBatis是一种轻量级的持久化框架,它提供了一级缓存和二级缓存的机制来优化数据库操作性能。一级缓存是默认开启的,而二级缓存需要手动配置启用。 一、一级缓存 1.1 缓存生命周期 一级缓存存在于

2023-12-03 11:55:11 438

438 SRAM是目前最成熟的易失性高速存储器,通常由6管(6T)实现数据的读写,可以用做CPU和内存(DRAM)之间的高速缓存。

2023-10-31 17:46:55 1259

1259

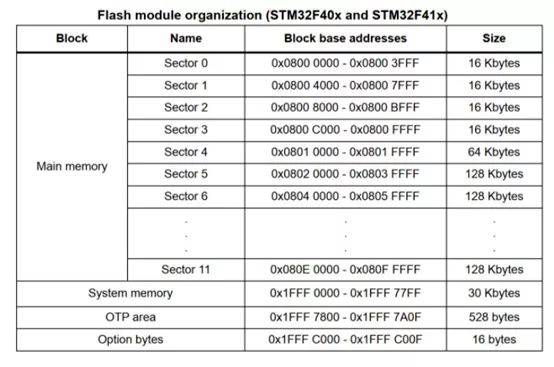

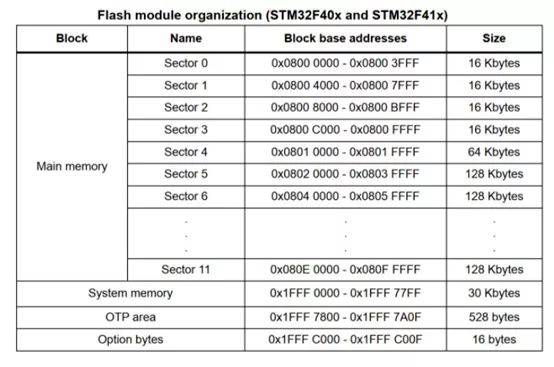

STM32加密问题:怎样预置一段Flash读保护和清除读保护的程序 在STM32加密方案中,为了对芯片进行加密,我们需要加入读保护功能。读保护功能即使未经授权的人无法读取芯片的Flash程序

2023-10-29 17:24:46 1083

1083 STM32的Flash写了保护怎么办?STM32如何设置读保护和解除读保护? 一、STM32的Flash写了保护怎么办? 当STM32的Flash写了保护后,我们需要先了解STM32的Flash

2023-10-29 17:24:43 5495

5495 讲讲STM32单片机Flash的读保护和写保护

2023-10-26 15:52:31 3243

3243

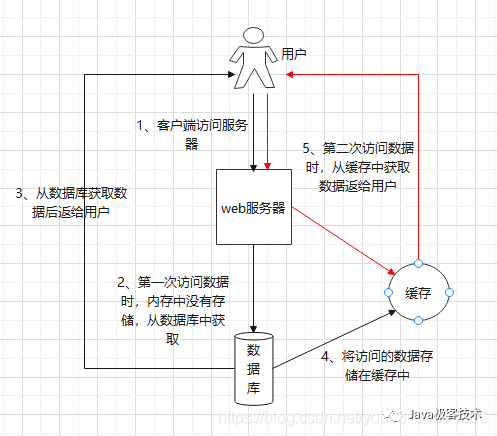

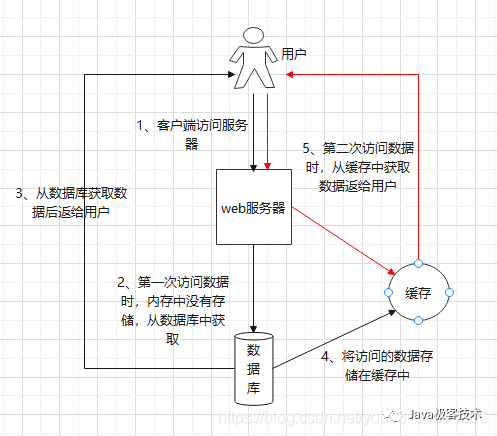

缓存技术被认为是减轻服务器负载、降低网络拥塞、增强Web可扩展性的有效途径之一,其基本思想是利用客户访问的时间局部性(Temproral Locality)原理, 将客户访问过的内容在Cache

2023-10-08 14:07:17 300

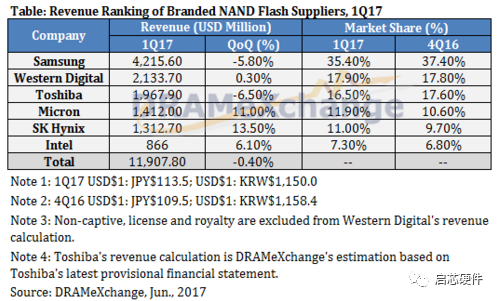

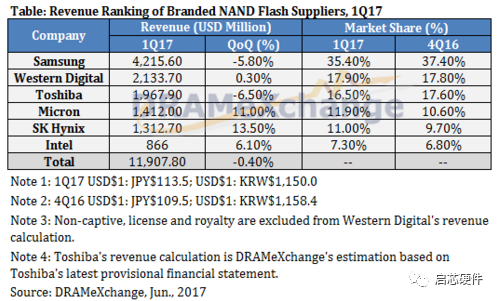

300 目前,NOR FLASH和NAND FLASH是市场上主要的非易失性闪存技术,但是据我了解,还是有很多工程师分不清NAND FLASH与NOR FLASH。

2023-10-01 14:05:00 468

468

一、摘要 说到缓存,面试官基本上会绕不开以下几个话题! 项目中哪些地方用到了缓存?为什么要使用缓存?怎么使用它的?引入缓存后会带来哪些问题? 这些问题,基本上是互联网公司面试时必问的一些问题,如果

2023-09-30 15:29:00 338

338

电子发烧友网站提供《管理基于Cortex-M7的MCU的高速缓存一致性.pdf》资料免费下载

2023-09-25 10:11:48 0

0 电子发烧友网站提供《利用MPLAB Harmony v3在Cortex-M7(SAM S70/E70/V70/V71)MCU上创建不可高速缓存的存储区.pdf》资料免费下载

2023-09-20 11:50:46 0

0 电子发烧友网站提供《利用MPLAB Harmony v3在Cortex-M7 MCU上在运行时使用高速缓存维护操作处理高速缓存一致性问题.pdf》资料免费下载

2023-09-20 11:40:24 0

0 电子发烧友网站提供《使用MPLAB Harmony v3基于PIC32MZ MCU在运行时使用高速缓存维护操作处理高速缓存一致性问题.pdf》资料免费下载

2023-09-19 16:28:10 0

0 STM32MP151A/D器件基于高性能ARM®Cortex®-A7 32位RISC内核,运行频率高达800 MHz。

Cortex-A7处理器包括一个32K字节的一级指令高速缓存、一个32K字节

2023-09-13 07:23:32

片上闪存特性和系统框图

存储空间组织架构

用户闪存

系统闪存

OTP

选项字节

闪存读接口

等待周期

指令预取

指令高速缓存

数据高速缓存

擦除和编程操作

读保护和写保护

STM32F2和STM32F1的闪存特性比较

2023-09-13 07:10:38

什么是高速缓存?• 高速存储器块,包含地址信息(通常称作TAG)和相关联的数据。• 目的是提高对存储器的平均访问速度• 高速缓存的应用基于下面两个程序的局部性 :• 空间局部性:如果一个存储器的位置

2023-09-07 08:22:51

1.具有双发布功能的高性能6级流水线(每个时钟周期最多执行两条指令)。

2.作为系统总线的64位AXI总线接口。

3.可选的指令高速缓存(4至64KB)和数据高速缓存(4至64KB),每个高速

2023-09-04 06:28:56

®v8.3-A扩展中引入的加载获取(LDAPR)指令·ARM®v8.4-A扩展中引入的Dot产品支持说明。

·EL1和EL0高速缓存控制的陷阱、支持Spectre变体4软件缓解的PSTATE SSB

2023-08-29 08:05:54

)指令以及Armv8.4-A扩展中引入的点积指令。

Cortex-A77内核具有1级(L1)内存系统和专用的集成2级(L2)高速缓存。

它还包括一个超标量、可变长度、无序的管道。

Cortex-A77

2023-08-29 07:51:54

就是防止ICE读取MCU flash中的代码的保护,手册上怎么找不到呢?

2023-08-28 08:20:39

和设备放置·可选的系统级高速缓存(SLC)。

有关SLC存储系统功能的更多信息,请参阅第867页的6.1关于SLC存储系统。

CMN-650支持ARM®AMBA®5 CHI版本D,包括以下功能:

·内存系统性能资源分区和监控(MPAM)·具有两部分响应的永久缓存维护操作(PCMO)

2023-08-25 07:49:25

受影响的ARM CPU上,建议的缓解措施包括在转换到需要保护以前的执行上下文的执行上下文时,使部分或全部分支预测器缓存失效。

有关术语执行上下文的定义,请参见第1.2节。

CVE-2018-3639,也

2023-08-25 07:36:27

)指令以及Armv8.4-A扩展中引入的点积指令。

Cortex-A77内核具有1级(L1)内存系统和专用的集成2级(L2)高速缓存。

它还包括一个超标量、可变长度、无序的管道。

Cortex-A77

2023-08-24 07:30:56

电子发烧友网站提供《LSI MegaRAID CacheVault技术工具.pdf》资料免费下载

2023-08-23 14:22:59 0

0 电子发烧友网站提供《CacheVault技术(CVM02 CVPM02和CVPM05)产品介绍.pdf》资料免费下载

2023-08-23 09:23:55 0

0 电子发烧友网站提供《MySQL服务器优化LSI MegaRAID CacheCade Pro 2.0读写缓存软件和固态硬盘(SSD).pdf》资料免费下载

2023-08-21 14:19:00 0

0 CPU高速缓存集成于CPU的内部,其是CPU可以高效运行的成分之一,本文围绕下面三个话题来讲解CPU缓存的作用

2023-08-21 12:17:35 793

793

电子发烧友网站提供《LSI SAS 9207-4i4e 8端口、6Gb/s SAS+SATA转PCI高速主机总线适配器.pdf》资料免费下载

2023-08-21 11:05:21 4

4 Cortex-A7 MPCore处理器是一款实现ARMv7-A架构的高性能、低功耗处理器。

Cortex-A7 MPCore处理器在带有一级高速缓存子系统、可选集成GIC和可选二级高速缓存控制器的单个多处理器设备中具有一到四个处理器

2023-08-18 07:25:18

吞吐量的Thumb-2技术。

该流水线具有双重算术逻辑单元(ALU),具有双重指令发布,以有效地利用其他资源,例如寄存器堆。

该处理器在具有最多两个处理器的群集中具有1级(L1)数据高速缓存一致性

2023-08-18 06:34:29

为了有效利用其他资源,例如寄存器文件,实现了有限的双指令发布。

提供硬件加速器一致性端口(ACP)以减少在与其他主机共享存储器时对缓慢的软件高速缓存维护操作的要求。

通过中断和重新启动加载存储多条指令

2023-08-18 06:09:34

Neoverse N1处理器集群。

该系统通过以下方式在高速缓存一致性加速器互连(CCIX)协议的背景下演示ARM技术:

·在N1 SoC和加速卡之间运行一致的流量。

·两个N1 SoC之间的连贯通信。

·支持开发支持CCIX的FPGA加速器。

2023-08-17 08:14:26

(SB)、所有内核以及内核之间共享的逻辑。

共享逻辑包括CPU桥(CPU侧)(CBC)、L2高速缓存,以及维护核心中的高速缓存与L2高速缓存和低延迟RAM(LLRAM)存储器之间的一致性的一致性逻辑

2023-08-17 08:02:29

Cortex-A8处理器是一款高性能、低功耗、高速缓存的应用程序处理器,可提供完整的虚拟内存功能。

该处理器的功能包括:

·完全实现ARM体系结构v7-A指令集·具有高级可扩展接口(AXI)的可配

2023-08-17 07:43:12

Cortex-A5处理器是一款高性能、低功耗的ARM宏单元,具有提供完整虚拟内存功能的一级高速缓存子系统。

Cortex-A5处理器实现了ARMv7架构,并在Jazelle状态下运行32位ARM指令、16位和32位Thumb指令以及8位JAVA™字节码

2023-08-17 07:16:41

执行模式将嵌入式内存内容转储到调试器,使其适用于芯片启动和调查软件故障,如高速缓存一致性错误。

它允许快速测试内存和内存保护逻辑。

因此,MBIST事务是使用IP核时钟连续执行的,因此,可以通过以全功能

2023-08-17 07:10:53

Cortex-A17 MPCore处理器是一款高性能、低功耗的处理器,采用ARMv7架构。

Cortex-A17 MPCore处理器在带有L1和L2高速缓存子系统的单个多处理器设备中具有一到四个处理器。

2023-08-17 07:06:31

Cortex-A9处理器是一款高性能、低功耗的ARM宏单元,具有提供完整虚拟内存功能的一级高速缓存子系统。

Cortex-A9处理器实现ARMv7-A架构,并在Jazelle状态下运行32位ARM

2023-08-17 06:53:00

电子发烧友网站提供《理解CacheVault模块系统工程说明.pdf》资料免费下载

2023-08-16 15:45:54 0

0 在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有四个Cortex-A32处理器可用,该监听控制单元维护L1和L2数据高速缓存一致性。

Cortex-A32处理器支持

2023-08-16 06:54:59

电子发烧友网站提供《MegaRAID CacheVault Flash模块02快速安装指南.pdf》资料免费下载

2023-08-15 10:31:35 0

0 在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有四个Cortex-A35处理器可用,该监听控制单元维护L1和L2数据高速缓存一致性。

Cortex-A35处理器支持

2023-08-12 07:39:00

在多处理器配置中,在监听控制单元(SCU)的控制下,高速缓存相关群集中最多有八个处理器可用,该监听控制单元维护L1、L2和L3数据高速缓存一致性。

本节提供周期模型与硬件的功能比较的摘要,以及周期模型的性能和准确性

2023-08-12 07:30:35

的电源、性能和面积(PPA)目标和其他关键要求。

RD-V2提供以下功能:

·32个MP1 ARMv9.0-A ARM®Neoverse™V2内核,支持直接连接和2MB专用,

每个核心的专用二级高速缓存

2023-08-11 07:54:59

电子发烧友网站提供《优化数据库性能使用LSI MegaRAID CacheCade Pro 2.0读/写缓存软件.pdf》资料免费下载

2023-08-10 17:38:15 0

0 电子发烧友网站提供《MegaRAID CacheVault电源模块02快速安装指南.pdf》资料免费下载

2023-08-09 10:35:22 0

0 Cortex®-A510是高效内核。

Cortex®-A510内核在称为联合体的模块中实施,该模块最多包含两个内核。在双核复合体中,向量处理单元(VPU)、L2转换后备缓冲器(TLB)和L2高速缓存逻辑在核心之间共享。

2023-08-09 07:50:45

电子发烧友网站提供《Broadcom CacheVault功率模块02和CacheVault功率模块05入门指南.pdf》资料免费下载

2023-08-08 09:16:51 0

0 )AHB(高级高性能总线)接口。它是的成员ARM9E-S Thumb®高性能32位片上系统(SoC)系列处理器,它非常适合广泛的嵌入式应用程序。的大小指令和数据高速缓存以及指令和数据SRAM是单独

2023-08-08 07:33:30

电子发烧友网站提供《LSI SAS 9200-8e高速主机总线适配器产品介绍.pdf》资料免费下载

2023-08-07 09:55:15 0

0 ARM946E-S™ 是一个可合成的宏小区,结合了ARM9E-S™ 带指令和数据高速缓存的处理器核心、带保护单元的紧密耦合指令和数据SRAM存储器、写缓冲区和AMBA™ (高级微处理器总线体系结构

2023-08-02 17:50:31

CCI-400将互连和一致性功能组合到一个模块中。它支持最多可连接两个ACE主机,例如:

•Cortex®-A7处理器。

•Cortex-A15处理器。

•Cortex-A17处理器。

•Cortex-A53处理器。

•Cortex-A57处理器。

CCI-400还支持多达三个ACE Lite主机,例如ARM Mali™-T600系列图形处理器单元(GPU)。

在所有这些接口上都有可选的DVM消息支持,以管理分布式内存管理单元(MMU),例如CoreLink MMU-400。这些可以通信通过具有多达三个ACE Lite从机的CCI-400。

硬件管理的一致性可以通过以下方式提高系统性能并降低系统功耗共享片上数据。管理一致性有以下好处:

•减少外部存储器访问。

•减少软件开销。

2023-08-02 17:33:01

高性能和高性能之间进行权衡代码密度。ARM922T处理器是哈佛高速缓存体系结构处理器,其目标是全内存管理、高性能和低功率是至关重要的。此设计中的独立指令和数据缓存每个大小为8KB,具有8字线长度。ARM922T实现了增强型ARM体系结构v4 MMU为指令和数据地址

2023-08-02 15:44:14

:

•用于增强操作系统安全性的TrustZone架构•专为高性能系统设计的主、从和外围AXI/AMBA接口•智能能源管理器(IEM)支持。

高速缓存控制器是一个统一的、物理寻址的、物理标记的8路高速缓存。您可

2023-08-02 15:09:49

当中央处理器(CPU)产生大量内存流量时,添加片上二级缓存(也称为二级缓存,L2CC)是提高计算机系统性能的公认方法。根据定义,二级缓存假定存在与CPU紧密耦合或内部的一级缓存或主缓存。

2023-08-02 13:11:45

高速缓存体系结构处理器,适用于全内存管理、高性能和低功耗至关重要的多程序应用。此设计中的独立指令和数据缓存大小分别为16KB,具有8字线长度。ARM920T处理器实现了一个增强的ARM架构v4-MMU,为

2023-08-02 13:05:00

ARM720T是一款通用的32位微处理器,具有8KB的高速缓存、扩大的写入缓冲区和内存管理单元(MMU),组合在一个芯片中。ARM720T中的CPU是ARM7TDMI。ARM720T是与ARM处理器

2023-08-02 11:36:56

时执行关键异常处理程序。

•每个指令和数据CPU接口的紧密耦合SRAM。指令和数据SRAM的大小都是实现者可配置的。

•指令和数据缓存。该设计可以很容易地修改,以允许从4K字节到1M字节的任何高速缓存组合

2023-08-02 09:41:21

。

Cortex-A720核心在DSU-120 DynamIQ中实现™ 簇它连接到DynamIQ™ 共享单元-120,其表现为具有L3高速缓存和窥探控制的完全互连。

这种连接配置也用于具有不同类型内核的系统中,其中Cortex-A720核心是性能均衡的核心。

2023-08-02 08:55:50

的ARM高速缓存处理器宏单元,提供完整的虚拟内存功能。ARM1020T设计用于运行复杂的操作系统,如JavaOS、Linux、Microsoft WindowsCE、NetBSD和Symbian

2023-08-02 08:33:42

MBIST是测试嵌入式存储器的行业标准方法。MBIST通过根据测试算法执行对存储器的读取和写入序列来工作。存在许多行业标准的测试算法。MBIST控制器生成正确的读取和写入序列。ARM L210 MBIST控制器用于与ARM L210一起执行二级高速缓存RAM的内存测试。

2023-08-02 08:07:10

内核是高效内核。

Cortex-A520内核在一个名为complex的块中实现,该块最多包含两个核心。在双核复合体中,矢量处理单元(VPU)、L2翻译Lookaside缓冲区(TLB)和L2高速缓存逻辑在核心之间共享。

下图显示了双核配置的示例。

2023-08-02 07:05:57

电子发烧友网站提供《STM32F7技术--高速缓存.pdf》资料免费下载

2023-08-01 15:18:55 0

0 电子发烧友网站提供《在Readme文件使用MegaRAID Cachevault选项.zip》资料免费下载

2023-07-27 16:42:47 0

0 ,用于构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32590集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指

2023-07-14 14:33:26

构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32591集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指令

2023-07-14 14:09:44

构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32592集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指令

2023-07-14 14:04:11

缓存服务器是什么?缓存服务器是专用网络服务器或充当在本地保存网页或其他互联网内容的服务器的服务。通过将以前请求的信息放入临时存储(或高速缓存)中,高速缓存服务器既可以加快数据访问速度,又可以减少

2023-07-07 17:48:59 353

353 Chiplet技术和NoC技术目前已经成为解决摩尔定律无法延续的一种重要方法,现在的CPU芯片对外的接口已经不是普通的IO了,而是一套标准的NoC总线接口,可以与专门的NoC总线DIE(暂称为IO

2023-06-29 09:56:59 519

519

SPI Flash为Slave (从设备),可将应用程序放在外部内存SPI Flash,要执行放在外部SPI Flash的程序时,硬件会透过SPI Flash控制单元将应用程序读取至新唐专为M480 SPI Flash 设计的32KB高速缓存执行应用程序。

2023-06-15 07:11:48

本地缓存 :应用中的缓存组件,缓存组件和应用在同一进程中,缓存的读写非常快,没有网络开销。但各应用或集群的各节点都需要维护自己的单独缓存,无法共享缓存。

2023-06-11 15:12:21 556

556

使用 TI SysBIOS,您可以在其中将高速缓存的一部分定义为具有特殊地址的快速 RAM。然后固件可以考虑将代码或变量放在那里,从而大大加快算法的速度。

我不知道 i.MX8mm 是否一般提供,我也不知道如何在构建嵌入式 Linux 时配置它。

2023-05-18 11:48:08

微机保护装置由硬件和软件两部分组成,其中硬件主要包括以下几个部分:

1. 微处理器:微机保护装置使用的微处理器通常会配置为高性能、低功耗、支持多核心、高速缓存的处理器,以保证系统的稳定性

2023-04-21 18:12:26 2998

2998 )的缩写。是 Motorola 公司推出的一种同步串行接口技术,是一种高速的,全双工,同步的通信总线。SPI 支持以三线同步串行模式进行数据交互,加上片选线支持硬件切换主从模式,支持以单根数据线通讯。

2023-04-17 15:30:56

LSI1013LT1G

2023-03-29 21:39:10

TBU®高速保护器

2023-03-28 18:13:42

高速DAP仿真器 BURNER

2023-03-28 13:06:20

沟道高速IGBT及场阻技术

2023-03-28 12:56:28

高速线路的2线ESD保护

2023-03-24 13:58:22

电子发烧友App

电子发烧友App

评论