所谓退耦,既防止前后电路网络电流大小变化时,在供电电路中所形成的电流冲动对网络的正常工作产生影响。换言之,退耦电路能够有效的消除电路网络之间的寄生耦合。

用在退耦电路中的电容称为退耦电容也叫去耦电容,退耦电容并接于电路正负极之间,可防止电路通过电源形成的正反馈通路而引起的寄生振荡。所谓退耦,即防止前后电路电流大小变化时,在供电电路中所形成的电流波动对电路的正常工作产生影响,换言之,退耦电路能够有效地消除电路之间的寄生耦合。

退耦滤波电容的取值通常为47~200μF,退耦压差越大时,电容的取值应越大。所谓退耦压差指前后电路网络工作电压之差。

什么是退耦?

退耦(Decouple),最早用于多级电路中,为保证前后级间传递信号而不互相影响各级静态工作点的而采取的措施。在电源中退耦表示,当芯片内部进行开关动作或输出发生变化时,需要瞬时从电源线上抽取较大电流,该瞬时的大电流可能导致电源线上电压的降低,从而引起对自身和其他器件的干扰。

为了减少这种干扰,需要在芯片附近设置一个储电的“小水池”以提供这种瞬时的大电流能力。 在电源电路中,旁路和退耦都是为了减少电源噪声。旁路主要是为了减少电源上的噪声对器件本身的干扰(自我保护);退耦是为了减少器件产生的噪声对电源的干扰(家丑不外扬)。

有人说退耦是针对低频、旁路是针对高频,我认为这样说是不准确的,高速芯片内部开关操作可能高达上GHz,由此引起对电源线的干扰明显已经不属于低频的范围,为此目的的退耦电容同样需要有很好的高频特性。本文以下讨论中并不刻意区分退耦和旁路,认为都是为了滤除噪声,而不管该噪声的来源。

简单说明了旁路和退耦之后,我们来看看芯片工作时是怎样在电源线上产生干扰的。我们建立一个简单的IO Buffer模型,输出采用图腾柱IO驱动电路,由两个互补MOS管组成的输出级驱动一个带有串联源端匹配电阻的传输线(传输线阻抗为Z0)。

为了做成纯文档的格式,尽量采用文字说明,不不采用图片,这样给理解带来一定的困难,看官们见笑了。设电源引脚和地引脚的封装电感和引线电感之和分别为: Lv和Lg。两个互补的MOS管(接地的NMOS和接电源的PMOS)简单作为开关使用。

假设初始时刻传输线上各点的电压和电流均为零,在某一时刻器件将驱动传输线为高电平,这时候器件就需要从电源管脚吸收电流。在时间T1,使PMOS管导通,电流从 PCB板上的VCC流入,流经封装电感Lv,跨越PMOS管,串联终端电阻,然后流入传输线,输出电流幅度为VCC/(2×Z0)。

电流在传输线网络上持续一个完整的返回(Round-Trip)时间,在时间T2结束。之后整个传输线处于电荷充满状态,不需要额外流入电流来维持。当电流瞬间涌过封装电感 Lv时,将在芯片内部的电源提供点产生电压被拉低的扰动。该扰动在电源中被称之为同步开关噪声(SSN,Simultaneous Switching Noise;SSO,Simultaneous Switching Output Noise)或Delta I噪声。

在时间T3,关闭PMOS管,这一动作不会导致脉冲噪声的产生,因为在此之前PMOS管一直处于打开状态且没有电流流过的。同时打开NMOS管,这时传输线、地平面、封装电感Lg以及NMOS管形成一回路,有瞬间电流流过开关B,这样在芯片内部的地结点处产生参考电平点被抬高的扰动。该扰动在电源系统中被称之为地弹噪声(Ground Bounce,我个人读着地tan)。

实际电源系统中存在芯片引脚、PCB走线、电源层、底层等任何互连线都存在一定电感值,因此上面就IC级分析的SSN和地弹噪声在进行Board Level分析时,以同样的方式存在,而不仅仅局限于芯片内部。就整个电源分布系统来说(Power Distribute System)来说,这就是所谓的电源电压塌陷噪声。

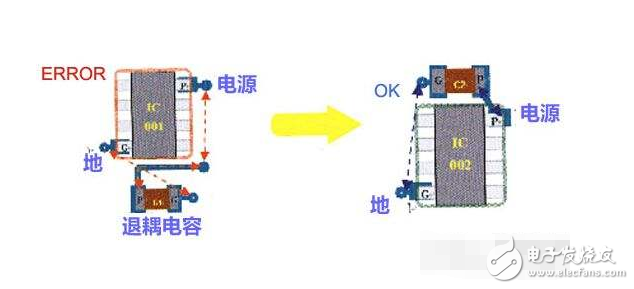

因为芯片输出的开关操作以及芯片内部的操作,需要瞬时的从电源抽取较大的电流,而电源特性来说不能快速响应该电流变化,高速开关电源开关频率也仅有MHz量级。为了保证芯片附近电源线上的电压不至于因为SSN和地弹噪声降低超过器件手册规定的容限,这就需要在芯片附近为高速电流需求提供一个储能电容,这就是我们所要的退耦电容。

如果电容是理想的电容,选用越大的电容当然越好了,因为越大电容越大,瞬时提供电量的能力越强,由此引起的电源轨道塌陷的值越低,电压值越稳定。但是,实际的电容并不是理想器件,因为材料、封装等方面的影响,具备有电感、电阻等附加特性;尤其是在高频环境中更表现的更像电感的电气特性。我们都知道实际电容的模型简单的以电容、电阻和电感建立。除电容的容量C以外,还包括以下寄生参数:

1、等效串联电阻ESR(Resr):电容器的等效串联电阻是由电容器的引脚电阻与电容器两个极板的等效电阻相串联构成的。当有大的交流电流通过电容器,Resr使电容器消耗能量(从而产生损耗),由此电容中常用用损耗因子表示该参数。

2、等效串联电感ESL(Lesl):电容器的等效串联电感是由电容器的引脚电感与电容器两个极板的等效电感串联构成的。

3、等效并联电阻EPR Rp :就是我们通常所说的电容器泄漏电阻,在交流耦合应用、存储应用(例如模拟积分器和采样保持器)以及当电容器用于高阻抗电路时,Rp是一项重要参数,理想电容器中的电荷应该只随外部电流变化。然而实际电容器中的Rp使电荷以RC时间常数决定的速度缓慢泄放。 还是两个参数RDA、CDA 也是电容的分布参数,但在实际的应该中影响比较小,这就省了吧。所以电容重要分布参数的有三个:ESR、ESL、EPR。其中最重要的是ESR、 ESL,实际在分析电容模型的时候一般只用RLC简化模型,即分析电容的C、ESR、ESL。因为寄生参数的影响,尤其是ESL的影响,实际电容的频率特性表现出阻抗和频率成“V”字形的曲线,低频时随频率的升高,电容阻抗降低;当到最低点时,电容阻抗等于ESR;之后随频率的升高,阻抗增加,表现出电感特性(归功于ESL)。因此对电容的选择需要考虑的不仅仅是容值,还需要综合考虑其他因素。包括: 1、电容容值;2、电介质材料;3、电容的几何尺寸和放置位置。

所有考虑的出发点都是为了降低电源地之间的感抗(满足电源最大容抗的条件下),在有瞬时大电流流过电源系统时,不至于产生大的噪声干扰芯片的电源地引脚。选用常见的有两种方法计算所需的电容: 简单方法:由输出驱动的变化计算所需退耦电容的大小;

复杂方法:由电源系统所允许的最大的感抗计算退耦电容的大小。

我们假设一个模型,在一个Vcc=3.3V的SRAM系统中,有36根输出数据线,单根数据线的负载为Cload=30pF(相当的大了),输出驱动需要在Tr=2ns(上升时间)内将负载从0V驱动到3.3V,该芯片资料里规定的电源电压要求是3.3V+0.3V/-0.165V。

可以看出在SRAM的输出同时从0V上升到3.3V时,从电源系统抽取的电流最大,我们选择此时计算所需的退耦电容量。我们采用第一种计算方法进行计算,单根数据线所需要的电流大小为: I=Cload×(dV/dt)=30pF×(3V/2ns)=45mA;

36根数据线同时翻转时的电流大小为Itot=45mA×36=1.62A。芯片允许的供电电压降为0.165V,假设我们允许该芯片在电源线上因为SSN引入的噪声为50mV,那么所需要的电容退耦电容为: C=I×(dt/dV)=1.62A×(2ns/50mV)=64nF;

从标准容值表中选用两个34nF的电容进行并联以完成该值,正如上面提到的退耦电容的选择在实际中并不是越大越好,因为越大的电容具有更大的封装,而更大的封装可能引入更大的ESL,ESL的存在会引起在IC引脚处的电压抖动(Glitching),这个可以通过V=L×(di/dt)公式来说明,常见贴片电容的L大约是1.5nH,那么V=1.5nH×(1.62A/2ns)=1.2V,考虑整个Bypass回路的等效电感之后,实际电路中glitch 会小于该值。通过前人做的一些仿真的和经验的数据来看,退耦电容上的Glitch与同时驱动的总线数量有很大关系。

因为ESL在高频时觉得了电源线上的电流提供能力,我们采用第二种方法再次计算所需的退耦电容量。这中方法是从Board Level考虑单板,即从Bypass Loop的总的感抗角度进行电容的计算和选择,因此更具有现实意义,当然需要考虑的因素也就越多,实际问题的解决总是这样,需要一些折中,需要一点妥协。

同样使用上面的假设,电源系统的总的感抗最大: Xmax=(dV/dI)=0.05/1.62=31m欧;

在此,需要说明我们引入的去耦电容是为了去除比电源的去耦电容没有滤除的更高频率的噪声,例如在电路板级参数中串联电感约为Lserial=5nH,那么电源的退耦频率:

Fbypass=Xmax/(2pi×Lserial)=982KHz,这就是电源本身的滤波频率,当频率高于此频率时,电源电路的退耦电路不起作用,需要引入芯片的退耦电容进行滤波。另外引入另外一个参数——转折点频率Fknee,该频率决定了数字电路中主要的能量分布,高于该频率的分量认为对数字电路的上升沿和下降沿变化没有贡献。在High-Speed Digital Design:A Hand Book of Black Magic这本书的第一章就详细的讨论了该问题,在此不进行详细说明。只是引入其中推倒的公式: Fknee=(1/2×Tr)=250MHz,其中Tr=2ns;

可见Fknee远远大于Fbypass,5nH的串联电感肯定是不行了。那么计算: Ltot=Xmax/(2pi×Fknee)=(Xmax×Tr/pi)=19.7pH;

如前面提到的常见的贴片电容的串联电感在1.5nH左右,所需要的电容个数是:

N=(Lserial/Ltot)=76个,另外当频率降到Fbypass的时候,也应该满足板级容抗需要即: Carray=(1/(2pi×Fbypass×Xmax))=5.23uF; Celement=Carray/N=69nF;

哇噻,真不是一个小数目啊,这么多啊!如果单板上还有其他器件同时动作,那么需要更多的电容呢!如果布不下,只能选择其他具有更小电感值的电容了。

电容选择上都采用的MLCC的电容进行退耦,常见的MLCC的电容因为介质的不同可以进行不同的分类,可以分成NPO的第一类介质,X7R和Z5V等的第二、三类介质。EIA对第二、三类介质使用三个字母,按照电容值和温度之间关系详细分类为: 第一个数字表示下限类别温度: X:-55度;Y:-30度;Z:+10度 第二个数字表示上限温度:

4:+65度;5:+85度;6:105度;7:125度;8:150度; 第三个数字表示25度容量误差:

P:+10%/-10%;R:+15%/-15%;S:+22%/-22%; T:+22%/-33%;U:+22%/-56%;V:+22%/-82%

例如我们常见的Z5V,表示工作温度是10度~85度,标称容量偏差+22%/-82%,就这玩意儿我们还大用特用啊。

介质性能好的电容容量做不大,容量大的介质常量不好,生活啊,你怎么总是这么矛盾啊!尤其重要的一点是MLCC电容提供的电容值都是指静电容量,表示电容在很低的电压下测试得到的电容量,当电容的两端的直流电压在不超过电容耐压下加大时电容量将急剧下降,例如在某耐压16V 的MLCC电容的测试数据中有:

0V--》100%,8V——》86%,12V——》68%,16V——55%。