将PIN二极管用做衰减元件时,PIN二极管具有比等效的GaAs MESFETs更高的线性度,通过使用具有厚I层及低介质张弛频率(fdr)的多个PIN二极管就可以将信号畸变减小到最低程度。在Avago公司PIN二极管产品线中HSMP-381x系列产品的I层最厚。在低衰减状态,大部分RF能量仅仅是从输入端传输到输出端而已。不过在高衰减状态,更多的RF能量被倾入衰减器,会使信号失真度上升。当Vc接近0时,几乎没有电流流过两个串联的二极管,它们接近于零偏压状态,其结电容将随RF电压同步变化,幸运的是,由于两个二极管是反向串联的,所以可以抑制由受RF调制的电容所产生的某些失真或畸变。由于封装的两个反串二极管具有完全互相匹配的特性,因此可以得到最佳的失真抑制能力。

Pi衰减器的相位偏移随衰减值而变化。总的相位偏移接近90度,在三个相隔较远的工作频率点(100、900和1800 MHz)测试时此相位偏移表现相当稳定。

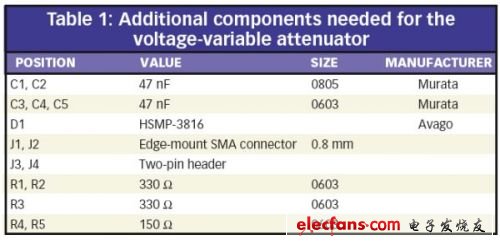

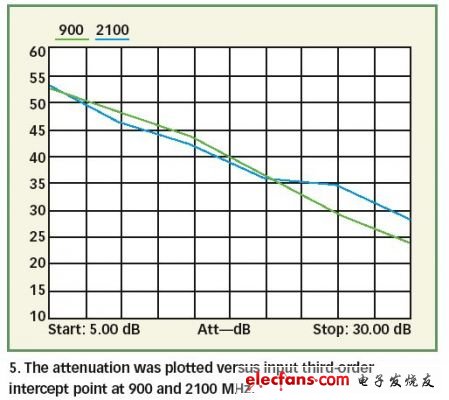

图1所示为π衰减电路的示意电路图。图2的左边为π衰减器的PCB布局,右边为元件布置。表1中给出了所需要的元件(包括四元二极管)。图3、4、5给出的成品π衰减器测试性能的样本。

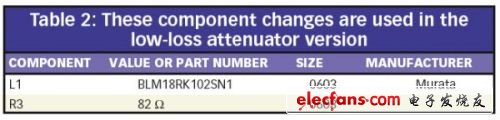

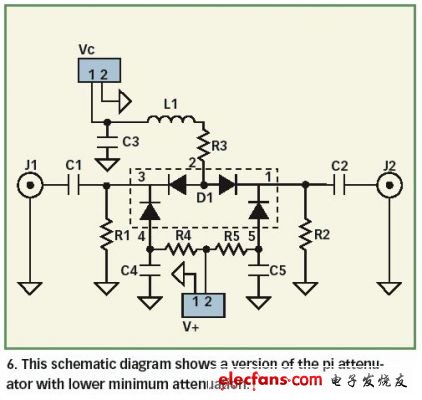

增加通过串联二极管的电流可以降低衰减下限。将控制电压保持在最大值5V,减小电阻R3的阻值就可以增大偏移电压,这可以通过给阻断RF的电阻R3(表2)串联一个表面贴装铁酸盐珠状电感而实现。在整个频率范围内,与传统的瓷芯多层片状电感相比,这种铁酸盐珠状电感具有更高的阻抗。图6给出了低衰减下限衰减电路的示意图,图7中给出了在Vc=5V的条件下与标准衰减电路的比较结果。

为了建立π衰减器的性能模型以便于进一步分析,安捷伦?司的高级设计系统(ADS)计算机辅助工程(CAE)软件为工程师们提供了模拟四元二极管π衰减器性能的技术支持范例。相应文件可以从www.edasupportweb.soco.agilent.com.的Agilent Eesof知识中心的“Examples”部分下载。

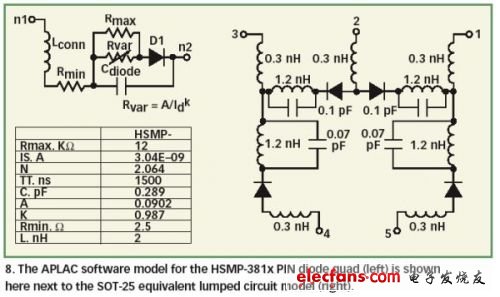

另外,包含在高频建模工具APLAC CAE软件包(www.aplac.com)中的PIN二极管模型也可以预测在给定正向偏移的条件下RF阻值。图8的左边给出了HSMP-3816 PIN二极管的APLAC模型,将APLAC模型与SOT-25等效电路模型(图8右边)结合在一起,就可以使设计人员在模拟过程中研究分析封装的寄生效应。