此原理图中使用了三个光耦集成芯片,P521,P521*2,P521*4。总共7个光耦

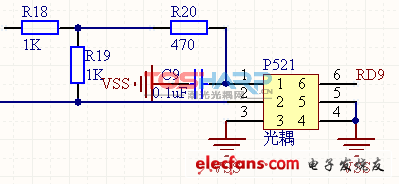

内部电路图如下:

P521的3脚接地,2脚与DI接口连接,测试DCS系统的DO反应时间一脚经过电阻R20,R18后与高电平连接(此处在PCB中没有连接)

电阻R19起到上拉电阻的作用,使得2脚默认电平为高。电容作用未知。

4脚与单片机相连,通过RD9电位的高低,判断是否接收到DI信号。

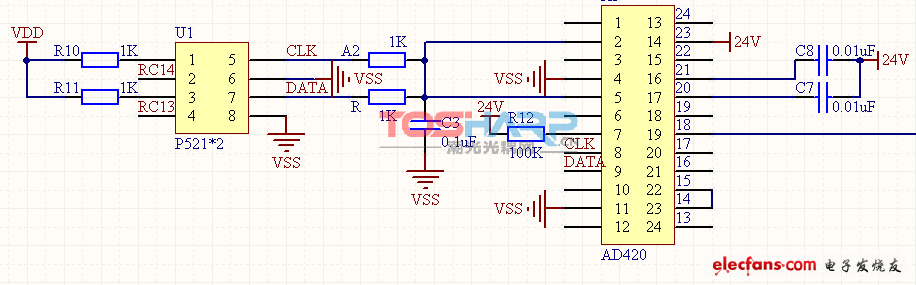

P521*2外围电路如下图,1,3脚被拉高,2,4脚分别与单片机相连,单片机通过2,4脚给出时钟和数据信号,再通过5,7脚传给AD420。AD420的2脚可以提供高电平,电阻A2,R都是上拉电阻。

此光耦芯片应用在AI测试中,电路通过两个光耦来实现AD420的数字数据写入,进而转化为模拟电流输出,并最终接到本设备的AO接口上。

P521*3外围电路如下图,RB1,RB2,RB3,RB4分别与单片机管脚连接,当按下DI测试按键后,RB1~RB4中的某一路信号电平变为低电平,则DO1~DO4中对应的一路线路导通,此时DCS系统接收到DI信号,此系统开始计时,直到测试鼠标按下,则计时停止。

有四路DO通道,在测试时使用哪一路,如何选择?