模块间接口设计不匹配引起的问题

如果没有一个技术能力很强的集成者,往往在模块间容易出现设计上的错误。这种情况是灾难性的,双方都是在需求文件上设计出来的东西,但是由于集成者的问题,这方面往往变成模糊设计或者假定设计,然后就会出现很多问题。

如下:

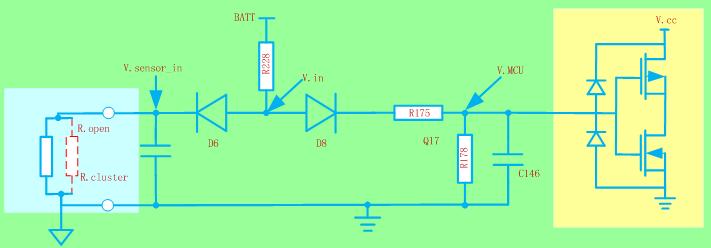

甲方的设计如下,假定输出信号的通断的内阻是变化的,如下:

乙方的实际设计与甲方设想的完全不同,采用OC门做设计,而且加入上拉环节,最致命的还是外部限流电阻。

然后我们看下面的表格:

甲方初始设计:

实际考虑因素:

1.由于OC门的集电极电流增大了,OC门的饱和性受一定影响,Vce电压增大

2.由于地偏移的因素,可能两个电压相差1V

3.由于限流电阻的作用,该电阻和上拉电阻分压造成端口电压抬高

假定限流电阻和上拉电阻相若,因此实际端口电压可能上升至6V,造成了无论OC门的状态,模块读取的信号始终是高电平的状态。

如下:

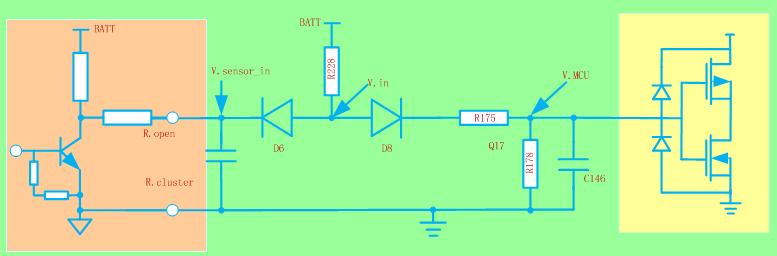

甲方的设计如下,假定输出信号的通断的内阻是变化的,如下:

乙方的实际设计与甲方设想的完全不同,采用OC门做设计,而且加入上拉环节,最致命的还是外部限流电阻。

然后我们看下面的表格:

甲方初始设计:

实际考虑因素:

1.由于OC门的集电极电流增大了,OC门的饱和性受一定影响,Vce电压增大

2.由于地偏移的因素,可能两个电压相差1V

3.由于限流电阻的作用,该电阻和上拉电阻分压造成端口电压抬高

假定限流电阻和上拉电阻相若,因此实际端口电压可能上升至6V,造成了无论OC门的状态,模块读取的信号始终是高电平的状态。