vhdl数码管动态扫描四:8位数码管输出任意数值的显示电路

实验设计注意事项

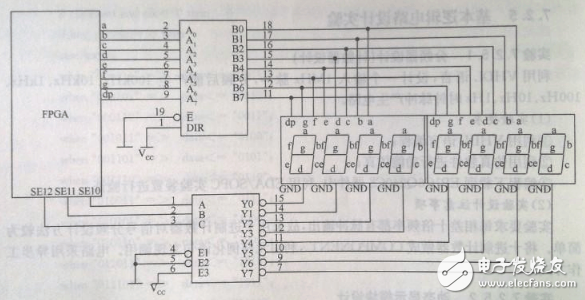

在EDA/SOPC装置中,图示数码管显示采用的是动态扫描方式,即当扫描选通电路74LS138输入为000,(SEL2、SEL1、SEL0为000时,)Y0输出低电平,8个数码管中左边第一个数码管被选通,此时,应在数码管输入端输入相应数据。其中,74LS245起输出驱动作用。

人眼视觉暂留频率在24Hz以上,如果大于该频率,点亮单个七段显示器,看上去能有8个同时显示的效果,而且显示也不闪烁。因此,选通频率要大于24Hz以上。 依据实验装置电路,完成七段LED显示译码器的设计应包含如下电路:

①分频电路:将10MHz脉冲分频到1kHz;

②七段译码电路;

③扫描计数电路:完成模8的计数电路,为扫描选通做准备;

④扫描选通电路:利用分时传输思想,将要显示的数据依次传入数码管显示电路。

VHDL代码

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.std_logic_arith.all;

USE IEEE.std_logic_unsigned.all;

ENTITY xianshi IS

PORT(clk:in std_logic;

smg:out std_logic_vector(7 downto 0);

sel:out std_logic_vector(2 downto 0));

END ENTITY;

ARCHITECTURE func OF xianshi IS

SIGNAL fp,tmp:std_logic;

SIGNAL count:std_logic_vector(9 downto 0);

SIGNAL sl:std_logic_vector(2 downto 0);

BEGIN

PROCESS(clk)

BEGIN

IF(clk‘EVENT AND clk = ’1‘)

THEN IF(count = “1111100111”)

THEN count <= (OTHERS => ’0‘);

tmp <= NOT tmp; ELSE

count <= count + 1; END IF;

END IF; fp <= tmp;

END PROCESS;

PROCESS(fp)

BEGIN

IF(fp’EVENT AND fp = ‘1’)

THEN IF(sl = “111”)

THEN sl <= “000”;

ELSE

sl <= sl + 1; END IF;

END IF;

END PROCESS;

sel <= sl;

PROCESS(sl) BEGIN

CASE sl IS

WHEN “000” => smg <= “01000000”;

WHEN “001” => smg <= “01111001”;

WHEN “010” => smg <= “00100100”;

WHEN “011” => smg <= “00110000”;

WHEN “100” => smg <= “00011001”;

WHEN “101” => smg <= “00010010”;

WHEN “110” => smg <= “00000010”;

WHEN “111” => smg <= “01111000”;

WHEN OTHERS => NULL;

END CASE;

END PROCESS;

END ARCHITECTURE;