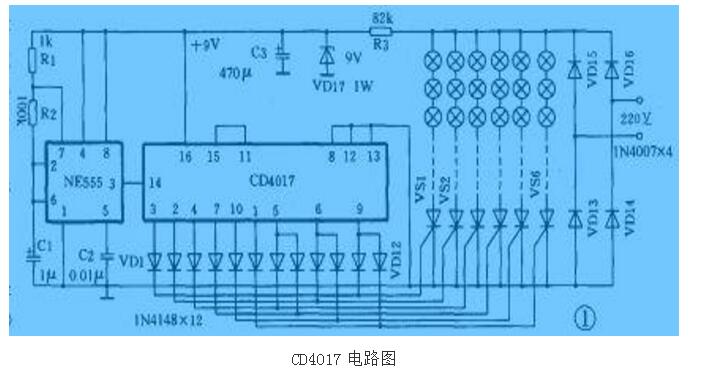

CD4017内部结构图 - cd4017工作原理详解(cd4017引脚图及功能_内部结构及应用电路图)

CD4017内部结构图

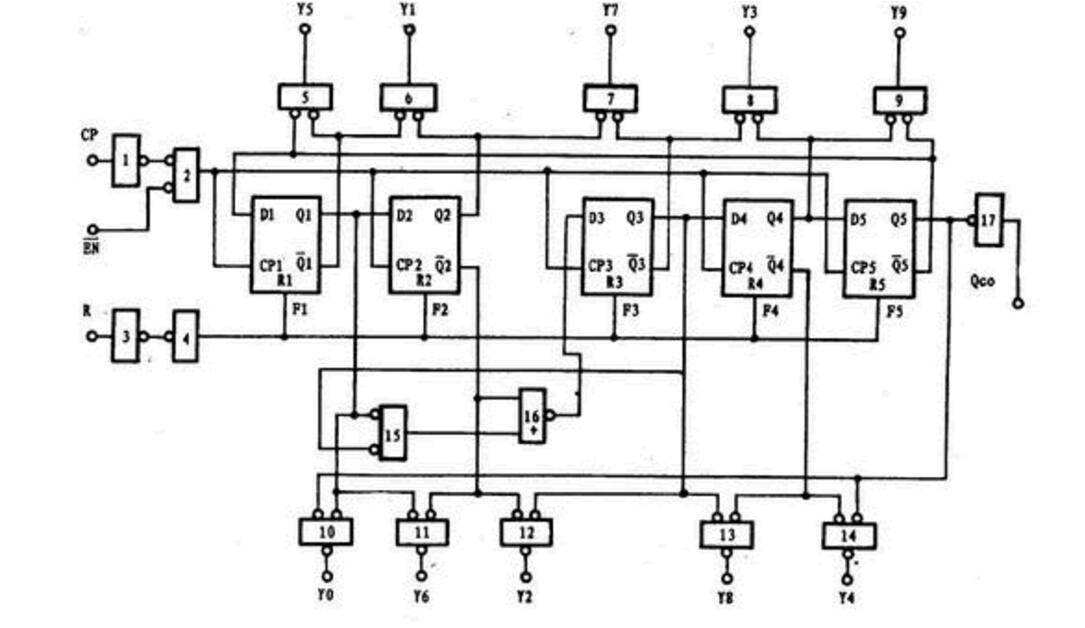

图 2 CD4017 内部逻辑电原理图

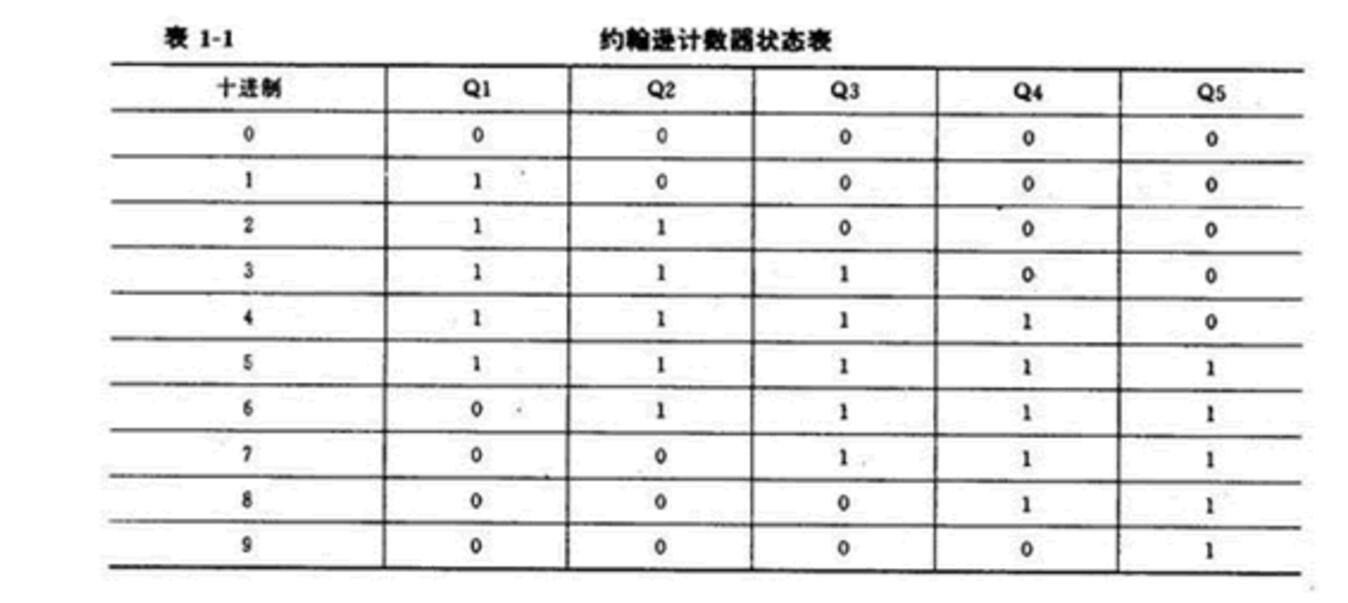

CD4017内部逻辑电原理图如图2所示。它是由十进制计数器电路和时序译码电路两部分组成。其中的D触发器Fl~F5构成了十进制约翰逊计数器,门电路5~14 构成了时序译码电路。约翰逊计数器的结构比较简单.它实质上是一种串行移位寄存器。除了第3个触发器是通过门电路15、16构成的组合逻辑电路作用于F3的D3端以外,其余各级均是将前一级触发器的输出端连接到后一级触发器的输入端D的,计数器最后—级的Q5端连接到第一级的D1端。这种计数器具有编码可靠,工作速度快、译码简单,只需由二输入瑞的与门即可译码,且译码输出无过渡脉冲干扰等特点。通常只有译码选中的那个输出端为高电平,其余输出端均为低电平。约翰逊计数器状态如表1-1所示。

当加上清零脉冲后,Q1~Q5均“0”,由于Q1的数据输入端D1是Q5输出的反码,因此,输入第—个时钟脉冲后,Q1即为“l”,这时Q2-Q5均依次进行移位输出,Ql的输出移至Q2,Q2的输出移至Q3……。如果继续输入脉冲,则Q1为新的Q5,Q2~Q5仍然依次移位输出,这样就得到了表l~l的状态及图l~3的波形

由五级计数单元组成的约翰逊计数器,其输出端可以有32种组合状态,而构成十进制计数器只需10种计数状态,因此,当电路接通电源之后,有可能进入我们所不需要的22种伪码状态。

为了使电路能迅速进入表1~l所列状态,就在第三级计数单元的数据输入端上加接了两级组合逻辑门,使Q2不直接连接D3,而使03由下列关系决定:

D3=Q2(Ql+Q3)

这样做,当电源接通后,不管计数单元出现哪种随机组合,最多经过8个时钟脉冲输入之后,都会自动进入表l~l所列状态。

CD4017有3个输入端:复位清零端R,当在R端加高电平或正脉冲时,计数器清零,在所有输出中,只有对应“0”状态的Q0输出高电平,其余输出均为低电平:时钟输入端CP和CE,其中CP端用于上升沿计数,CE端用于下降沿计数,这两个输入端的内部逻辑电路如图2所示。由图2可见,CP和CE还有互锁的关系,即利用CP计数时,CE端要接低电平:利用CE计数时,CP端要接高电平。反之则形成互锁。

在“R”端加上高电平或正脉冲日子,计数器中各计数单元F1~F5均被置零,计数器为“00000”状态。

CD4017有10个译码输出端Q0~Q9,它仍随时钟脉冲的输入而依次出现高电平,见图3。此外,为了级联方便,还设有进位输出端QC,每输入10个时钟脉冲,就可得到一个进位输出脉冲,所以QC可作为下一级计数器的时钟信号。

从上述分析中可以看出,CD4017(它的基本功能是对“CP”端输入脉冲的个数进行十进制计数,并按照输入脉冲的个数顺序将脉冲分配在Yo—Y9这十个输出端,计满十个数后计数器复零,同时输出—个进位脉冲。我们只要掌握了这些基本功能就能设计出千姿百态的应用电路来。

- 第 1 页:cd4017工作原理详解(cd4017引脚图及功能_内部结构及应用电路图)

- 第 2 页:CD4017内部结构图

- 第 3 页:用三个CD4O17彩灯电路图

本文导航

非常好我支持^.^

(911) 93.3%

不好我反对

(65) 6.7%

相关阅读:

- [电子说] 基于CD4521和CD4017的心电图模拟器电路 2024-06-09

- [电子说] 集成芯片cd4017的功能 2024-03-20

- [电子说] CD4017BD芯片基础介绍 2024-02-01

- [电子说] CD4017 CMOS逻辑芯片简单介绍 2024-02-01

- [电子说] 使用NE555和CD4017制作一个迪斯科LED灯电路 2023-07-05

- [电子说] 基于IC555和CD4017的双色迪斯科灯电路 2023-07-02

- [电子说] 基于CD4017的电子骰子电路 2023-06-29

- [电子说] 基于CD4017构建的简单密码锁电路 2023-06-29

( 发表人:姚远香 )