cd4046简介

cD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

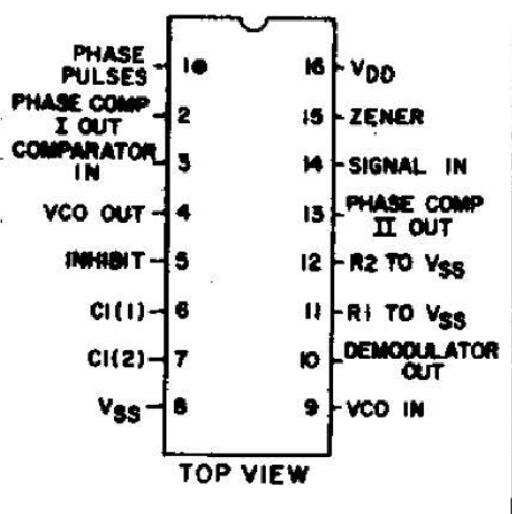

cd4046引脚图及功能

1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

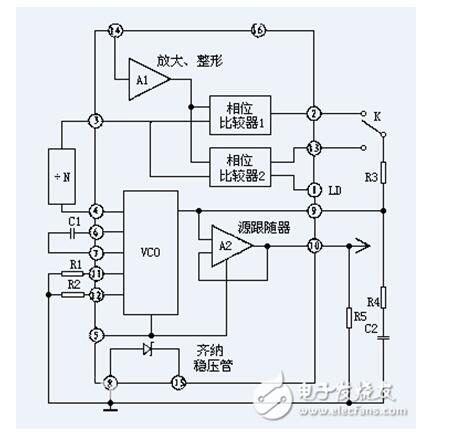

cd4046工作原理

输入信号 Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f2迅速逼近信号频率f1。VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。若开关K拨至13脚,则相位比较器Ⅱ工作,过程与上述相同。

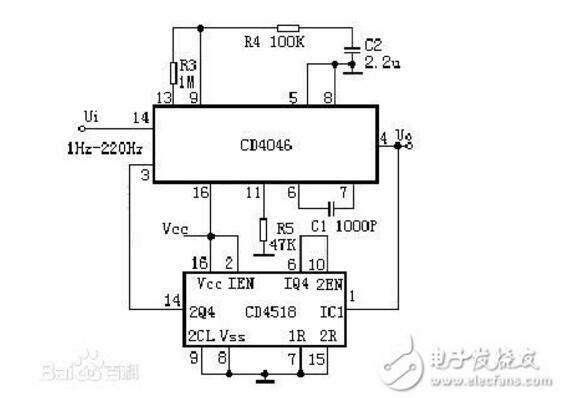

cd4046分频倍频电路设计详解

设计采用锁相环芯片cd4046和分频器cd4518实现,效果良好,cd4046压控振荡输出到分频器cd4518的时钟输入端,经分频后回馈到cd4046的鉴相器输入端,和待倍频的输入信号进行相位比较,得出的相位差经过低通滤波器产生一个控制电压调节压控振荡器的输出振荡频率,当鉴相器的两输入端频率相位一样时(即相位锁定),压控振荡器的输出频率即为倍频和的频率。

注意事项:

1、芯片外围电路参数的选择应严格按照DATASHEET上的要求进行选择。

2、倍频的倍数不能太大,太大的话会造成倍频出来的结果很不稳定。

3、准确选择R1、C1和R2的参数,这三项的参数如果设置不正确将会造成倍频输出不对的结果。