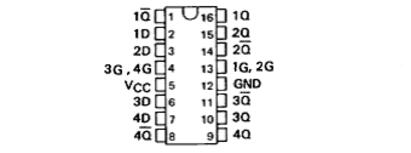

74ls75引脚图

16引脚4路透明D锁存器。当控制端G为高电平时,Q输出跟随D变化。当控制端为低电平时,Q保持原值。 通常用在数据在时钟沿未准备好时来暂存数据。

74ls75功能表

H=高电平L=低电平×=不定

Q0=使能G由高电平转换到

低电平之前Q的电平

说明:这种锁存器最适合作运算单元和输入/输出(或指示)单元之间二进制数据的暂时储存之用。当使能G是高电平时,数据D输入上的信息便传送至Q输出;只要使能保持高,Q输出便随数据输入而变。当使能变为低电平时,跳变时数据输入端的信息将保持在Q输出上,直至使能变成高电平为止。

74ls75推荐工作条件

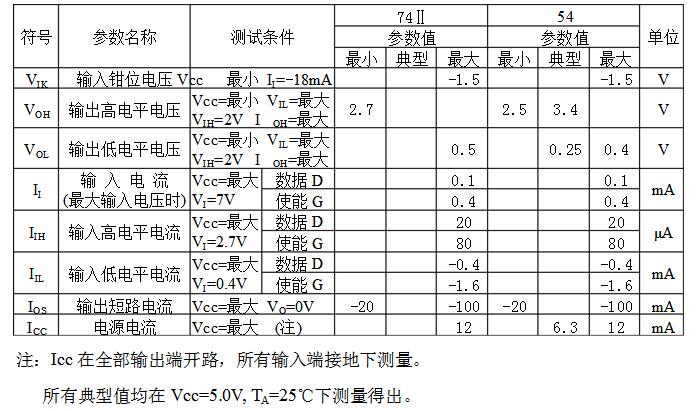

74ls75电气性能

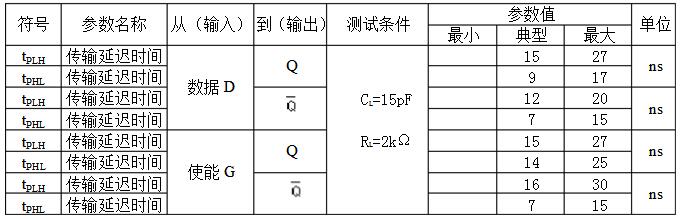

74ls75交流(开关参数)

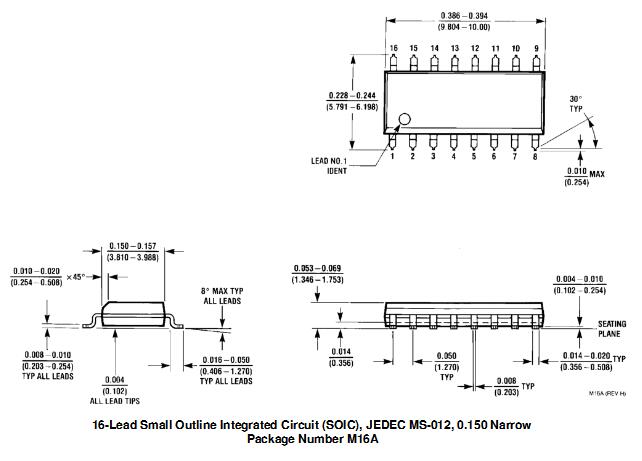

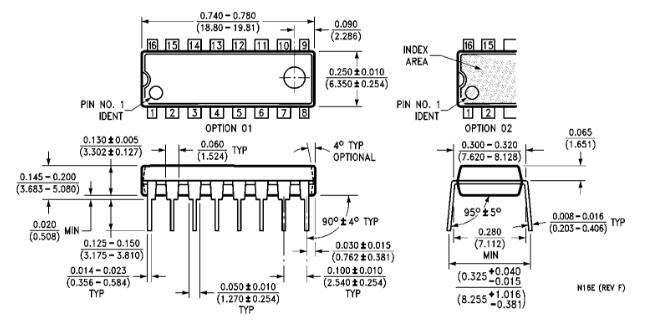

74ls75封装