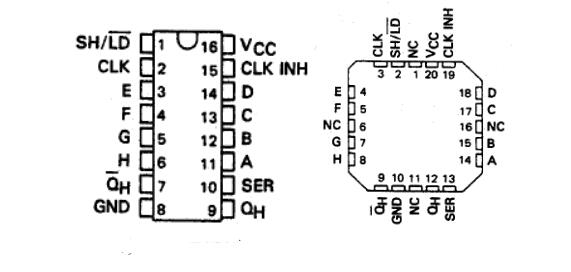

74ls165引脚图及功能

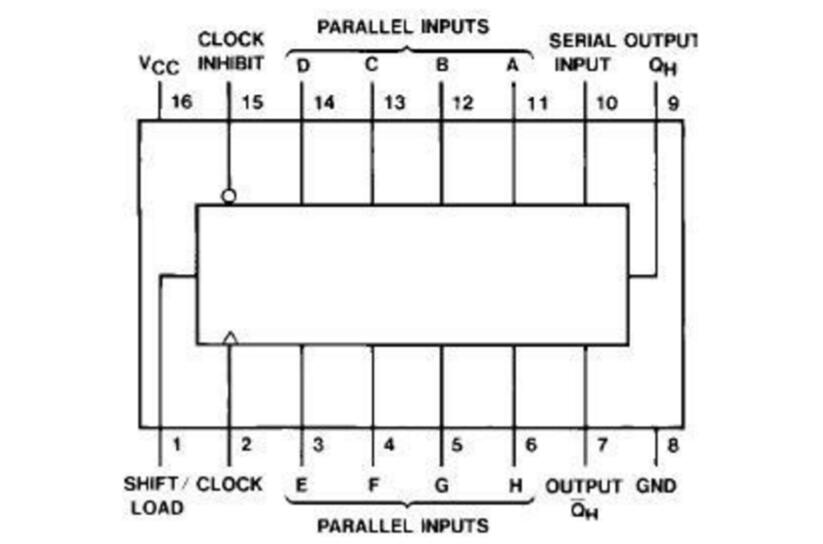

74ls165是8位并入串出移位寄存器。

CLK,CLK INH 时钟输入端(上升沿有效)

A-H 并行数据输入端

SER 串行数据输入端

QH 输出端

互补输出端

互补输出端

移位控制/置入控制(低电平有效)

移位控制/置入控制(低电平有效)

74ls165工作原理

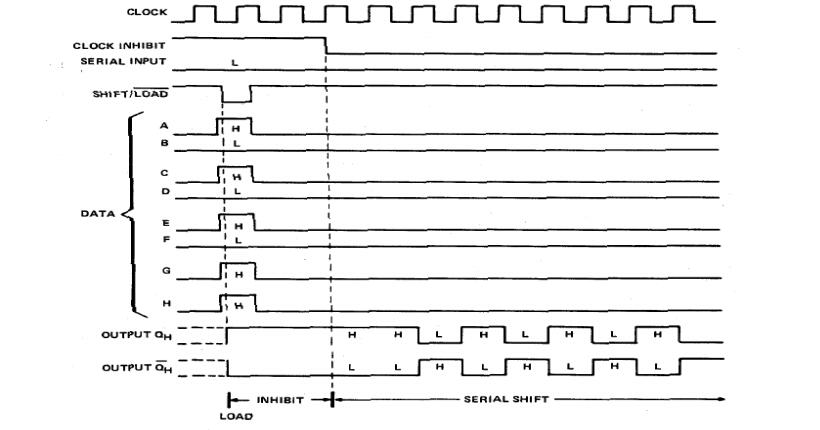

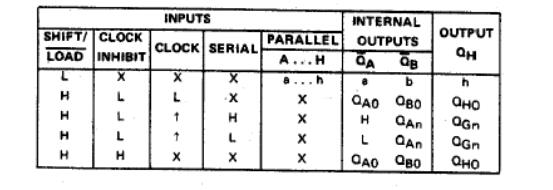

当移位\植入控制端(SH/LD)为低电平时,并行数据(A-H) 被置入寄存器,而时钟(CLK,CLK INH)及串行数据(SER)均无关。当SH/LD)为高电平时,并行置数功能被禁止。

CLK和CLK INK在功能上是等价的,可以交换使用。当CLK和CLK INK有一个为低电平并且SH/LD为高电平时,另一个时钟可以输入。当CLK和 CLK INK有一个为高电平时,另一个时钟被禁止。只有在CLK为高电平时CLK INK才可变为高电平。

74ls165逻辑图

74ls165极限值

电源电压…………………………………7V

输入电压…………………………………5.5V

SH/LD与CLKINK间电压……………………5.5V

工作环境温度

54164……………………………………-55~125℃

74164……………………………………-0~70℃

储存温度……………………………………-65℃~150℃

74ls165真值表

H-高电平

L-低电平

X-任意电平

↑-低到高电平跳变

74ls165时序图