ARM处理器中CP15协处理器地址变换过程详解

之前我们在学习MMU的时候, **知道这个内存的分配和CP15协处理器** 。这里先介绍一下CP15寄存器以及访问CP15寄存器的汇编指令。

2023-09-08 17:50:52

一文详解CP15协处理器

ARM架构通过支持协处理器来扩展处理器的功能。ARM架构的处理器支持最多16个协处理器,通常称为CP0~CP15。下述的协处理器被ARM用于特殊用途。

2023-10-31 16:07:40

在ARM嵌入式系统中访问CP15寄存器的指令

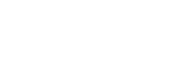

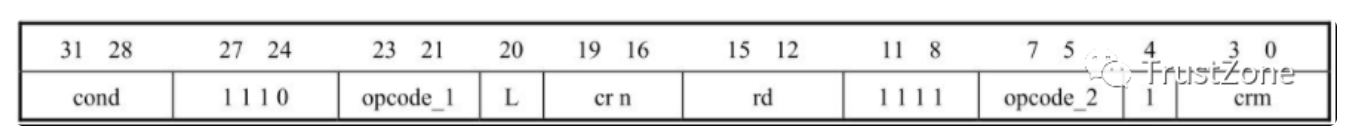

在基于ARM的嵌入式应用系统中,存储系统通常是通过系统控制协处理器CP15完成的。CP15包含16个32位的寄存器,其编号为0~15。访问CP15寄存器的指令MCR ARM寄存器到协处理器寄存器

![]() bigbangboom

2022-05-17 14:38:17

bigbangboom

2022-05-17 14:38:17

关于ARM存储管理的协处理器CP15分析资料推荐(一)

一、ARM中对于存储管理的协处理器CP15CP15可以包含16个32bit的寄存器,分别标记为0~15。但是对于同一个寄存器的物理寄存器可能会对应多个。实际上对于CP15的访问的指令相当简单,只有

![]() zhongnian

2022-05-17 14:19:33

zhongnian

2022-05-17 14:19:33

鸿蒙轻内核源码分析:MMU 协处理器

1、 ARM C15 协处理器 在 ARM 嵌入式应用系统中, 很多系统控制由 ARM CP15 协处理器来完成的。CP15 协处理器包含编号 0-15 的 16 个 32 位的寄存器。例如,ARM

2024-02-20 14:28:03

arm的协处理器有几个?ARM协处理器详解

本文首先介绍了ARM处理器特点与主要模式,其次介绍了arm的协处理器有几个,最后介绍了CP14和CP15系统控制协处理器。

2018-04-24 15:34:25

ARM核心类型和修订标识的应用说明

ARM核心通过两种机制进行识别。 第一种是通过系统控制协处理器的寄存器0,也称为协处理器15或CP15。 CP15仅在包含MMU或MPU的处理器内核上可用,并包含多个配置寄存器(实际数量取决于内核

![]() 一巷清苑

2023-08-23 06:55:04

一巷清苑

2023-08-23 06:55:04

MCR汇编指令有哪些功能呢

MCR指令将ARM处理器的寄存器中的值传到协处理器的寄存器中去这里用CP15协处理器来作为例子MCR{cond} p15,

![]() 我有一车切糕

2022-01-20 06:08:02

我有一车切糕

2022-01-20 06:08:02

鸿蒙内核源码中C7,C2,C13三个寄存器

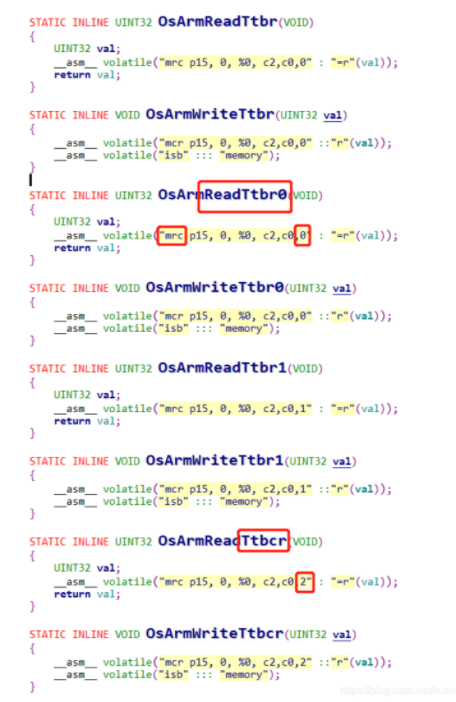

CP15的寄存器只能被MRC和MCR(Move to Coprocessor from ARM Register )指令访问,包含16个32位的寄存器,其编号为0~15。本篇重点讲解其中的 C7,C2,C13三个寄存器。

2021-04-24 10:18:48

鸿蒙内核源码分析:关于内存涉及的C7,C2,C13三个寄存器

ARM-CP15协处理器 ARM处理器使用协处理器15(CP15)的寄存器来控制cache、TCM和存储器管理。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from

2020-10-29 10:41:07

请问ARM920到底有几个协处理器?

ARM920到底有几个协处理器,手册上只看到了CP14,CP15,为什么说是若干个,是不是可以扩展,是不是每个协处理器只有一种功能?

![]() vwterwer

2019-05-22 05:45:26

vwterwer

2019-05-22 05:45:26

ARM 无法进入WFI 模式

Mode) 按照omap-138的datasheet 介绍 You can enable the WFI mode via the CP15 register #7 using

![]() 风龙陈谷子

2018-06-21 12:51:58

风龙陈谷子

2018-06-21 12:51:58

ARM9的高端异常向量基址硬件如何配置?

请问: S3C2440可以通过设置/清除CP15协处理器的寄存器1的bit13来设置高端/低端异常向量地址,我从网上看到说也可以通过硬件电路控制,但是我一直没有查到硬件如何配置???我想了解下,谢谢谁来解惑,

![]() 60user73

2019-04-25 07:45:05

60user73

2019-04-25 07:45:05

请问如何在arm清零后激活D-TCM而不激活I-TCM呢

本人刚学RAM,想在芯片内部带上TCM,只是不会配置,请问如何在arm清零后,激活D-TCM而不激活I-TCM,要详细的步骤。谢谢另:我采用指令写CP15的c9寄存器打开D-TCM,到指令执行阶段访问MEM时整个指令不再继续,请问什么原因? 谢谢

![]() 新星之火12138

2022-06-06 16:22:05

新星之火12138

2022-06-06 16:22:05

ARM的内存管理(MMU)是如何实现的?

,集成了一个被称为 CP15 的协处理器,该协处理器的 C2 寄存器中用于保存页表的基地址,下面以一级页表变换为例说明 MMU 实现地址变换的过程。4 、节访问的转换过程节和大页是支持允许只用一个

![]() emitter

2020-10-23 15:29:49

emitter

2020-10-23 15:29:49

为什么openjtag调试中会出现这个warning?

in ?? ()monitor haltmonitor arm920t cp15 2 02: 00000000monitor arm7_9 sw_bkpts enablesoftware

![]() 饿了就吃的

2019-10-29 21:15:23

饿了就吃的

2019-10-29 21:15:23

请问LEDS调试代码出现以下错误该怎么办?

asmmonitor haltmonitor arm920t cp15 2 02: 00000000monitor arm7_9 sw_bkpts enablesoftware breakpoints

![]() hongjane

2019-11-05 02:25:20

hongjane

2019-11-05 02:25:20

关于ARM存储管理的协处理器CP15分析资料推荐(三)

1、通过一段MMU的创建来说明MMU的工作方式下面这段代码是OAL进入kernel Start的一段代码,它也就是wince的页表初始化代码,涉及到两部分内如,分别为二级页表的创建和一级页表的创建。这里的一级页表和前面那个有些不同是TTB发生改变了,也就是说系统进入内核后从新创建了页表。;-------------------------------------------------------------------------------; KernelStart - kernel main entry point;; The OEM layer will setup any platform or CPU specific configuration that is; required for the kernel to have access to ROM and DRAM and jump here to start up; the system. Any processor specific cache or MMU initialization should be completed.; The MMU and caches should not enabled.;; This routine will initialize the first-level page table based up the contents of; the MemoryMap array and enable the MMU and caches.;; NOTE: Until the MMU is enabled, kernel symbolic addresses are not valid and must be; translated via the MemoryMap array to find the correct physical address.;; Entry(r0) = pointer to MemoryMap array in physical memory; Exit returns if MemoryMap is invalid;-------------------------------------------------------------------------------LEAF_ENTRY KernelStart原作者:jianwen01

![]() 泡芙奶昔

2022-05-18 16:19:41

泡芙奶昔

2022-05-18 16:19:41

关于ARM存储管理的协处理器CP15分析资料推荐(二)

1、基于二级页表的地址查询方式 上节讨论了当一级描述符[1:0]为01或者11的时候表示这是一种二级页表查询方式,而一级页表描述符仅仅做为二级页表的索引。下面我们将coarse page与fine page 一起讨论,并且之处他们的区别。 Coarse page 索引了一个二级页表,这个页表描述查询是用大页,小页还是极小页。粗颗粒将1MB的空间划分为256个4KB的空间。如下图所示:其中各个权限的控制位定义如下原作者:jianwen01

![]() 百灵千岛酱

2022-05-17 14:29:49

百灵千岛酱

2022-05-17 14:29:49

请问我能通过修改配置文件的方式来默认关闭MMU和D-Cache吗?

)Failure examining memory> 可不可以通过修改配置文件的方式来默认关闭MMU和D-Cache而不用每次都输入arm920t cp15 2 0

![]() caseylee

2019-11-05 05:45:19

caseylee

2019-11-05 05:45:19

嵌入式面试常见问题汇总,绝对实用

表,然后设置cpu为svc(特权)模式,同时关闭FIQ和IRQ(防止突发中断程序跑飞了)注:在跳转到内核之前,要满足CPU出在SVC模式下。2、对cp15协处理器进行设置,这里主要是关闭MMU和cache3、进入到板级初始化阶段,这里会进行时钟、内存、串口的初始化。最后还要关闭看门狗。4、接下来

![]() 冰箱洗衣机

2021-12-24 08:26:28

冰箱洗衣机

2021-12-24 08:26:28

鸿蒙内核源码分析(内存汇编篇):内存实现涉及哪些汇编代码

ARM-CP15协处理器ARM处理器使用协处理器15(CP15)的寄存器来控制cache、TCM和存储器管理。CP15的寄存器只能被MRC和MCR(Move to Coprocessor from

![]() 颜刚YanG

2020-11-19 14:57:04

颜刚YanG

2020-11-19 14:57:04

请问u-boot SDRAM代码具体在哪个文件中

\config.mk文件中 TEXT_BASE是干什么用的?TEXT_BASE = 0x33F80000 。现在SDRAM变成32MB需要修改这个数值吗?3、我下载到目标板上发现代码运行到 设置CP15

![]() 60user194

2019-02-25 05:11:48

60user194

2019-02-25 05:11:48

Hyp调试控制寄存器配置

HDCR 位分配下表显示了 HDCR 位分配。表 4-125 HDCR 位分配要访问处于 AArch32 状态的 HDCR,请使用以下命令读取或写入 CP15 寄存器:MRC p15, 4, &

![]() hsdou月半

2022-06-08 18:04:29

hsdou月半

2022-06-08 18:04:29

ARM1176JZF-S技术参考手册

14和CP15 •矢量浮点(VFP)协处理器支持 •外部协处理器接口 •使用MicroTLB管理的指令和数据存储器管理单元(MMU) 由统一的主TLB支持的结构 •指令和数据缓存,包括具有

![]() 香脆面

2023-08-02 10:30:50

香脆面

2023-08-02 10:30:50

【HarmonyOS】内存实现涉及哪些汇编代码

\arm目录ARM-CP15协处理器先拆解一段汇编代码CP15有哪些寄存器TTB寄存器(Translation table base)mmu上下文TLB(translation lookaside

![]() l_xy

2020-11-03 16:23:21

l_xy

2020-11-03 16:23:21

ARM1156T2F-S处理器技术参考手册

(AXI),用于支持优先级的二级接口 多处理器实现 •九级管道 •带返回堆栈的分支预测 •低中断延迟 •外部协处理器接口和协处理器CP14和CP15 •可选的指令和数据存储器保护单元(MPU) •可选的指令

![]() 北冥有熊

2023-08-02 09:15:45

北冥有熊

2023-08-02 09:15:45

内存实现涉及哪些汇编代码

本篇讲解 内存的汇编部分 源码详见:/kernel/base/vm -- kernel_liteos_a\arch\ARM\arm目录ARM-CP15协处理器先拆解一段汇编代码CP15有哪些寄存器

![]() emitter

2020-11-04 10:52:25

emitter

2020-11-04 10:52:25