FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。数字收发组件的关键技术 RF-FPGA芯片在窄带系统设计中的优势

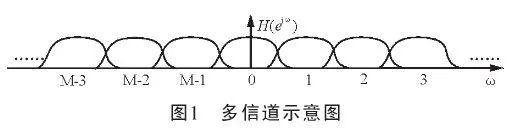

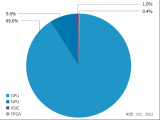

对于通信、雷达等无线电行业相关的朋友,我相信大家对于窄带系统的设计,必然是轻车熟路,如数家珍。尤其是围绕FPGA+AD/DA的数字收发的架构设计,那估计更是心中有笔,信手拈来了。 传统...

2023-08-09 1640

什么是被动后向散射?“无电池”物联网即将到来!

当谈到物联网设计时,最重要的一个方面是电池寿命。较长的电池寿命意味着更长的正常运行时间、更少的维护需求,以及物联网设备更大的可持续性。...

2023-08-09 544

如何提升跑Calibre效率呢?

Siemens的Calibre是业内权威的版图验证软件,被各大Foundry厂广泛认可。用户可以直接在Virtuoso界面集成Calibre接口,调用版图验证结果数据,使用起来极为方便。...

2023-08-09 935

求一种超低成本FPGA JTAG方案

首先按照GitHub 说明在虚拟机上安装依赖项,然后创建一个新的存储库目录并克隆了 pico-SDK 和 XVC-Pico 项目。...

2023-08-09 285

Vivado的Implementation阶段约束报警告?

前言:本文章为FPGA问答系列,我们会定期整理FPGA交流群(包括其他FPGA博主的群)里面 有价值 的问题,并汇总成文章,如果问题多的话就每周整理一期,如果问题少就每两周整理一期,一方面...

2023-08-08 796

FPGA零基础学习之TLC5620驱动教程

在FPGA处理完数字信号之后,我们有些情况下是需要将数字信号转变为模拟信号再输出的。比如音频信号在滤波后,需要转换为声音信号进行输出。...

2023-08-04 665

薄膜PMUT研究进展综述

据麦姆斯咨询报道,近日,新加坡国立大学(National University of Singapore)和新加坡科技研究局(A*STAR)微电子研究所的研究人员组成的团队在Microsystems & Nanoengineering期刊上发表了题为“Thin-...

2023-08-03 920

时钟偏移对时序收敛有什么影响呢?

FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序路径上的所有寄存器在时钟信号的驱动下步调一致地运作。...

2023-08-03 981

Vivado仿真器和代码覆盖率简析

编写 HDL 通常是 FPGA 开发中耗时最少的部分,最具挑战性和最耗时的部分可能是验证。根据最终应用程序,验证可能非常简单,也可能非常复杂,简单的话只需对大多数功能进行检查或执行完全...

2023-08-03 1306

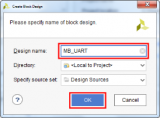

MicroBlaze串口设计

本系统中,Basys3的MicroBlaze模块调用基于AXI协议的UART IP核,通过AXI总线实现MicroBlaze-UART之间的通信,完成串口打印。...

2023-08-02 770

什么是三态电路?在FPGA上如何使用三态电路作为IO呢?

一般来说,我们认为CMOS数字电路的输出的稳定状态只有2种,就是逻辑0和逻辑1,从模拟信号量来说,就是0V和VDD。...

2023-08-01 2609

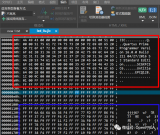

fpga时序分析案例 调试FPGA经验总结

今天跟大家分享的内容很重要,也是调试FPGA经验的总结。随着FPGA对时序和性能的要求越来越高,高频率、大位宽的设计越来越多。在调试这些FPGA样机时,需要从写代码时就要小心谨慎,否则写...

2023-08-01 1116

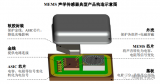

MEMS传感器的主要构造?MEMS芯片与集成电路芯片有什么区别?

MEMS的全称是Micro-Electro-MechanicalSystem,中文名称是微机电系统,是将微电子电路技术与微机械系统融合到一起的一种工业技术,它的操作范围在微米尺度内。...

2023-07-31 2400

光子集成电路(PIC)加速未来光子芯片的开发周期

液晶技术和MEMS技术使可重新编程光子集成电路(PIC)成为可能,这些PIC能够支持多种功能,并显著加速未来光子芯片的开发周期。...

2023-07-31 3891

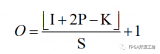

怎么去设计一种基于FPGA的扩频模块呢?

扩频系统最早可以追溯到20世纪20年代左右,扩频通信就有了初步的应用。但是一直到20世纪年代中期,扩频系统才真正应用和发展起来。...

2023-07-31 492

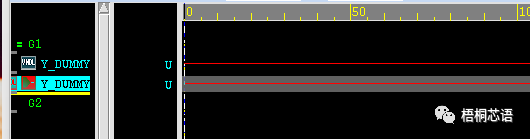

FPGA时序分析-建立时间和保持时间裕量都是inf怎么解决呢?

今天有个小伙伴遇到一个问题,就是在vivado里面综合后看到的建立时间和保持时间裕量都是inf,我们来看看怎么解决这个问题。...

2023-07-30 769

如何实现基于FPGA Vivado的74系列IP封装呢?

双击桌面图标打开Vivado 2017.2,或者选择开始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;...

2023-07-30 453

Meta:正在多款自研芯片上使用RISC-V

在DAC 2023上,Meta 的 ASIC 工程经理 Himanshu Sanghavi 谈到了 Meta 正在使用 RISC-V 开展的各种项目。...

2023-07-27 606

复位信号是什么意思?复位信号的作用?详解Xilinx FPGA复位信号那些事

复位信号几乎是除了时钟信号外最常用的信号了,几乎所有数字系统在上电的时候都会进行复位,这样才能保持设计者确定该系统的系统模式的状态,以便于更好的进行电子设计,并且在任意时...

2023-07-27 5265

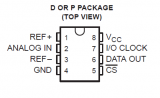

FPGA Vivado-TLC549驱动设计介绍

在生活中,数模转换的例子到处可见。但是在我们做FPGA设计时,需要对数字信号进行处理,但是,不是所有的信号都是以数字信号的形式体现的,比如光信号、声信号、电信号等等。...

2023-07-27 526

基于HLS之任务级并行编程

HLS任务级编程第一篇文章可看这里: HLS之任务级并行编程 HLS的任务级并行性(Task-level Parallelism)分为两种:一种是控制驱动型;一种是数据驱动型。对于控制驱动型,用户要手工添加DATAF...

2023-07-27 844

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |