您的位置:电子发烧友网 > 电子技术应用 > 行业新闻 > 新品快讯 >

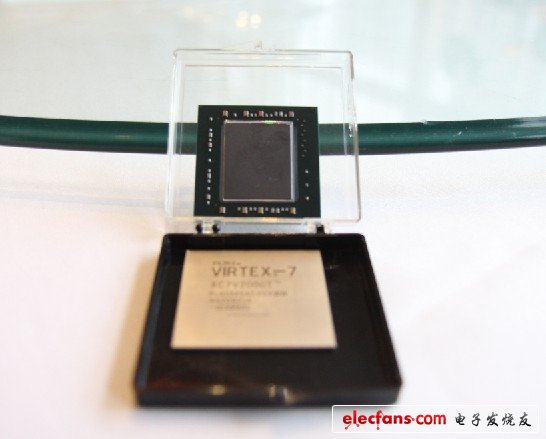

赛灵思推出采用堆叠硅片互联技术的世界最大容量FPGA:Virtex-7 2000T

2011年10月26日 14:31 来源:电子发烧友网 作者:叶子 我要评论(0)

赛灵思已向客户推出世界最大容量FPGA:Virtex-7 2000T。这款包含68亿个晶体管的FPGA具有1954560个逻辑单元,容量相当于市场同类最大28nm FPGA的两倍。这是赛灵思采用台积电(TSMC)28nm HPL工艺推出的第三款FPGA,更重要的是,这也是世界第一个采用堆叠硅片互联(SSI)技术的商用FPGA。

赛灵思可编程平台开发全球高级副总裁Victor Peng指出:“Virtex-7 2000T FPGA是赛灵思创新和业界合作史伤的一个重大里程碑。如果没有堆叠硅片互联(SSI)技术,至少要等到下一代工艺技术,才有可能在单个FPGA中实现如此大的晶体管容量。就通常新一代产品的推出而言,SSI至少提前一年讲我们的最大型28nm期间交付给了客户。这对ASIC和ASSP仿真和原型而言尤其重要。”

传统上,FPGA厂商习惯于采用最新芯片工艺技术来实现他们的新架构,充分发挥摩尔定律的作用,这样晶体管的数量每22个月就能随最新芯片工艺技术的推出而翻一番。过去20年,FPGA厂商一直遵循摩尔定律的发展,不断推出新的FPGA,实现器件容量的倍增。

Vertex-7 2000T的推出,标志着赛灵思取得了一个重大成就,也标志着赛灵思向半导体产业的3D IC迈进了一大步。ChandraseKaram指出,该产品的真正价值在于开启了用户创新之门,为苦心寻找最大容量器件的客户带来了新的设计能力。他说:“对那些希望加速产品开发,为软件开发人员提供芯片仿真功能,或者期待将多个芯片整合到单个器件中,以及那些发现其设计不能采用ASIC的客户而言,他们都将从这一了不起的技术中大受其益。通过采用SSI技术,赛灵思现在就把下一代才能提供的超大容量FPGA,交到设计人员手中。”

大型单芯片的制造挑战。

ARM 设计技术和自动化副总裁John Goodenough指出:“ARM公司很高兴与赛灵思合作,在我们的验证基础架构中部署业界领先的Virtex-7 2000T器件。这一新型器件支持一种灵活而有针对性的模拟仿真架构,能大幅提升容量,使我们能够针对ARM的下一代处理器更加轻松地进行全面的系统验证与确认。”

Virtex-7 2000T器件还为设备制造商提供了一个集成的平台,能帮助他们在提升性能和功能的同时降低功耗。由于消除了电路板上不同IC 间的I/O接口,系统的整体功耗得以显著降低。同时,因为电路板上需要的IC 器件数量减少,客户能降低材料清单成本、测试和开发成本。此外,由于芯片在硅中介层上并排放置,SSI 技术能够避免多个芯片堆叠造成的功耗和可靠性问题。中介层在每个芯片间提供10,000多个高速互联,可支持各种应用所需要的高性能集成。

Virtex-7 2000T FPGA为客户提供了通常只有大容量ASIC 才具备的容量、性能和功耗水平,更增加了可重编程的优势。由于越来越多的系统和市场对ASIC 的开发成本感到难以承受,Virtex-7 2000T FPGA为那些面临ASIC 修改风险和超过5,000万美元的28nm 定制ICNRE成本的设计,提供了一个独特的、可扩展的替代解决方案。

赛灵思所有28nm 器件(Artix™-7、Kintex™-7、Virtex®-7 FPGA和Zynq™-7000 EPP)均采用统一架构,能够在同一系列的不同产品间以及不同系列的产品间支持设计和IP 重用。这些器件均采用台积电的28nm HPL(低功耗高介电层金属闸技术)工艺制造,这样制造出来的FPGA 静态功耗比同类竞争产品降低一半。随着器件容量的增大,静态功耗降低的意义越发显著。Virtex-7 2000T相对于采用多个FPGA实现的设计方案而言,功耗更低,其中28nm HPL起到了关键作用。

标签: