先看看供应商送的外壳样品,有好几个抽屉,应该是积累了多年的结果!

挑了个小的,测了下三围,长约83.5毫米

宽约42毫米,

高约30.5毫米

全景加上内部图:

外壳厚2.5-2.6毫米,两侧面长75毫米,去除厚度,PCB的两边不会超过70毫米,假设锡点高2毫米,PCB厚1.6毫米,元件的高度要限制在22毫米左右,由于外壳的弧形结构,四周的元件要矮一点.

算下体积,做个反激24W左右的电源应该可以,就按12V2A做吧.

接着应该定个方案了,先选IC,反激这一块可选的IC真是不能再多了,公司里常用的是昂宝这个品牌,这个功率段用OB2263不会有问题,由于体积有点小,优选贴片的,同样很多元件都应该以贴片为主.....

接下来就按OB2263设计电路图.....

完成的原理图,是按OB的典型应用设计的,

电脑上没有PDF生成软件,只好截图....

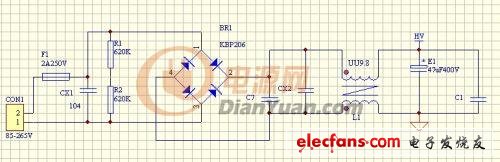

下面是各部分,输入滤波/整流

PWM及VCC供电部分:

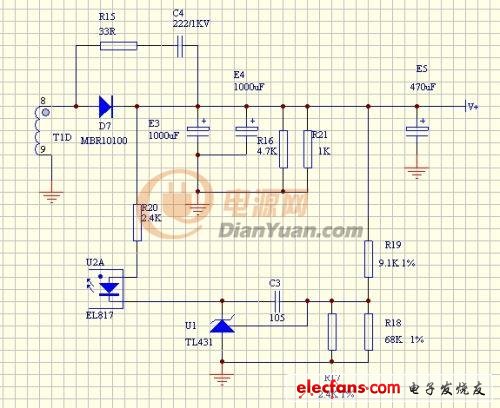

输出和电压取样部分:

先说下输入滤波/整流部分元件取值估计方法:

重传下这部分电路,方便观看

由于PCB的面积较小,而保险要求的距离要2.5毫米以上,为方便布局并节省空间,把保险丝放到输入的最前.假设输出24W,允许最大输出为1.2倍,效率假设为80%,最低输入交流85V,加上只有电容滤波,PF值约0.5,那么输入电流有效值约为

IAC=24*1.2/0.8/85/0.5,约等于0.85A;

由于温度降额,开机冲击等原因,这个保险丝取值应该在1A以上,而且保险的作用并不在于保护后面元件的安全,只要求能断开电网,所以取个2A250V的值.

输入端离外壳比较近,元件不能用太高的,X电容用了小体积(约13*12*6)的,容量只有0.1微法,R1,R2为放电电阻,要求断开电源1秒后X电容上的电压降到安全范围内,经计算,1.5M以下完全满足要求,但要满足耐压,还得用二个电阻串联.

接下来是桥堆,按保险丝算出来的电流取就可以,耐压同样要满足,个子也尽量小,用了个KBP206.

共模电感也是按经验用的,40W以下一般是UU9.8,这颗料常见成本也低,考虑到X电容偏小,在桥堆和电感之间加入一个聚酯类的电容,好处是可以做到小体积大容量.

电解电容也是按2微法/W的经验值取,这里用47微法.

C1,C7是小容量贴片高压电容,如果做EMI的话可以按需要取舍.

接下来说说PWM部分,原理图如下:

R3,R4,E2组成IC的启动电源,基本上按厂家给的数据赋值,实际上这个回路是有算法的,要求IC输出一个驱动信号之后电容上的电压不能低于IC的关闭电压值.

插个不是题外的题外话:据我所知,有几家电源厂考试时会考到这个问题,就是问应试者怎么取启动电源的元件数值,也不知道是哪个厂家开始搞的.这个对基础知道要求还是挺严的,包含了IC,电容,电阻的基本知识,如耐压,漏电流等等.

IC第一脚接地,是输入/输出信号和电源的公用端;2脚反馈,外接光电耦合器的集电极,并一个用于滤除高频信号的小容量电容;3脚外接电阻到地可以改变IC的工作频率,这里取推荐值100K;4脚电流感应信号输入端,内部已经有延时,小功率应该时一般不用再外加RC延时;5脚为IC的供电端;6脚驱动信号输出,外接的R6,R7,D5可以改变驱动信号对MOS输入电容的充放电速度,进而对开关波形的上升下降沿作调整,有利于EMI整改,R8主要作用是泄放MOS栅-源间积累的电荷,一般取值几K到40-50K,按经验用10K.

C6也用于改善开关波形,一般100P以下常用,做EMI时按需取舍,先留个位置.

CY1是安规电容,由于漏电流的规定,取值不大于103,算法比较麻烦,可以按经验取值,具体可以在EMI整改时调整.

D6,C5,R12,R13是MOS的吸收回路,要保证MOS不会因为变压器感应的反射电压和漏感造成的尖峰击穿.同时它们也会引起损耗,因此取值时得有个折衷.

R9,R10,R11用于将开关电流转换成电压,具体的取值要看变压器设计了.

最后说下输出和电压取样反馈部分,电路原理图如下:

D7是整流管,一般情况下,参数要求正向电流大于等于3倍输出电流,具体算法不再说明;反向耐压大于(初级最高电压除以初次级匝数比+输出电压),并留有一定余量.按经验这里用100V的管子就行,因体积较小,设定电流10A,可以减少发热量.

R15,C4是整流管的吸收回路,对整流管的电压波形起调整作用,并防止过高的尖锋电压损坏整流管;对EMI整改有用.

R16,R21是假负载,对电源轻载时的稳定性有作用,并不一定用到,先留位置.

E3,E4,E5是储能电容,可以说输出部分的能量都要由它们提供,对它们的要求是内阻越小越好,能承受的纹波电流越大越好;

R17,R18,R19为电阻分压取样网络,通过调整它们的值可以确定输出电压,这里输出电压约为基准电压*(R19/(R18//R17)),图中用431作基准,基准电压约为2.495V,算出来输出电压约为12.3V.

R20为光耦限流电阻,C3是431本身的一个反馈网络,为简单化,只用了一个105的电容.

完成的PCB文件:

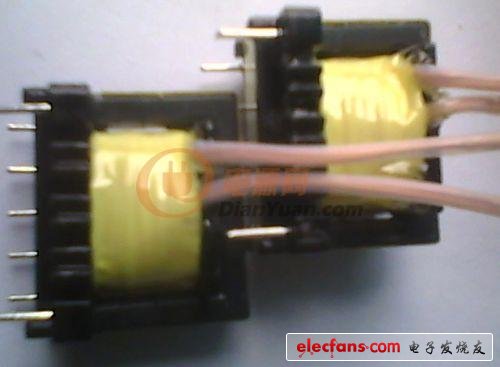

用了立式EE25变压器,为了过安规,次级用飞线引出;DS吸收回路中的电容也改成贴片的;为降低高度,MOS和肖特基的焊盘孔都加大,元件可以直接贴到板上.

面积受限,将Y电容骑到光耦上面;

前面开槽用于焊接AC线,后面的方便放置线卡.

同时生成DXF文件,用于绘制散热片.

用CAD做的散热器图纸:

2毫米厚,铝制.

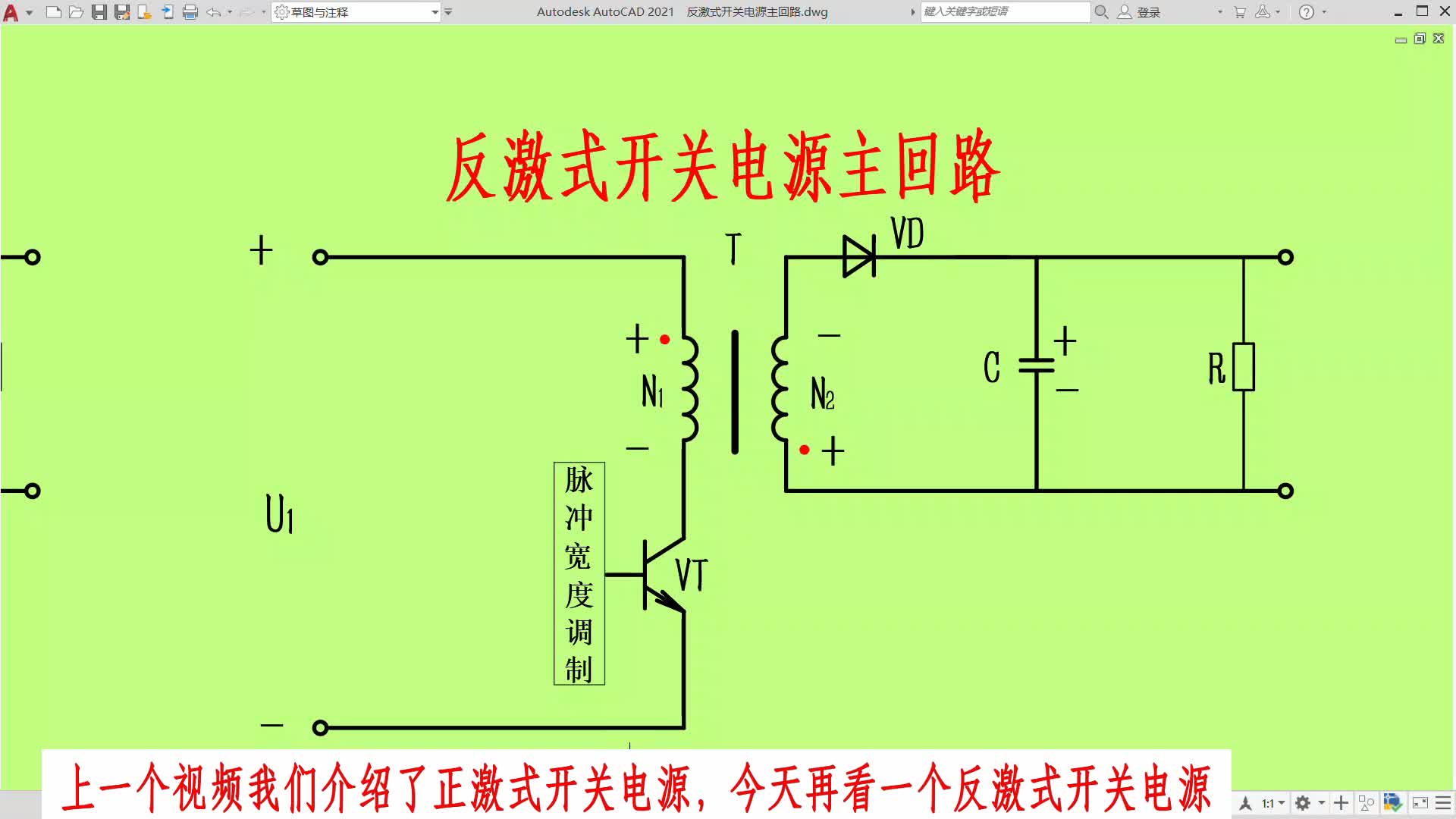

其实在布板之前已经对变压器进行选取,个人习惯按AP法选用磁芯,由于整机高度和PCB面积限制,只能选小一点的,相同频率相同功率下断续模式用的磁芯要小一点,决定以断续模式计算磁芯。

AP值的公式:

AP=Aw*Ae=Pt*106/[2*ko*kc*fosc*Bm*j*?]

其中Pt=Po+Po/ ?

Pt:视在功率,单位W;

Po:变压器的输出功率,单位W;

? :变压器的效率,小功率一般选0.9-0.95,选0.92;

ko:窗口的铜填充系数,一般选0.3-0.5,这里考虑到安规,会用三层绝缘线做次级,用0.3;

kc:磁芯填充系数,对于铁氧体=1;

fosc:磁芯工作频率,单位HZ;

j:电流密度,一般取j=5A/mm2

Bm:变压器工作磁通,单位高斯

AP值的单位,CM的4次方.

这里的变压器输出电压约(12.3V+0.6V),0.6V是肖特基二极管正向电压降;电流是2.4A(设过电流点为正常输出电流的120%);变压器输出功率是31W.

工作于断续模式,BM取2000高斯,得到AP值为0.18。

接下来计算变压器,过程大抵如下:

1,计算输入最小交流对应的直流电压:

设最低输入电压85V,容性负载时电容上的电压约为输入交流值的1.2倍,约为102Vdc;

2,确定频率和最大占空比,占空比大变压器利用率高,次级感应的电压低,可以用耐压低的整流二极管,但初级开关管的峰值电压高,所以有时得折衷选择.

这里设频率为65KHZ,占空比为0.4,由这两个算出开关管最大开通时间为6.15微秒;

3,由最大占空比算出匝比N:

N=(最低输入电压*最大占空比)/(输出电压+整流二极管正向电压降)/(1-最大占空比),

N=(102*0.4)/(12+0.6)/(1-0.4)=5.397

由N可以得出反射电压Vor=(输出电压+整流二极管正向压降)*N,

代入上式结果,得到Vor=68V;

4,确定变压器最大输入峰值电流:

IPK=2*变压器输出功率/(变压器效率*最低输入直流电压*最大占空比)

=2*(12+0.6)*2/(0.92*102*0.4)

=1.3427(A)

5,算出变压器初级电感LP:

LP=(最低输入电压*最大开通时间)/峰值电流,

LP=(102*6.15)/1.3427

=467(uH)

取470微亨

6,算出初级匝数NP:

NP=(初级电感量*初级电流峰值)/(磁芯截面积*工作磁通)

计算AP值时已经取工作磁通2000高斯,EE25的磁芯截面积为40平方毫米,这里如果电感量用微亨的话,工作磁通应该用特斯拉,2000高斯=0.2特斯拉.

NP=(470*1.3427)/(40*0.2)

=78.9,取79匝;

7,由匝比算出次级匝数NS=79/5.397=14.6,取15匝;

8,设OB2263工作时供电电压为18V,则供电绕组匝数=18/(12+0.6)*15,约等于21匝.

接下来按电流容量取线径,算窗口填充系数,我初级线径取0.35*1根,次级用二根0.5的三层绝缘线,供电绕组用0.2漆包线*1根.

查了下它们的数据,0.2的线最大外径为0.27,0.35的线最大外径0.42,0.5的三层绝缘线为0.8,线包总的截面积为

3.14*(0.27*0.27*1*21+0.42*0.42*1*79+0.8*0.8*2*15)/4=27.2平方毫米,

EE25的AW为78.2,则填充系数=27.2/78.2,约为0.35,可以装得下.

得知PCB下午应该能到,变压器还没来,先手工绕个,次级没用三层绝缘线,只用了0.65的漆包线一根,样子有点丑,因为没找到合适的胶带,自己裁的.....

看起来还有好多绕线空间....

可以的,不过板已经发出打样,现在的PCB却改成这样了:

整体没什么变化,400V电解电容阳极处的跳线J1取消了,要加工一下电解电容才好插件.

基本完成插件作业...先上个图

继续进行中,上几张....

这是来的散热器...

穿上硅胶套管做绝缘....

打上管子,没找到新的塑封10100,只能用旧的了...

另一面.....

装起来就这个样子,大电解用的是16*26的;

焊上引线,接底壳...

测试中,变压器也到了,干嘛不早点到呢...

上测试图。。。。。

先说下改动了哪儿,有DIY的朋友注意了。

1,光耦的限流电阻改4.7K;

2,输出端的E5由8*14改8*12,220微法,原因是高了不好装壳。

3,输出加了假负载3K,1206的。

4,散热器二极管处斜剪掉2*2的一个三角,原因同上条。

5,MOS吸收回路的C5改222/1KV贴片。

先上空载:

机子测试中。。。。。

MOS的波形:

满载波形230V:

满载120VAC,没60HZ的AC源,测试50HZ的:

电压还低一点就变这样:

只测满载,如有DIY的朋友自己测试其他的负载,还是手工做的那变压器,全50HZ频率下测量的;

效果有点不如意,朋友们自己可以在变压器上改良一下:

230V时

120V时

100V时

电子发烧友App

电子发烧友App

评论