引言

设计人员可以通过控制器的开关频率抖动,减少一个脉冲宽度调制(PWM)控制器的电磁干扰(EMI)分布中频谱分量的峰值幅度。时钟抖动扩频技术并非意在取代传统的EMI降低技术,但它们与传统技术的结合使用,可以减少系统中的EMI分布。它们还可以利用减少通过某些排放标准所需的屏蔽和滤波量来降低成本。

我们采用外部扩频抖动时钟源,既有IC也有FPGA,来驱动PWM降压转换器,结果如下所述。 如果FPGA时钟源已存在于系统中,由于不需要添加额外的组件,因此它将是一个更好的选择。

专用IC扩频抖动的时钟源为Exar g公司的PowerXR设备提供时钟脉冲。PowerXR让设计师可以灵活地选择一个PWM控制器开关频率,以及自如地实现外部时钟源的同步。

原理

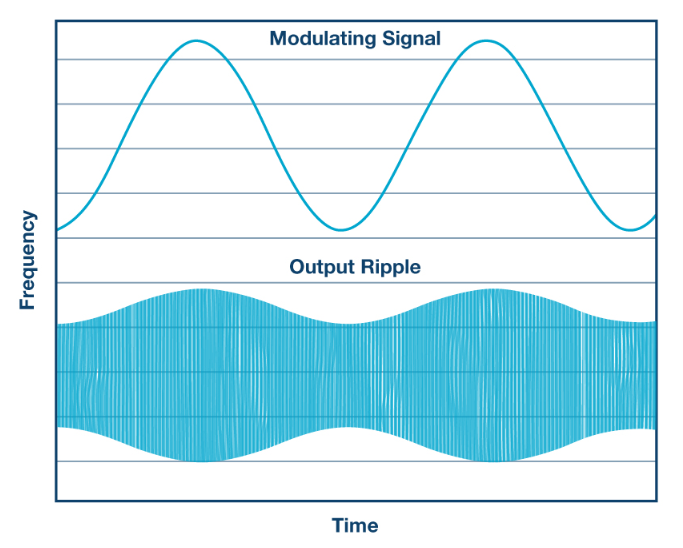

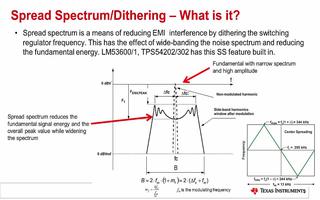

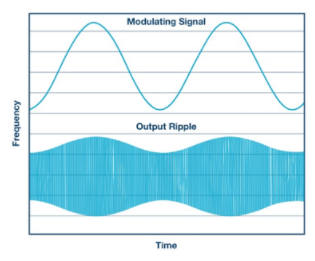

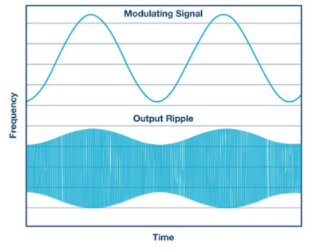

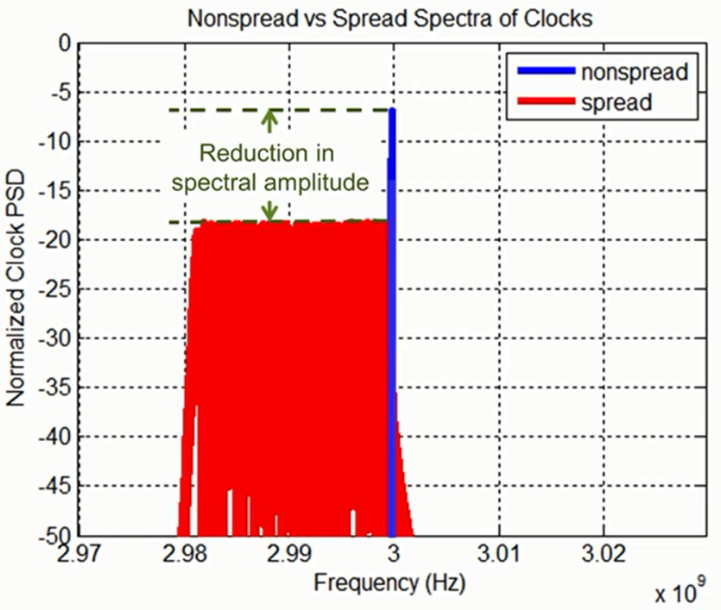

在常见的PWM控制器中,时钟波形是一个方波,其频谱由基本开关频率、fsw和高阶奇次谐波组成(图1a)。 通过三角波调制基频进行扩频,可以在更宽的频带上分散基频和高次谐波中集中的能量,从而减少峰值排放(图1b)。 由于宽频能量保持恒定,扩频还能增加噪底。

图1: (a) 非抖动时钟的频谱。 (b) 抖动时钟频谱(蓝色)。

例如,如果fsw = 300千赫,所得到的高次谐波将是900千赫、1.5兆赫、2.1兆赫等。随着高次谐波振幅的减少,基本开关频率的振幅将是最高的。

实际辐射分量的振幅将取决于辐射传输效率以及其它诸多因素的影响,包括频率、布局和路径长度。 但振幅一般会随着频率的增加而减少,其中有一个或多个频率的辐射可能比其他的更有效。

在两个边界频率之间调制基本开关频率称为时钟抖动。 PWM控制器基本开关频率的抖动会在一个相当窄的频带内改变基本开关频率。 例如,如果fsw = 300千赫,则此频率的±1.5%对称抖动(简称为中心抖动)加上三角波的抖动作用,将产生从295.5千赫至304.5千赫的PWM控制器开关频率范围。

所得到的抖动频谱显示了各种频谱分量振幅的减少及其各自频宽的增加。 同时,由于宽频能量保持恒定,还出现了噪底的增加。

抖动频率fDITHER通常介于20和40千赫之间。 虽然更复杂的调制波形不无可能,但事实证明简单的三角形波形产生效果最好。 同时,经证明,时钟抖动导致了频谱分量振幅减少,这可以通过以下公式来说明:

频谱衰减[dB]=10*log[(fsw*d)/(fDITHER/n)]

其中:

fsw = PWM控制器开关频率(介于PowerXR设备的300 kHz和1.5 MHz之间)

d = 基本开关频率的抖动百分比(通常介于±0.25%和±5%之间)

fDITHER = 抖动调制率(通常介于20 kHz和60 kHz之间)

n = 系统时钟分频器

增加d和减少fDITHER的效果一样。

专用扩频时钟发生器

一些厂家生产专用的IC时钟抖动扩频时钟发生器。 在常见设备中,IC的参考时钟源来自外部晶振(XTAL)或外部时钟源(CLKIN)(图2)。

图2: 专用IC扩频时钟发生器框图。

根据晶振或外部时钟源频率,可编程的相位锁定回路(PLL)可产生范围从几MHz到超过100 MHz时钟源。

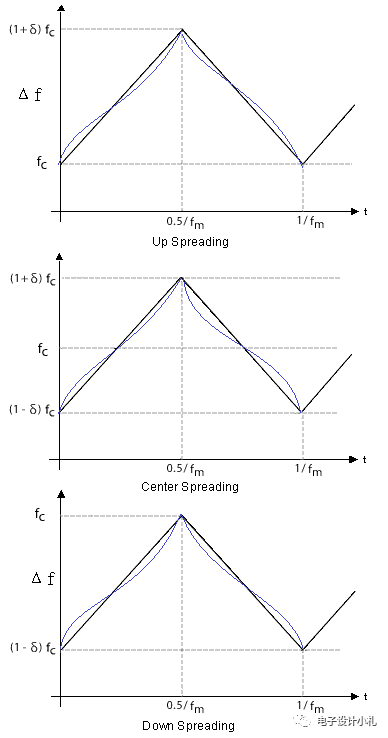

许多外部扩频控制线通常可用于控制相对于参考时钟源频率的抖动范围。 这些控制线也可决定时钟频谱将是中心抖动、向下抖动,或相对于参考时钟源频率的向上抖动。

所支持的参考频率的确切范围将取决于IC,但它通常涵盖的范围很广,足以支持驱动器所需的系统时钟频率。因为晶振制造商很多,因所以找到一个比较接近所需系统时钟频率的产品轻而易举。

例如,如果所需的PowerXR系统时钟频率为28.8 MHz(300 kHz PWM开关频率),则合适的晶振可能是Abracon ABLS-28.63636MHZ-B4-FT,可以产生28.63636 MHz的频率,, 符合PowerXR系统时钟频率0.57%的范围 这可可以允许参考时钟源频率±1.1%左右的中心抖动,同时保持在PowerXR设备要求的所需±5%同步范围内。

使用抖动FPGA设备

有关实施扩频时钟发生器的详细信息可从FPGA厂商处获得。 如果系统现有用的FPGA资源,与前面讨论的专用IC方法相比,在FPGA中实施扩频时钟发生器可以节省成本和空间。

以用FPGA实施的常用扩频时钟发生器框图为例(图3)。 大多数FPGA厂商提供扩频模块或基原,可以用来从参考时钟源产生时钟抖动信号。

图3: FPGA扩频时钟发生器框图。

参考时钟通常来自分频器或倍频模块,并且频率与所需的系统时钟频率相同。 微调模块由调谐/抖动命令模块控制,并使用可配置的频率阶跃和其间可配置的时间间隔,向上和向下调节PLL输出频率(CLKOUT)。 PLL内核模块配置详情可以从FPGA厂商处获得,但如图所示,内部反馈回路通常为断开状态,微调模块则被放置在外部反馈环路中。

连接驱动器

PowerXR设备使用一个可编程的系统时钟频率和一个可编程的分频器来产生PWM控制器的开关频率,fsw。如果对这些设备进行配置,从外部同步时钟源操作,时钟源的频率必须在内部系统时钟频率的±5%范围之内。

数据表中提供了一个表格,有助于确定下分频的系数n。例如,对于在300 kHz的操作,系统时钟频率可能是28.8 MHz, n值为96。在此情况下,d的频谱衰减 = ±1.1%(即2.2%),fDITHER = 56 kHz为:

频谱衰减 = 10*log[(fsw*d)/(fDITHER/n)] = 10*log[(300 kHz)*(0.022)/(56 kHz/96) = 10.5 dB。

因此,除了所有谐波外,基频的振幅将衰减约10.5 dB。

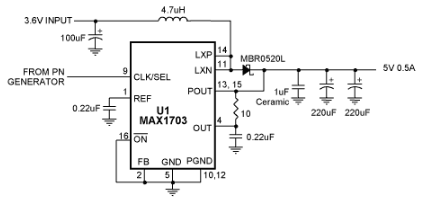

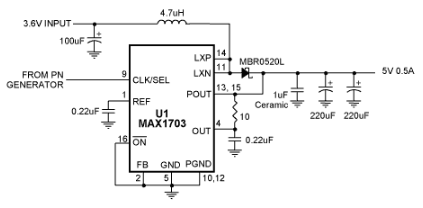

测试配置

在用于收集非抖动和抖动时钟源的排放数据的测试设置中,PowerXR设备同步至时钟发生器提供的外部时钟源(图4)。 电路中的LX节点是用于收集非抖动和抖动排放数据的测量点,因为它包含了最高的电压峰值和所有相关的辐射频谱分量。

图4: 测试设置。

虽然在LX节点收集的数据不是实际的辐射排放数据,因为它不包括每个频谱分量的辐射效率,但可将它用于比较非抖动和抖动时钟数据之间的相对水平。

XRP7714 PowerXR设备是一个4通道数字PWM降压控制器,但仅启用通道1并用于收集排放数据。 外部同步时钟源连接到其中一个通用I/O (GPIO)端口。

PowerXR设备使用PowerArchitect开发软件在I2C端口上配置。该软件可从Exar网站下载。 如先前所讨论的,该设备针对基于28.8 MHz系统时钟频率的300 kHz PWM开关频率进行配置。

测量的数据

基线排放数据的收集采用了零扩展、外加上述±1.1%中心扩展的28-MHz ModOUT时钟源收。 28.63636-MHz ±1.1%抖动时钟源的抖动频率范围是:

fmax = (28.63636 MHz)(1.011)/n = (28.63636 MHz)(1.011)/96 = 301.6 kHz

fnom = 28.63636 MHz/n = 28.63636 MHz/96 = 298.3 kHz

fmin = (28.63636 MHz)(1 – 0.011)/n = (28.63636 MHz)(1 – 0.011)/96 = 295.0 kHz

该数据表示+1.07%/–1.01% (2.08%)的频率扩展,这与±1.1%(2.2%)的预期扩展非常接近。 与预期的一样,基准频率在fnom = 295.3 kHz时进行测量。 每个波形的占空比是50%左右,和VOUT1/VIN = 5 V/10 V = 0.5电压转换比所预示的一样。

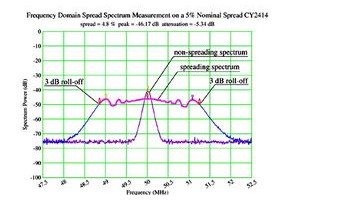

非抖动和抖动频谱的频域图像表明所有抖动频谱分量振幅低于相应的非抖动组件,而且它们的宽度也稍大。 这在叠加波形时更明显(图5)。 频率介于6.50和9.00 MHz之间。 示波器的噪底性能的限制,妨碍了在更高频率下的精确测量,但这些情况可作为在更高频率下预期行为的很好的例证。

图5: (a) 非抖动频谱。 (b) 抖动频谱。 (c) 两个频谱的重叠。

示波器中内置的快速傅立叶变换(FFT)功能有局限性,因此导致频谱分量的振幅、宽度和整体形状有些失真,但它仍然可用于说明频率抖动技术的优点。

较大主频谱分量之间的低振幅频谱分量是由于占空比恰好不是50%。 当一个时域的脉冲串有一个恰好为50%的占空比,所得到的高次频谱分量是基频的奇数倍,而对于非50%的占空比,所得到的频谱分量是基频的整数倍。

电子发烧友App

电子发烧友App

评论