2 测试电路设计

2.1电路设计

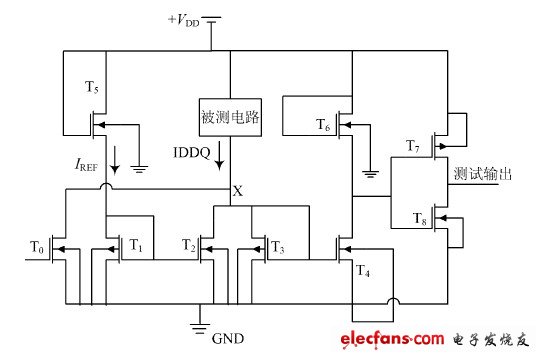

图2所示为CMOS测试电路,其由1个电流差分放大电路(T2,T3)、2个镜像电流源(T1,T2和T3,T4)和1个反相器(T7,T8)组成。镜像电流源(T1,T2)用来产生一个参考电流IREF,电流源(T3,T4)的电流为(IDDQ-IREF),其作用相当于一个电流比较器。IDDQ是被测电路的电源电流。差分放大电路(T2,T3)计算出参考电流与被测电路异常电流IDDQ的差。参考电流IREF的值设为被测电路正常工作时的静态电源电流,其取值可通过统计分析求出。

图2测试电路

2.2工作模式

测试电路工作于两种模式:正常工作模式和测试模式。电路使能端E作为管子T0的输入,用来控制测试电路与被测电路的连接和断开,即测试电路的工作模式。

在正常工作模式下(E=1),T0导通,IDDQ经T0管到地,测试电路与被测电路断开,被测电路不会受到测试电路的影响。

在测试模式下(E=0),T0管截止,被测电路的静态电流IDDQ与参考电流IREF比较,如果静态电流比参考电流大,则电流差分放大电路计算出差值,反向器的输出即测试输出为高电平(逻辑1),表明被测电路存在缺陷。若静态电流比参考电流小,反向器输出即测试输出为低电平(逻辑0),表明被测电路无缺陷。

2.3不足与改进

因为测试电路加在被测电路与地之间,所以会导致被测电路的性能有所下降。为了消除这种影响,另外加上控制端X。在正常工作模式情况下,X端接地,测试电路与被测电路分离,测试电路对被测电路无任何影响。在测试模式下,X端悬空,E端接地,T0管截止,测试电路进行测试。

在测试模式下,X端悬空,E端接低电平,若电路有缺陷,测试输出为高电平。但是被测电路输入跳变时,被测电路无缺陷,也会产生一较大的动态峰值电流IDDQ。为了避免出现误判断,在此种情况下,测试电路应输出为低电平。所以在被测试电路输入变化后,必须在瞬态电流达到稳定时才可进行IDDQ测试。

3 结语

本文所设计的IDDQ测试电路由一个电流差分放大电路、电流源、反相器组成。在正常工作模式下,测试电路与被测电路断开;在测试模式下,电流差分放大电路计算出被测电路电流与参考电流的差,反相器输出是否有缺陷的高低电平信号。测试电路用了7个管子和1个反相器,占用面积小,用PSpice进行了晶体管级模拟,结果证明了其有效性。IDDQ测试的缺点是随着特征尺寸的缩小,每个晶体管阈值漏电流的增加,电路设计中门数的增加,电路总的泄漏电流也在增加,这样分辨间距会大大缩小,当出再重叠时就很难进行有效的故障检测和隔离。

但尽管如此,由于IDDQ测试电路的简易性非常突出,所以它仍然是目前可测性测试技术的研究热点。

用户评论

共 0 条评论