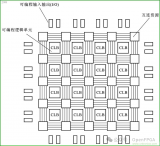

FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。易灵思钛金系列加密方案-V1

硬件设计要求 在之前的版本中,加密是通过VCC_AUX来供电的。在新的版本中已经通过单独的VQPS管脚来供电来实现。 对于Ti35/Ti60F225,VQPS供电管脚是G6, 对于 Ti35/Ti60F100S3F2,VQPS供电管脚是 A5,这...

2024-10-30 557

FPGA无芯片怎么进行HDMI信号输入

FPGA 在无外部PHY芯片情况下输出HDMI,目前是比较成熟的方案(外部电路需要转换成TMDS电平)。在无PHY芯片情况下怎么进行HDMI信号输入呢?...

2024-10-24 957

易灵思Efinity入门使用-v8

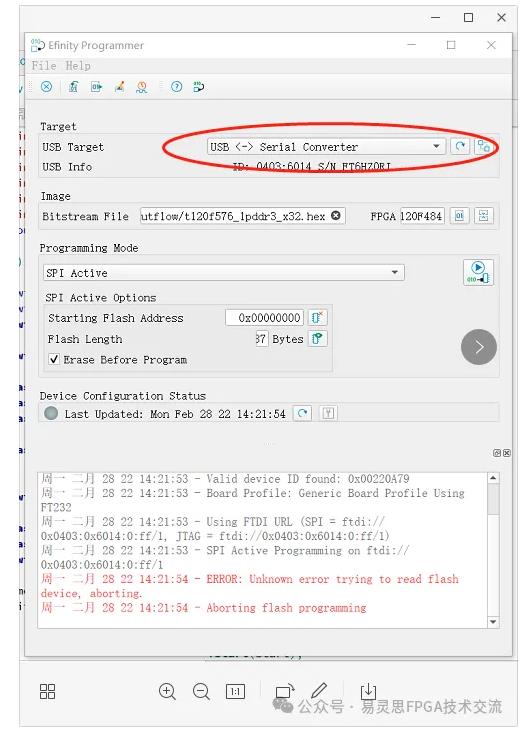

Step1:点击设置 Step2:在Top level project path中输入路径 Step3:点击File -> Open Project,路径会指向step2中设置的路径...

2024-10-23 586

Efinity FIFO IP仿真问题 -v1

Efinity目前不支持联合仿真,只能通过调用源文件仿真。 我们生成一个fifo IP命名为fifo_sim 在Deliverables中保留Testbench的选项。 在IP的生成目录下会有以下几个文件 我们来看下modelsim.do文件,里面...

2024-10-21 754

FPGA软件Efinity入门使用-v7

一、 软件预设置 二、新建工程 三、添加源文件 四、添加管脚约束 五、添加GPIO 六、 PLL设置 七、IPM添加IP 八、 添加debug 九、下载 十、仿真 十一、查看软件版本 一、软件预设置。 选项...

2024-10-21 521

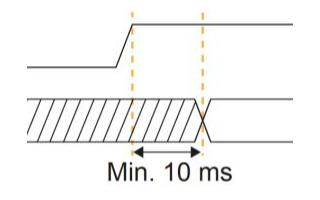

逻辑布线锁定 用FPGA实现TDC时的逻辑锁定和布线锁定

在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。 Efinity从2022.1开始支持逻辑锁定,从2022.2开始支持逻辑和布线锁定。当然锁定布线时也要锁定相应的逻辑 因...

2024-10-15 1245

莱迪思分析不断变化的网络安全形势下FPGA何去何从

莱迪思安全专家与Secure-IC的合作伙伴一起讨论了不断变化的网络安全环境以及现场可编程门阵列(FPGA)技术在构建网络弹性中的作用。...

2024-08-30 749

数字芯片设计验证经验分享(第三部分):将ASIC IP核移植到FPGA上——如何确保

本篇文章是SmartDV数字芯片设计经验分享系列文章的第三篇,将继续分享第五、第六主题,包括确保在FPGA上实现所需的性能和时钟两个方面的考量因素。...

2024-08-26 1638

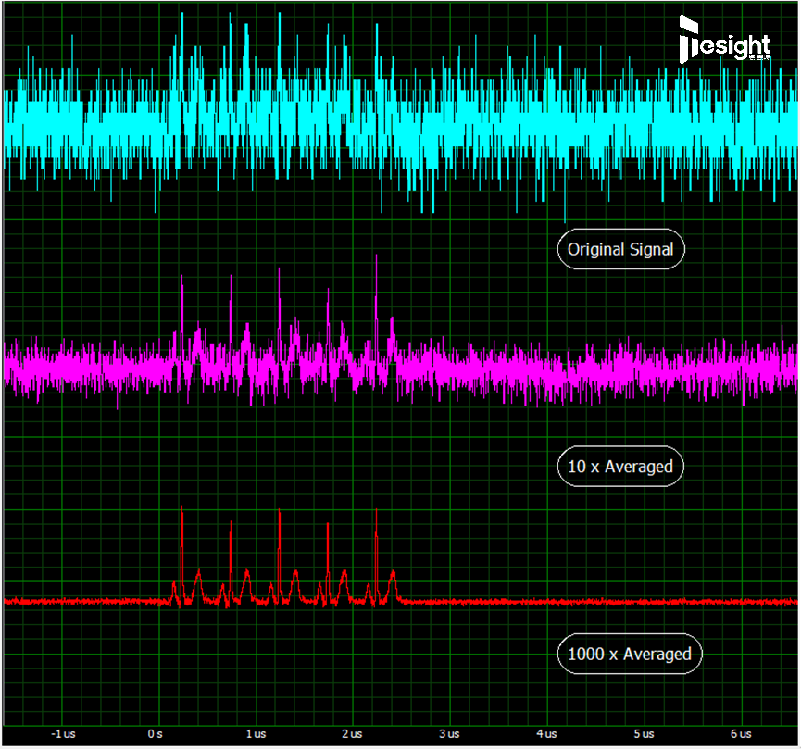

德思特分享 突破FPGA限制:德思特TS-M4i系列数字化仪利用GPU加速实现高效块平均

本白皮书将展示如何使用德思特TS-M4i系列数字化仪的高速PCIe流模式来在软件中实现块平均处理,从而突破FPGA的限制。我们用了TS-M4i.2230(1通道,5 GS/s,8位垂直分辨率,1.5 GHz带宽)作为例子,...

2024-08-20 1100

瑞苏盈科打造基于工业标准SOM的人工智能

FPGA技术能够以低功耗和低延迟实现复杂的神经网络,同时还能连接大量外设并提供对工业应用非常重要的高稳定性,因此正在成为嵌入式人工智能应用领域的主要参与者。客户挑战在这种情况...

2024-08-10 728

LVDS的GCLK接收方案

在易灵思的器件上接收LVDS一般采用PLL接收,通过PLL产生两个时钟,一个是fast_clk,一个是slow_clk,分别用于处理串行数据和并行数据。 但是如果LVDS的速率比较低时,另外想通过去掉PLL来节省功...

2024-08-12 1176

P4 Suite for FPGA面市 P4 Suite for FPGA主要功能解析

基本简介 P4 Suite for FPGA是一款 综合性工具套件, 可在数字网络的不同领域提供广泛功能,该套件能够以高达200 Gbps甚至更高的数据传输速率支持FPGA。这一发展为虚拟蜂窝基站路由器...

2024-07-25 840

Efinity编译生成文件使用指导-v1

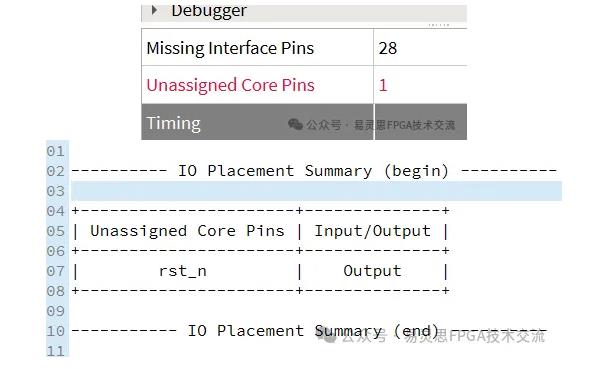

接上篇: (6)查看Unassigned Core Pins。 在placement下面的palce.rpt文件中搜索 Unassigned C ore Pins就可以看到。它说明这些管脚没有用于内部连接。 大家可以点击这个链接查看上文 Efinity编译生成文件使...

2024-08-13 636

Efinity编译生成文件使用指导

(1)查看综合后的原语 在outflow .map是网表对FPGA资源的映射。比如gbuf,dspt等原语的是怎样适配的,可以从这里找到。下面是一个乘加在原语上的映射情况。 module top(a, b,c, clk, o); input signed [1...

2024-08-13 1070

Efinity debuger常见问题总结-v2

Efinity在Debug时会出现UUID mismatch错误。很多刚开始使用的人经常遇到。下面我们做一个总结。欢迎遇到案例时共同分享。...

2024-07-11 1933

基于安路科技FPSoC器件DR1系列的视频采集/显示/处理解决方案

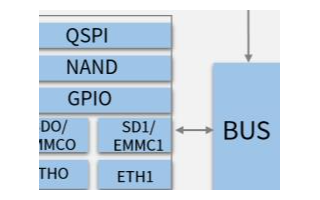

安路科技全新一代FPSoC器件DR1系列, 集成高性能硬核处理器双核ARM Cortex-A35或单核64位RISC-V、丰富的片上内存和高低速外设接口、FPGA可编程逻辑、NPU/JPU硬件加速单元, 内部通过高带宽总线互联...

2024-06-29 1126

FPGA厂商紫光同创入选多样性算力产业及标准推进委员会黄金成员

日前,“共筑新算力,智启新未来”多样性算力产业峰会2024在北京成功举办。本次峰会由中国通信标准化协会多样性算力产业及标准推进委员会主办,来自计算产业代表近400人参加。紫光同创...

2024-06-23 1349

易灵思的时钟网络问题

在T20中有16个全局时钟网络GCLK。在芯片的左右两侧各8个。全局时钟管脚或者PLL的输出时钟通过左右两个CLKMUX上全局网络。左侧的PLL(包括PLL_TL0和PLL_TL1)上左侧的CLKMUX_L;右侧的PLL(包括PLL_TR0,PL...

2024-06-20 1459

加法进位链的手动约束

在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。 在outflow下会生成一个.qplace文件 。用于指示布线的各个原语资源的分布位置 。 它的内容主是 是原语的单元名...

2024-05-20 1215

FPGA是实现敏捷、安全的工业4.0发展的关键

到2028年,全球工业4.0市场规模预计将超过2790亿美元,复合年增长率为16.3%。虽然开发商和制造商对这种高速增长已经习以为常,但其影响才刚刚开始显现。通过结合云计算、物联网(IoT)和人...

2024-05-10 663

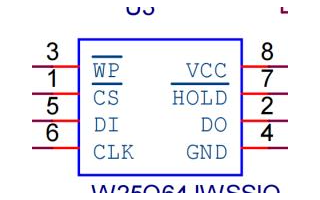

Ti60F100 内外flash操作方案

有客户认为Ti60F100内部flash容量比较小,只有16Mb,需要外挂flash.这里我们提供了内部flash和外部flash分别操作的方案。 该程序是通过SOC操作4线的外部flash和内部flash.程序先经过外部flash的擦除,写...

2024-05-20 1325

时序约束实操

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录或者新建自...

2024-04-28 2091

易灵思RAM使用--Update4

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径 在对ram进行初始化时需要指定文件路径,这里要注意'/'的方向。 (1)如果文件放在工程目...

2024-04-23 992

易灵思Jtag_bridge_loader生成-v2

Efinity版本:2023.1及以前版本。 易灵思器通过jtag bridge烧写flash时需要自己生成一个jtage birdge文件。jtage bridge 工程的目的是为了打通JTAG与flash的连接。 (1)打开IPM (2)选择Memory Controllers --> J...

2024-04-15 1217

gtkwave界面每次都更新太麻烦?来个小技巧-v1

迄今为止,大家都在吐槽gtkwave debug每次弹窗都会覆盖上一次弹窗设置好的排序和参数。下面我们分享一个可以暂时规避该问题的方法,聊以慰藉久被摧残的心~~。 (1)添加debug ,无论手动或者自...

2024-04-15 1230

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |