数十年来,光刻一直是关键的芯片生产技术。今天它仍然很重要。不过,在最近的SPIE先进光刻技术大会中,一些迹象显示,光刻界及其客户需要的微缩──字面上的微缩──事实上几乎已经有点像心理安慰了。

焦虑、紧张和忧虑或许适合用来描述今天的光刻领域。但也许后头还有更严重的苦难,因为三个主要的下一代候选光刻技术(NGL)──超紫外光(EUV)、无光罩和纳米压印──统统迟到。第四个NGL选项:定向自组装(DSA)尽管来势汹汹,但它毕竟仍处于探索阶段。

摆脱光刻技术的沮丧看来遥遥无期。今天的193nm浸入式光刻技术仍然远远领先。业界一度认为193nm浸入式光刻会在32nm遭遇极限,但令人惊讶,看来该技术可扩展到1-x纳米节点。不过,要获得这些几何图形,芯片制造商必须采取更多、更昂贵的双重曝光步骤。

而一度领先的下一代光刻候选技术EUV仍然顽固地因为缺乏光源能、阻抗和关键光罩以及量测基础设施而延迟。结果是EUV的声望持续下滑,并失去了在1-x纳米节点大展身手的良机。

NAND闪存供应商之间存在着一种对EUV的迫切感,因为需要EUV来实现进一步微缩。NAND闪存厂商将193nm浸入式技术推进到了2-x纳米节点,但他们迟早需要在1-x纳米部份用到EUV技术。“我们的确曾对EUV技术充满寄望,”SanDisk公司技术总监Tuan Pham说。SanDisk和东芝(Toshiba)在日本有一座合资的NAND晶圆厂。

当被问及是否担心EUV的地位时,Globalfoundries资深院士Harry Levinson表示:“我是必须担心。”Levinson也是该公司的光刻策略经理。

由于EUV技术持续落后于半导体的微缩脚步,设备制造商ASML Holding NV据报导仍在思考将EUV波长从13nm减少到6.7nm,以追上摩尔定律。这也意味着该产业必须发展更新和更昂贵的EUV工具技术和基础架构,这让该领域的专家们不寒而栗。

身处EUV技术阵营的领先芯片制造商,现在也对其他NGL技术持开放态度,如无光罩、纳米压印,甚至是未来的IC自组装。“赌注非常大,”VLSI Research公司总裁Risto Puhakka说。“如果你做出错误的决定,就可能导致一场灾难。”

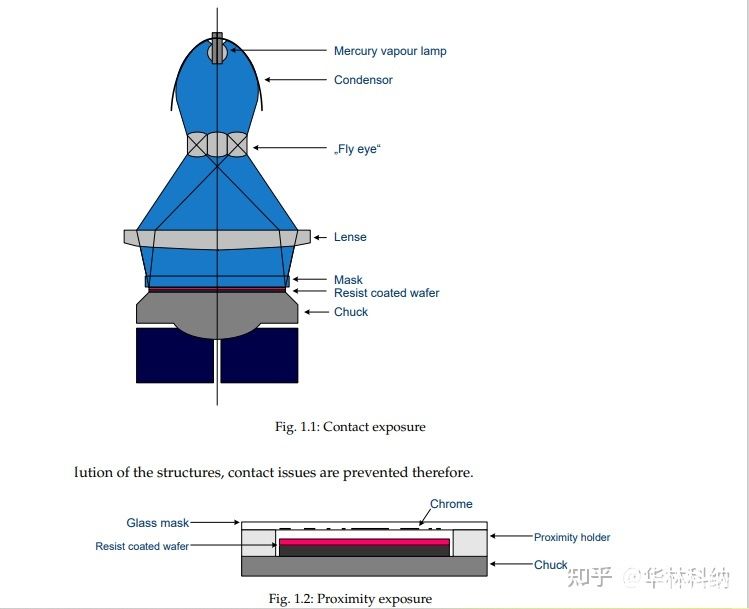

多年来,业界一直依靠传统的光学光刻来维持摩尔定律的发展。但恐怕早在上世纪70年代,光学光刻便将发展动能用光了。

图:业界预测的光刻技术发展路线图

当时,芯片制造商认为他们需要昂贵的X光光刻以微缩元件。当光学光刻技术在20世纪80年代打破了1微米壁垒时,该技术推动了对X光的需求,但最终也将X光钉入了棺木。

而后,在1990年代,关于光学光刻是末代技术的担忧再次浮现。当时有众多针对65nm芯片制造及以下制程的NGL技术,包括:157nm波长、电子束、电子束投影光刻(EPL)、超紫外光、离子束、解剖刀扫描电子束等。而在过去十年内,高指数(high-index)、纳米压印、无光罩和自组装也陆续问世。

随着时间的推移,157nm、高指数、EPL、解剖刀扫描电子束和其他技术逐渐销声匿迹。今天,余下的四个竞争者是EUV技术、纳米压印、无光罩和自组装。

在20世纪90年代,软X光技术的出现成为推动EUV的关键。包括英特尔(Intel)、超微(AMD)、摩托罗拉(Motorola)和国家实验室,开始在加州Livermore的Lawrence Livermore Labs开发EUV技术。

EUV:前景光明,道路曲折

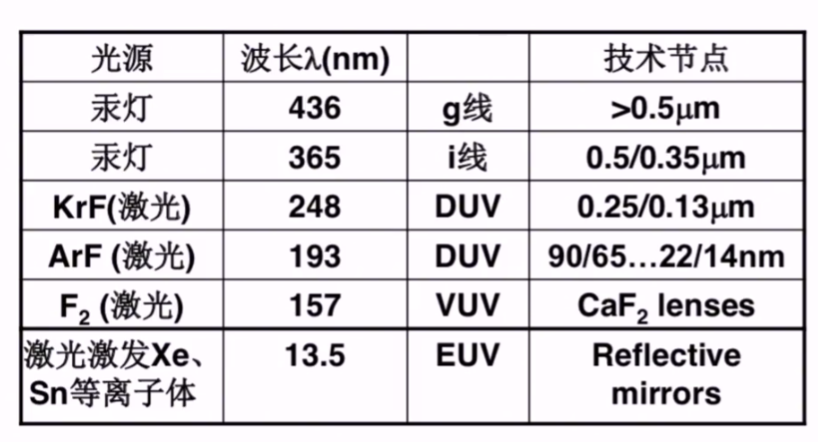

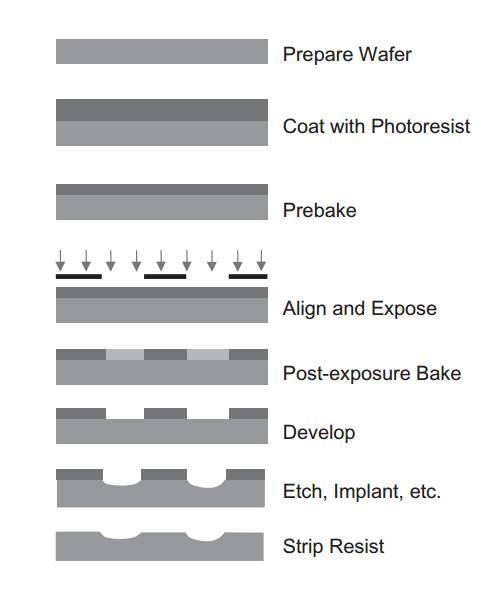

EUV技术采用13.5nm波长,在真空室中加工。其光学元件基本上是一个可透过层间干扰方式反射光线的无缺陷透镜。

EUV技术一度被认为可用于65nm节点的生产,但该技术不断延迟。而总拥有成本(COO)仍是一大问题,因为与现行的光学'光簇'(photo-cluster)售价7,000万美元相比,今天EUV的'光簇'(photo-cluster)售价高达1.2亿美元,Globalfoundries的Levinson表示。

图:EUV光刻技术原理

ASML、佳能(Canon)和尼康(Nikon)是三大主要的EUV扫描器制造商。但最近,佳能跌出了领先光刻厂商排行榜。

剩下的两家厂商ASML和Nikon则有不同的策略。ASML公司正努力让EUV技术能应用在22nm节点,但Nikon认为在16或11nm节点前,该技术都尚未就绪。“EUV生态系统也会延迟,”Nikon的新世代技术开发部门总经理Yuichi Shibasaki说。

尼康一直在开发的EUV工具称为EUV1,这是一套生产系统,据报导该系统预计在2012年左出货。

ASML公司的策略相对明确。如同其193nm浸入式策略,该公司赶在Nikon之前向客户交付试产的EUV技术工具。ASML希望客户将藉由这套试产工具获得经验,从而逼使Nikon退出市场。

截至目前,ASML已出货两套alpha EUV工具,一套交付给Albany Nanotech,另一套则交货给IMEC。ASML最近也对三星电子推出了其首款独立的预生产EUV工具NXE:3100。ASML公司刚刚付运另外一套系统给IMEC。整体来说,ASML现有六张NXE:3100订单。

NXE:3100据闻拥有27nm解析度,数值孔径(NA)为0.25,场尺寸为26nm,光刻垒对(overlay)为4nm,flare则少于5%。这套工具售价将近1亿美元。

该工具的目标是在今年底达到每小时60片晶圆的吞吐量。但目前它的吞吐量每小时仅5片晶圆。EUV工具每小时约需200W的功率来处理100~150片晶圆。目前,ASML的EUV工具仅运作在10W左右。

分析师认为,ASML公司在推动EUV的过程中已经做了非常好的努力。现在,该公司的EUV客户正在等待由几家第三方合作伙伴开发的光源能。

尽管问题频传,但ASML对光源供应商付出了无比耐心。“我们有三家全力合作的厂商,”ASML执行副总裁暨首席产品和技术长Martin van den Brink说。

有两家厂商为ASML的NXE:3100工具提供光源能:Cymer公司和Ushio公司。Cymer已经开发了基于雷射激发电浆型(laser-produced plasma, LPP)技术的光源能。据ASML表示,Cymer的LPP光源能是在11W的持续功率上运作。

竞争对手Ushio则正在开发一种基于放电技术的光源能。ASML称Ushio的光源能已达到12W功率。另一家厂商Gigaphoton公司则展现了20W的功率。

“Cymer已经售出了四套EUV光源能给客户,而且正准备推出第五套,来自三星的初步反馈指出混合图案相当良好,但吞吐量很差,”Barclays Capital分析师CJ Muse在一份报告中提到。

迫切需要光源能

我们的调查反馈仍然有差异,当前的EUV吞吐量大约每小时7-15片晶圆左右,远低于每小时60片的目标,Muse说。不过,这仍然让Cymer领先其主要竞争对手Gigaphoton约六个月。

另一个问题是,当ASML和Nikon在2012年出货其EUV工具时,EUV光源必须达到要求的目标。

“根据技术蓝图,HVM Gen 1 Cymer光源的目标是达到105W的输出功率;HVM Gen 2约达250W(根据目前揭露的设计细节),而HVM Gen 3则约350W;”Muse说。“也就是说,Cymer的脚步有点落后于功耗调整。他们目前的光源是运作在11W左右;该公司主管认为今年中他们将达到约22W,实验室的性能表现约为80W,而2011年中可望实现100W功率并推出产品,希望2011年第四季能交付给客户。”

放电激发电浆型(discharge-produced plasma,DPP)和激光激发电浆型(LPP)光源技术将以平均10~20W的曝光功率水平持续对ASML的NXE:3100设备作出贡献,咨询公司EUV Litho Inc.总裁Vivek Bakshi表示。

“我估计在2011年该数字将增加一倍达到40W,在2012年之前都无法实现100W的目标,”他说。“所以我们可以预期100W的光源与NXE:3300工具同时问世,这是一件好事,因为100W可支援每小时80片晶圆的吞吐量,一些专家认为必须为量产做准备,”他表示。

这是个好消息。现在,轮到坏消息了。“我相信,目前的光源技术版本可以达到100~150W。然而,就算达到100W,我们还是需要更多的创新,以获得150W和发展250W光源,我们还需要思考更多。”

不过,最大的问题是,EUV技术是否仍是芯片生产的首要考量。而在这其中,EUV技术仍然落后遂成为关键。SanDisk-东芝已经推出24nm的NAND元件,并宣布今年稍晚将推出1-x纳米产品。

对于,SanDisk与东芝的合资工厂使用193nm浸入式光刻技术,再加上双重曝光技术生产24nm的NAND元件,称之为隔层(spacer)技术,SanDisk的Pham说。据报导,Hynix、美光(Micron)和三星都在2-x纳米NAND生产中使用了类似技术。

在发展1-x纳米节点早期阶段,有迹象显示NAND闪存厂商SanDisk-东芝可能需要延长193nm浸入式技术,直到EUV准备好,Pham表示。

另一家厂商──三星,则一直努力推动将EUV技术导入DRAM和闪存的生产。三星认为DRAM将是率先使用EUV的应用,理论上这适用于下一代元件中难以致密的接触孔成像和间隔。

在逻辑方面,英特尔公司计划将目前的193nm浸入式光刻技术拓展到14nm逻辑节点,预计在2013年下半年实现。然后,这家芯片巨擘希望在10nm节点使用EUV技术,该目标预计在2015年下半年达到。

英特尔的10nm节点发展已历时四年多,该公司目前正在制订相关设计规则,但延迟的EUV依然未能参与此一盛晏。“EUV赶不及参与10nm节点设计规则的定义,”英特尔光刻技术总监Sam Sivakumar说。(参考阅读:英特尔10nm设计规则初定,EUV技术恐错过良机)

另外两家代工竞争对手──Globalfoundries和台积电(TSMC)则有不同的光刻技术策略。

一些人认为EUV技术在6.7nm波长的基础上将是更可行的解决方案,这很有可能推动次1nm元件的实现。但像13.5nm EUV、6.7nm等技术却面临着许多相同障碍:光源能、测量等。

基于6.7nm波长的EUV技术是一种有趣的概念,但业界至今甚至仍未征服13.5nm技术,TSMC纳米成像部门副总裁Burn Lin观察。

那么,EUV技术是不是有可能永远无法成为商业上可行的量产方案,即使投注了大量的时间和金钱?“当然,”Peterson Advanced Lithography公司总裁暨主席Jim Peterson说。Peterson Advanced Lithography是一家提供光刻产品和服务的公司。

“如果一项技术具有竞争力,那么,在进入商用化之前,它就必须取得巨大的进展,”日本凸版印刷(Toppan Printing)美国子公司Toppan Photomasks技术长Franklin Kalk说。

图:造价高昂的EUV光刻系统

Kalk坚持,EUV光罩在这点上并没有遭遇瓶颈;EUV光罩的成像非常简单,但直到EUV进入量产,业界是不会知道哪一个步骤是必须在EUV光罩上进行缺陷管理的,他表示。

Kalk和一些专家指出,EUV技术的商业化生产并不是一个问题。可能有很多公司口袋很深,也或许只有少数几家,但这些公司将继续建立先进的晶圆厂并持续EUV的研发,Kalk说。“这必然会发生。”

不过,Kalk也与其他人一样,关注EUV的潜在吞吐量。目前的共识是EUV生产工具必须达到至少每小时65~80片晶圆的吞吐量,才能让EUV具经济效益。虽然根据Kalk的建议,这将是初期令人满意的吞吐量,但长远来看,吞吐量也将有所改善,他说。

对许多人来说,EUV是唯一的下一代光刻技术。“光学光刻已经接近尾声了,”VLSI Research的CEO Dan Hutcheson和该公司的Puhakka表示。他们指出,短期内EUV是昂贵的,但也只有它才能确保竞争力。

无光罩光刻:研发进度落后,商业化进程缓慢

EUV比其他的NGL技术获得更多进展。过去十年内,一些公司开始研究新一代电子束技术,称为无光罩光刻(ML2)。包括IMS、KLA-Tencor、Mapper、Multibeam和其他公司都各自进行开发,他们的方法是在单一机台上使用多波束。理论上,ML2应该能克服与单一波束直接写入相关的吞吐量问题。

无光罩仍然缺乏资金且进度落后。要让无光罩技术商用化,业界至少要募到1亿美元,Design2Silicon(D2S)总裁兼CEO Aki Fujimura表示。

这个数字可能还被低估了。在今年的SPIE上,新创的无光罩公司Multibeam Corp.介绍了互补电子束光刻(CEBL)技术,及甚努力推动无光罩技术商业化的努力。

晶圆厂设备巨擘KLA-Tencor也提出了更多正在为无光罩技术商业化努力的细节,包括反射电子束光刻(REBL)技术在内,该计划由KLA-Tencor和DARPA公司赞助。

最初的工具使用使100 KeV源、旋转台和一个数位图案产生器(DPG)。旋转台是一个六晶圆平台。该DPG是一款CMOS芯片,带有小型、独立可控的金属单元或画素阵列,它主要用途是作为电子镜阵列。

该工具允许100万个'细光束'(beamlets)同时被暴露在芯片上。REBL的目标是在16nm节点实现晶圆成像,KLA-Tencor的REBL资深总监Paul Petric说。

最初,单柱型工具使用'静态DPG'芯片。KLA-Tencor正在开发一种基于CMOS的新型DPG,它由28个金属层和1,454个焊盘组成。然而,该公司目前在焊盘方面有些困难,他表示。

在商业化以前,REBL看来还有很长的路要走。荷兰的Mapper Lithography Bv公司在今年的SPIE上并没有提出太多实质性的进展报告。该公司提出的成果包括使用其110电子束的系统在32nm半间距节点进行晶圆成像。

纳米压印、定向自组装:仍未准备好迎接黄金时代

Mapper的pre-alpha系统获台积电采购,该系统每小时吞吐量目前为10~20片晶圆。Mapper推动其技术迈向量产的计划,是建立一个约由10套工具组成的丛集,以达到每小时约100片晶圆的吞吐量。

另一个候选的NGL技术──纳米压印,同样进展缓慢。包括EV Group、Nanonex、Nanolithosolution、Molecular Imprints Inc.(MII)、Obducat、Suss都投入了纳米压印领域。

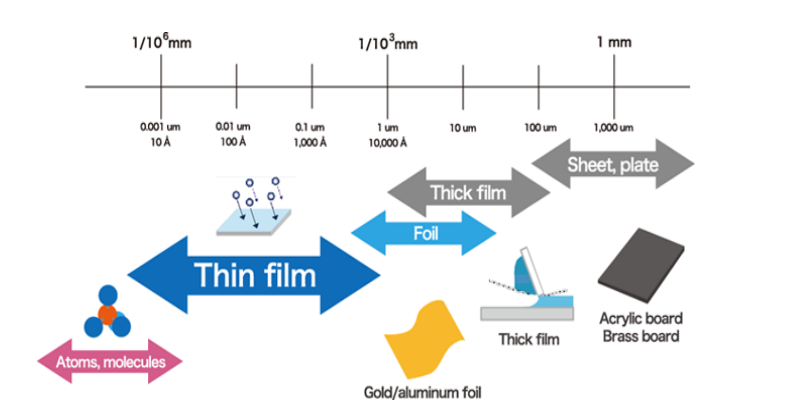

纳米压印技术并未使用昂贵的光学元件,而是采用简单的压印或热铸制程,在元件上产生特征图案。这种制程先从模板或铸模着手,然后再由电子束工具根据1:1比例的缩减机制在模板上选择特征图案。使用纳米压印工具──就像一台巨大的压印机──模板被压向加热的单层基板,最终形成微型的特征尺寸。

但纳米压印的低吞吐量、光刻垒对(overlay)、缺陷率等缺点,使其还无法成为主流制程。

出于这些原因,纳米压印一直无法用于芯片生产,至少现在还没有办法。它仍然停留在研发实验室或大学研究阶段。

几年前,MII公司出货了纳米压印工具给东芝公司。但在今年的SPIE上,东芝表示纳米压印仍然没有准备好迎接其黄金时代。

但另一方面,纳米压印也正在取得进展。同样在SPIE上,Sematech“展示了具体缺陷率0.09cm2的良好结果,”MII公司总裁暨CEO Mark Melliar-Smith表示。“由于这已经低于东芝所设定的0.1cm2水平,我认为我们正在走向成功。”

MII展示了多款已在过去12个月内出货的工具平台。包括一款针对CMOS的工具,“5xx系列每小时吞吐量为20片晶圆,而且拥有良好的光刻垒对(overlay),”他表示。

但纳米压印在其最大的潜在市场──硬盘(HDD)──也有可能延误。目前硬盘制造商使用溅镀技术在硬盘上实现磁性介质,但这些产品很快地就会遭遇1TB容量的极限。

大约在今年底左右,硬盘制造商们将使用一种名为'位元规则介质'(bit-patterned media)的下一代技术来生产硬盘;这种技术据称可将传统的储存容量扩展到10TB。

在争相取代EUV的NGL技术中,定向自组装(DSA)在今年SPIE上的表现最为抢眼。DSA技术概念听起来像科幻小说,它是将块状共聚合物(block copolymer)或是聚合物混合物(polymer blend)沉积在基板上,通常采用旋转涂布,并经由退火过程以'指挥'其形成有序的结构。研究人员指出,DSA相容于传统的193nm光刻设备,不再需要双重曝光步骤。

但DSA仍处在研发阶段,但已经有一些机构提出令人振奋的报告,包括IBM、应用材料等。JSR稍早前也才针对次20nm半间距节点推出了DSA技术,这是该公司与IBM研发协议的一部份

电子发烧友App

电子发烧友App

评论