可编程、可配置与IP篇

ECP5“打破陈规” 挑战FPGA巨头

在FPGA领域,与赛灵思(Xilinx)和Altera这两个追求极致密度、超高传输速率、巨量晶体管数、最新工艺技术的巨头不同,Lattice(莱迪思)走的是低成本、低功耗和小形状因数之路。

Lattice总裁兼CEO Darin Billerbeck形容自身优势时,用了快速和敏捷(Agility)这两个词,目的就是使用户争取到足够快的上市时间。

他特别提到了两个“最”产品。一个是号称全球最小FPGA的iCE40,价格不到50美分,功耗最低25μW,1.4x1.48mmBGA封装。

另一个是面向视频安全监控、人机接口和移动终端的MachXO3,其每个I/O接口的成本不到1美分,2.5x2.5和3.8x3.8mm2的WLCS封装。

Lattice方面表示,除了上面差异化技术外,将以最新开发出的ECP5 FPGA系列,在小型蜂窝网络、微型服务器、宽带接入、工业视频等大批量应用中,向两大巨头的中低端产品发起挑战。

一段时期以来,赛灵思和Altera一直宣称要用FPGA取代ASIC和ASSP。而Lattice则表示要让ECP5在10万LUT以下的设计中,成为ASIC和ASSP的辅助设计伙伴,以弥补ASIC的成本问题和ASSP不够灵活的缺陷。

Darin Billerbeck称,ECP5系列在成本、功耗和密度3个方面“打破了陈规”:

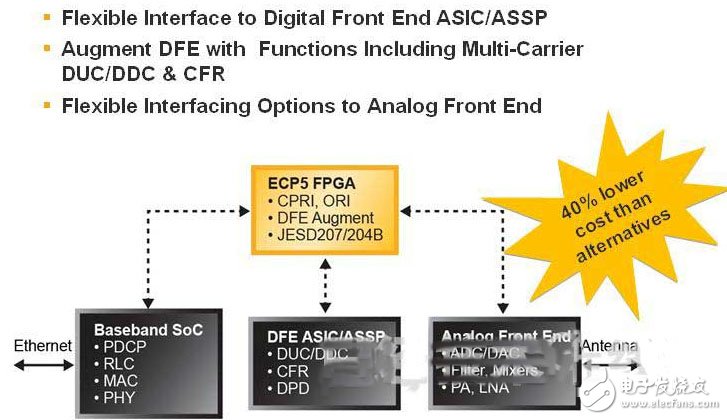

①2.5万~8.5万LUT在提高提高设计灵活性的同时,比市场上其他竞争产品的成本最多降低了40%。在小型蜂窝基站中的应用如图1所示。

图1 ECP5系列在小型蜂窝基站中作为ASIC和ASSP的辅助设计

②使用单通道3.25Gpbs SERDES,即一路PCIe时,最低功耗约为0.25W(见图2)。若采用4路PCIe,功耗也不到0.5W。静态功耗在64~78mW。在150MHz典型应用中的功耗,比竞争产品最多降低30%。

图2 ECP5系列在安防监控摄像机方案中,使用单通道3.25Gpbs SERDES,即一路PCIe时,功耗约0.25W。

在现场演示中,用Diamond软件工具测得8.5万LUT设计的典型功耗约315mW;2.5万LUT时为264mW。

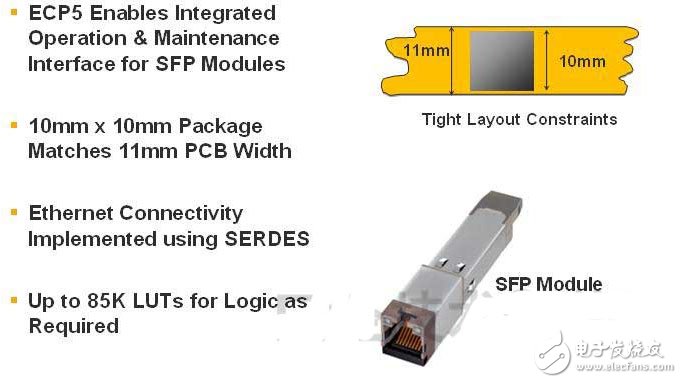

③8.5万LUT和SERDES封装在10x10mm2BGA内(见图3),功能密度,即每平方毫米的LUT数量,比竞争产品高2倍以上。40nm工艺的ECP5系列比竞争产品28nm工艺的芯片尺寸还小。

图3 ECP5系列采用10x10mm2BGA封装,适于宽带接入设备的智能小型可插拔(SFP)收发器方案。

据悉,ECP5预计将于2014年8月上市,并在2016年进入28nm工艺。

另外,市场方面,目前亚太地区营收占Lattice全球的60%,其中,中国占亚太区的70%。

神秘又熟悉的IP商

本次硅谷之旅第二天采访的Arteris,是一家网络芯片(Network-on-Chip)互连IP和工具供应商。尽管已有10多年的历史了,但是它并不像处理器IP商ARM、MIPS、Tensilica、CEVA或Cadence、Synopsys那样有很高的知名度,因而对于大多数电子工程师可能显得有些神秘。

不过在半导体设计界,三星、高通、TI、飞思卡尔、ST、瑞萨电子、东芝和Altera等大牌都是Arteris的用户。而且,中国大陆半导体设计三剑客海思、展讯、锐迪科,及全志科技、瑞芯微、珠海炬力和虹晶科技等不少公司,也采用了Arteris的FlexNoC互连IP进行SoC设计。据IHS iSuppli的调查报告,中国大陆多数半导体公司都得到了FlexNoC互连IP的授权。

最近,***创意电子(GUC)也得到了FlexNoC互连IP的授权,用于16nm移动设备应用处理器SoC IP验证平台的设计。

对于Arteris这样既神秘又熟悉的厂商,在介绍其独特技术之前,笔者觉得有必要对各位看官先普及一下它的历史。

Arteris在2003年由3位法国人创立,总部设在巴黎。次年收到第一笔风险投资。2005年,现任董事长、总裁兼CEO K. Charlie Janac加盟,担任CEO一职。2006年,第一个互连IP产品NoCSolution问世,并马上就拿到了100万美元的授权许可收入。

2007年,在得到由Synopsys领头的新一轮投资后,把公司总部从巴黎搬到了硅谷。同年,TI的OMAP4应用处理器采用了NoCSolution的IP。2009年,第二代技术FlexNoC上市。随后,得到了高通风险投资(欧洲)、ARM、日本Innotech等的第三轮投资。2010年,与三星和高通合作推出FlexLLI Interchip Link IP技术。

2011年,即公司成立的第8年,才开始盈利。2012年,全球60%的移动设计都采用了FlexNoC互连IP。2013年,在智能手机市场收获颇丰。同年底,被高通以独特的交易方式***了IP和工程团队。2014年,Arteris宣布雇佣新的工程领导团队。

下面就来看看Arteris的FlexNoC互连IP的独到之处。

从事芯片设计的工程师都知道,高效的互连是SoC盈利的关键。同时,在竞争激烈的市场上,灵活的拓扑架构对产品差异化非常重要。

Arteris营销副总裁Kurt Shuler幽默地表示:“Arteris is Switzerland。”对这句话,不只是笔者,就连一位来自欧洲的资深媒体同行也大惑不解:“你们不是美国公司吗?怎么又是瑞士的了?”

Shuler解释道:“大家知道,瑞士是中立国。实际上我的意思是,Arteris是中立的。也就是说,我们自己不设计生产任何芯片,而是为所有的网络芯片设计公司提供互联IP,且与任何协议无关。虽然他们是竞争关系,但我们是中立的。”

这时,现场响起一片会意的笑声。

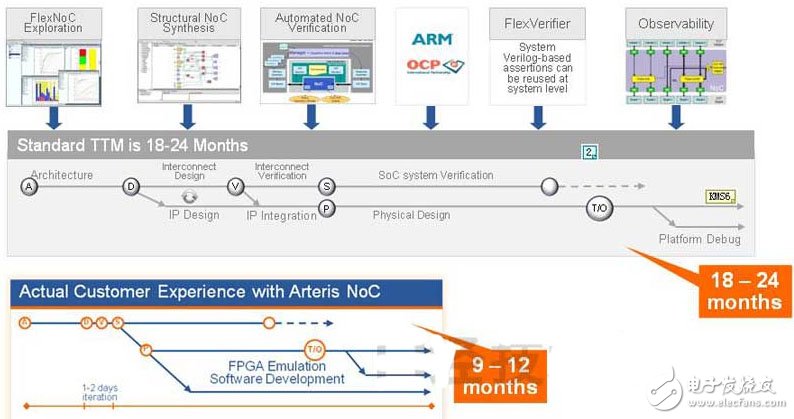

他强调,Arteris的NoC互连IP技术可把用户通常12~18个月的设计周期缩短到9~12个月(见图4)。同时,NoC互连工具还可提升SoC的生产力(见图5)。

图4 Arteris的NoC互连IP技术可将设计周期缩短为9~12个月

图5 NoC互连工具可提升SoC的生产力

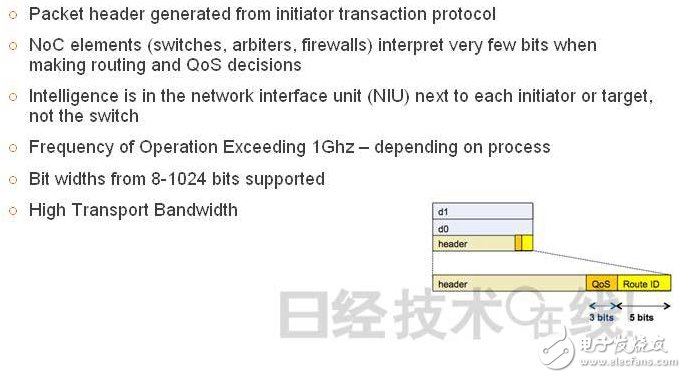

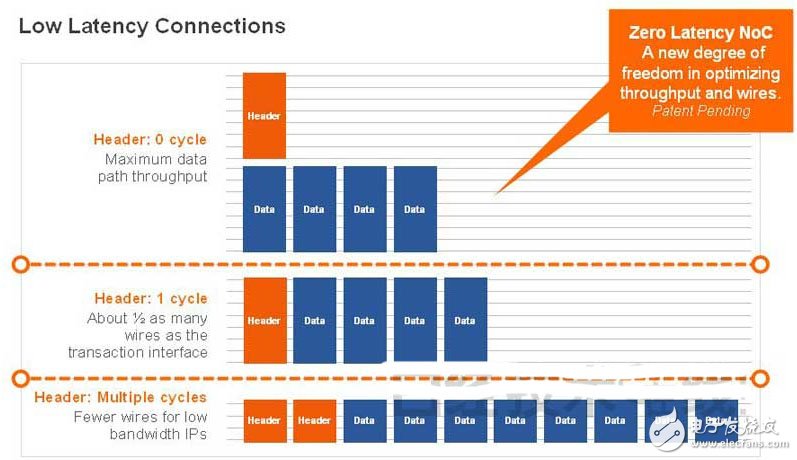

具体地,NoC互连IP技术的工作频率可达1GHz以上(见图6),支持CPU到存储器的高速数据传输;极低的连接延迟(见图7);易于布局布线等。

图6 NoC互连IP技术支持1GHz以上的工作频率和高传输带宽

图7 NoC互连IP技术具有极低的连接延迟特性

此外,与传统的混合总线互连架构比,NoCIP架构的线路量少了50%,最高工作频率也高于后者,带宽提高了1倍,可连接上百个IP块,功耗不到1W,延迟特性相当甚至更好。

Shuler表示,目前有56个用户,85项流片及44个完整的芯片设计,用户的芯片发货量已达1亿多片。

开辟一个崭新的半导体市场

相比模拟、电源和分立器件300亿美元以上的市场,FPGA和可编程微控制器分别有50多亿和90多亿美元的市场,Silego所在的可配置混合信号芯片(CMIC)市场潜在容量只有30亿美元左右。

不过,Silego营销副总裁John McDonald(见图8)表示,可配置混合信号芯片或称“可编程模拟技术”开辟了一个崭新的半导体“蓝海”市场,正因为如此,这个市场的竞争不像前几个市场那样激烈。消费类、计算、通信和工业领域的广泛应用需求正推动这个市场呈现出爆炸式增长的态势。

图8 Silego营销副总裁John McDonald

Silego包括混合信号阵列GreenPAK、电源管理芯片GreenFET、定时产品GreenCLK和接口ASSP在内的4类芯片,近4年内的总出货量已过10亿,2012和2013年的出货量更是分别达到了2.7亿和4.2亿。

目前最小的GreenPAK3采用1.6 mm x1.6 mm X0.55mm,12引脚STQFN封装,其厚度比1美分硬币还薄(见图9)。在这样小的芯片内,集成了模拟元件、数字逻辑、可编程互连架构、I/O及非易失性存储器等。主要可用于替代4~8位MCU、胶合逻辑、电平转换器和电压监控器等。“工程师用所提供的GPAK开发工具,在几分钟内就可搞定所需的配置和编程。”McDonald表示。

图9 GreenPAK3采用1.6x1.6mm212引脚STQFN封装,厚度比1美分硬币还薄。

GreenPAK3低成本、低功耗的特点,有助于在可穿戴设备、移动终端及PC市场上,实现差异化设计和产品快速上市。

另外,McDonald透露,Silego在中国设有一个研发中心。计划在2014年推出8款新产品,同时,将进一步加强与英特尔和nVidia的合作关系。

电子发烧友App

电子发烧友App

评论