前面介绍了一些中规模时序逻辑电路,如集成移位寄存器,二进制、十进制计数器等。下面将介绍这些集成器件组成的时序电路及其设计。

6.5.1中规模同步时序逻辑电路的分析

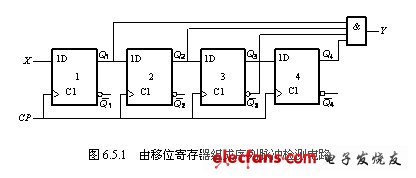

1.移位寄存器可以用于输入脉冲序列的检测

在数字系统中有时需要将输入数据序列中的输入数据进行检测,以满足设计的要求。在图6.5.1中,就是一个序列脉冲数据检测器,它能够检测输入端X中是否有数据序列1011段出现,如果有此数据序列,则输出端Y为1,否则为0。电路由4个D触发器组成四位右移移位寄存器,输出端![]() ,输出端Y只有在4个D触发器输出

,输出端Y只有在4个D触发器输出![]() 时,才为1。假设输入数据先送最高位1,加入时钟脉冲,然后送次高位0,又加入时钟脉冲,然后分别送后面几位数,在4个脉冲之后,则

时,才为1。假设输入数据先送最高位1,加入时钟脉冲,然后送次高位0,又加入时钟脉冲,然后分别送后面几位数,在4个脉冲之后,则![]() ,Y= 1。表6.5.1是一系列输入数据与输出的关系。

,Y= 1。表6.5.1是一系列输入数据与输出的关系。

|

|

||||||||||

|

CP |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

X |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

|

0001 |

0010 |

0101 |

1011 |

0110 |

1101 |

1011 |

0110 |

1101 |

1010 |

|

Y |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

从表6.5.1中可以看出,输入序列码元的检测具有重复性,在第4个输入数据后只要输入011即可在输出端得到1,因为在此之前已经输入了数据1,寄存在触发器中。

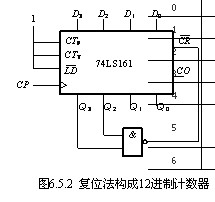

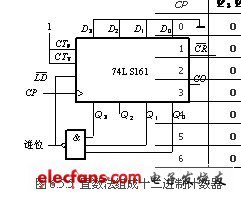

2.用十六进制计数器组成任意进制数计数器

十六进制计数器74LS161具有可预置数的功能,有进位输出、置数输入、复位和保持功能端,可以利用其置数和复位端来获得十六进制数以下的其他任意一种计数器。要获得十六进制数以上的任意一种计数器,需要多片74LS161组成电路。下面分别介绍利用复位端和置数端得到任意一种计数器的方法。

复位法 在图6.5.2电路中,将输出端![]() 和

和![]() 与-非运算后送复位端

与-非运算后送复位端![]() ,复位端只有在输入低电平时才可以使计数器复位,复位后输出端

,复位端只有在输入低电平时才可以使计数器复位,复位后输出端![]() 。在正常计数时输出端按照二进制计数,当

。在正常计数时输出端按照二进制计数,当![]() 和

和![]() 输出高电平时,

输出高电平时,![]() 获得低电平,计数器复位,复位结果使得

获得低电平,计数器复位,复位结果使得![]() 端的低电平迅速消失,可以用表6.5.2来说明图6.5.2的计数过程。

端的低电平迅速消失,可以用表6.5.2来说明图6.5.2的计数过程。

从表6.5.2可以看出,计数器的输出状态出现1100时,计数器被复位为0000,状态1100的维持时间非常短暂,约为门电路的延迟时间,所以状态值1100不能稳定维持,在考虑计数器总的状态时一般忽略状态1100的出现。所以图6.5.2组成的是的所有计数循环为0000→0001→0010→…→1011→0000共12个有效状态循环,所以是十二进制计数器。

|

表6.5.2 图6.5.2计数过程 |

|||||||||

|

CP |

|

CP |

|

||||||

|

0 |

0 |

0 |

0 |

0 |

7 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

8 |

1 |

0 |

0 |

0 |

|

2 |

0 |

0 |

1 |

0 |

9 |

1 |

0 |

0 |

1 |

|

3 |

0 |

0 |

1 |

1 |

10 |

1 |

0 |

1 |

0 |

|

4 |

0 |

1 |

0 |

0 |

11 |

1 |

0 |

1 |

1 |

|

5 |

0 |

1 |

0 |

1 |

12 |

|

1 |

0 |

0 |

|

6 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

0 |

在这里我们看出实际上输出端有13个状态出现,不过状态值1100的时间很短,采用这种简单的复位法获得任意进制计数器,如果复位的结果使得![]() 先被复位为0,假设此时

先被复位为0,假设此时![]() 还没来得及复位,由于

还没来得及复位,由于![]() 已被复位为0,

已被复位为0,![]() 的低电平马上消失,这样就使得

的低电平马上消失,这样就使得![]() 没有被复位而复位电平就消失了,结果输出可能为0100,不是表6.5.2的结果。如果假设的是

没有被复位而复位电平就消失了,结果输出可能为0100,不是表6.5.2的结果。如果假设的是![]() 先复位,

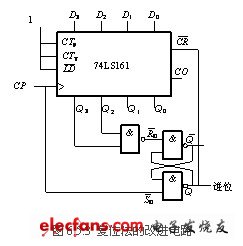

先复位,![]() 还没来得及复位则复位电平就消失了,则得到的复位结果可能是1000。集成电路内部门电路的延迟时间具有不确定性,所以采用这种方法来组成任意进制的计数器,可能会使有些输出端没有被复位,也就达不到设计要求。解决的办法就是采用RS触发器来将复位信号保存下来,使得计数器内部得电路获得可靠得复位。改进得电路结构形式如图6.5.3所示。

还没来得及复位则复位电平就消失了,则得到的复位结果可能是1000。集成电路内部门电路的延迟时间具有不确定性,所以采用这种方法来组成任意进制的计数器,可能会使有些输出端没有被复位,也就达不到设计要求。解决的办法就是采用RS触发器来将复位信号保存下来,使得计数器内部得电路获得可靠得复位。改进得电路结构形式如图6.5.3所示。

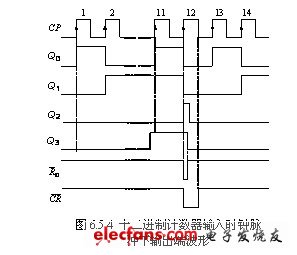

图6.5.3中RS触发器的作用是将复位信号的低电平保存一个时钟脉冲的高电平时间,以使得计数器的输出端可以有足够的时间来获得复位,时钟信号引入RS触发器中的![]() 端的作用是当计数器复位后,用时钟脉冲的下降沿清除

端的作用是当计数器复位后,用时钟脉冲的下降沿清除![]() 的低电平,使计数器可以继续计数工作。其工作过程可以用图6.5.4的时序电压波形图来表示。图中表示出了时钟脉冲作用下输出端和复位端的波形,在第11个时钟脉冲到来时,输出端

的低电平,使计数器可以继续计数工作。其工作过程可以用图6.5.4的时序电压波形图来表示。图中表示出了时钟脉冲作用下输出端和复位端的波形,在第11个时钟脉冲到来时,输出端![]() ,在第12个脉冲到来时,输出端

,在第12个脉冲到来时,输出端![]() ,此刻

,此刻![]() ,

,![]() ,RS触发器输出为

,RS触发器输出为![]() ,计数器复位,则

,计数器复位,则![]() ,因为CP =1,所以在第12个时钟脉冲高电平期间

,因为CP =1,所以在第12个时钟脉冲高电平期间![]() 为低电平。改进的电路可以从RS触发器的Q输出端获得整个计数器进位信号的输出,此时74LS161的进位输出端CO一直为高电平,没有进位结果输出,不能作为整个计数器的进位端。

为低电平。改进的电路可以从RS触发器的Q输出端获得整个计数器进位信号的输出,此时74LS161的进位输出端CO一直为高电平,没有进位结果输出,不能作为整个计数器的进位端。

置数法 复位法获得任意进制计数器的方法缺点是计数器的输出端出现短暂的电平尖峰,如果将输出端接入其他逻辑电路中,可能会使计数结果发生错误,改进的方法就是利用计数器的置数端组成任意进制计数器。图6.5.5是利用74LS161的置数端![]() 组成的十二进制计数器。

组成的十二进制计数器。

|

表6.5.3 图6.5.5计数过程 |

|||||||||

|

CP |

|

CP |

|

||||||

|

0 |

0 |

0 |

0 |

0 |

7 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

8 |

1 |

0 |

0 |

0 |

|

2 |

0 |

0 |

1 |

0 |

9 |

1 |

0 |

0 |

1 |

|

3 |

0 |

0 |

1 |

1 |

10 |

1 |

0 |

1 |

0 |

|

4 |

0 |

1 |

0 |

0 |

11 |

1 |

0 |

1 |

1 |

|

5 |

0 |

1 |

0 |

1 |

12 |

0 |

0 |

0 |

0 |

|

6 |

0 |

1 |

1 |

0 |

|

|

|

|

|

图6.5.5中电路,只有当计数器输出端![]() 时,与-非门输出为0,

时,与-非门输出为0,![]() ,此时计数器还不置数,当下一个时钟脉冲的上升沿到来时,计数器置数,将预置数

,此时计数器还不置数,当下一个时钟脉冲的上升沿到来时,计数器置数,将预置数![]() 送入输出端,计数状态之间的转换可以用表6.5.3来表示。图6.6.6为该计数器的电压波形图。

送入输出端,计数状态之间的转换可以用表6.5.3来表示。图6.6.6为该计数器的电压波形图。

利用置数法组成任意进制的计数器,从计数器的输出数值来获得置数控制端的低电平信号,74LS161的置数是在时钟脉冲的作用下同步完成的,而复位法是异步复位的,即不需要时钟作用即可复位。所以在图6.5.6中,第11个时钟脉冲到来时,输出为1011,此时![]() ,做好置数准备,在第12个时钟到来时将计数器置数。在这里置入的数值为0000,其状态转换图与复位法的状态转换图相同,不同的是,置数法中的计数器输出端不会出现电平毛刺。由于置数数值来自置数数据端,所以同样实现的是十二进制计数,改变不同的置入数,可以得到不同的状态转换图。

,做好置数准备,在第12个时钟到来时将计数器置数。在这里置入的数值为0000,其状态转换图与复位法的状态转换图相同,不同的是,置数法中的计数器输出端不会出现电平毛刺。由于置数数值来自置数数据端,所以同样实现的是十二进制计数,改变不同的置入数,可以得到不同的状态转换图。

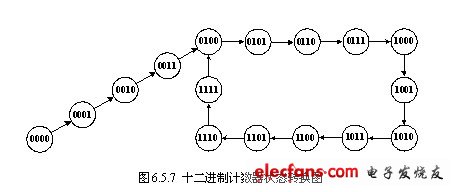

在图6.5.5中,若将置入数值设定为![]() 、

、![]() ,置数端控制端

,置数端控制端![]() ,则正常计数后的状态循环如图6.5.7所示。

,则正常计数后的状态循环如图6.5.7所示。

利用置数控制端![]() 来控制计数器什么时候置数,并且设定不同的置数输入数值,实现同样进制数的计数,可以有不同的状态转换图。送入置数控制端

来控制计数器什么时候置数,并且设定不同的置数输入数值,实现同样进制数的计数,可以有不同的状态转换图。送入置数控制端![]() 的值可以从计数器的输出端经门电路运算而得,也可以从进位端CO得到。

的值可以从计数器的输出端经门电路运算而得,也可以从进位端CO得到。

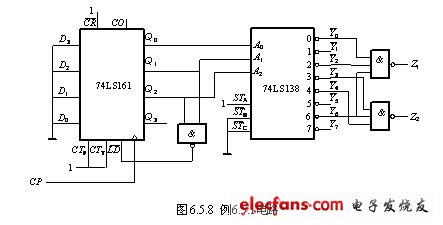

例6.5.1 由同步计数器74LS161和3线-8线译码器74LS138以及门电路组成的电路如图6.5.8所示,试分析:

(1)74LS161组成的计数器的模值,

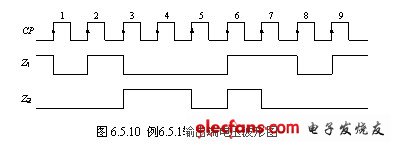

(2)画出电路在时钟信号作用下输出端Z1、Z2的电压波形图,

(3)电路的逻辑功能。

解:(1)图6.5.8中电路分为三个部分,左部分为脉冲计数电路,中间部分为译码电路,右部分为组合输出电路。脉冲计数电路是由置数法组成的计数器,置数控制端![]() 的低电平取决于74LS161的计数输出端

的低电平取决于74LS161的计数输出端![]() 和

和![]() 的与-非结果,置入的数值为0000,根据前面的分析结果可以作出计数状态转换图如图6.5.9所示。从状态转换图可以看出由74LS161组成的是七进制计数器。即74LS161组成了模值为7的计数器。

的与-非结果,置入的数值为0000,根据前面的分析结果可以作出计数状态转换图如图6.5.9所示。从状态转换图可以看出由74LS161组成的是七进制计数器。即74LS161组成了模值为7的计数器。

(2)74LS138的译码地址输入端来自74LS161的输出端![]() 、

、![]() 和

和![]() ,所以地址输入端A2A1A0的编码是二进制数的000至110。译码器输出端是低电平有效译码输出。从以上两部分电路可以看出,在输入时钟信号的作用下,译码器的输出端依次单独输出低电平,这一点与前面讲到的CC4017有相似之处,不过CC4017是高电平有效输出。

,所以地址输入端A2A1A0的编码是二进制数的000至110。译码器输出端是低电平有效译码输出。从以上两部分电路可以看出,在输入时钟信号的作用下,译码器的输出端依次单独输出低电平,这一点与前面讲到的CC4017有相似之处,不过CC4017是高电平有效输出。

电路输出端的逻辑表达式为:

(6.5.1)

(6.5.1)

根据以上分析作出输出端Z1、Z2的真值表,如表6.5.4所示。由于74LS161工作在七进制计数状态,故正常计数时Q3不会出现高电平,所以表中没有列出Q3的状态。

|

表6.5.4 例6.5.1真值表 |

||||||||||||

|

CP |

Q3 |

Q3 |

Q3 |

|

|

|

|

|

|

|

Z1 |

Z2 |

|

0 1 2 3 4 5 6 7 |

0 0 0 0 1 1 1 0 |

0 0 1 1 0 0 1 0 |

0 1 0 1 0 1 0 0 |

0 1 1 1 1 1 1 0 |

1 0 1 1 1 1 1 1 |

1 1 0 1 1 1 1 1 |

1 1 1 0 1 1 1 1 |

1 1 1 1 0 1 1 1 |

1 1 1 1 1 0 1 1 |

1 1 1 1 1 1 0 1 |

1 0 1 0 0 0 1 1 |

0 0 0 1 1 0 1 0 |

根据式(6.5.1)以及上面的分析可以画出输出端Z1和Z2在时钟信号作用下的电压波形图,如图6.5.10所示,图中假设计数器的初始状态输出为0000。

(3)通过分析可知,实现的逻辑功能是七进制计数-译码电路。

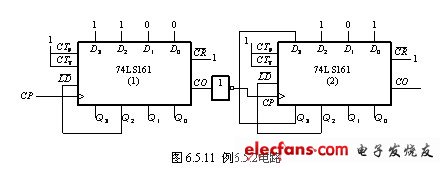

例6.5.2 分析图6.5.11所示电路的计数分频比

解:电路由两片74LS161计数器组成整个计数系统,计数脉冲的输入端加在74LS161(1)的时钟端,74LS161(1)计数器的进位输出求非作为时钟信号加到74LS161(2)计数器中,计数结果的输出端从74LS161(2)的进位输出。

|

表6.5.5 74LS161(1)的状态转移表 |

||||

|

CP |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 1 2 3 4 |

0 1 1 1 1 |

0 1 1 1 1 |

0 0 0 1 1 |

0 0 1 0 1 |

|

表6.5.6 74LS161(2)的状态转移表 |

||||

|

CP |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 1 2 3 4 5 6 7 |

0 0 0 0 1 1 1 1 |

0 1 1 1 0 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

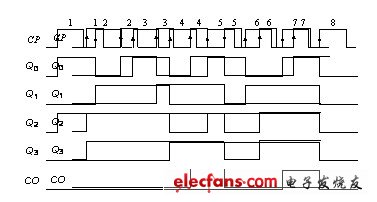

74LS161(1)计数器是利用置数端来获得任意进制计数器的。可以假设计数器的初始状态为0000,此时![]() ,74LS161(1)计数器工作在置数准备阶段,输入计数脉冲时,完成置数操作,将74LS161(1)计数器输出置为1100,然后在计数脉冲作用下继续计数,当计数到输出为1111时,产生进位信号,此进位信号送入74LS161(2)计数器计数。所以可作出74LS161(1)计数器的状态转移表,如表6.5.5所示。图6.5.12为74LS161(1)的电压波形图。

,74LS161(1)计数器工作在置数准备阶段,输入计数脉冲时,完成置数操作,将74LS161(1)计数器输出置为1100,然后在计数脉冲作用下继续计数,当计数到输出为1111时,产生进位信号,此进位信号送入74LS161(2)计数器计数。所以可作出74LS161(1)计数器的状态转移表,如表6.5.5所示。图6.5.12为74LS161(1)的电压波形图。

74LS161(2)计数器也是利用置数端来获得任意进制计数器,不同的是其时钟计数端取自74LS161(1)进位的非,而且其置数端与计数输出端Q3有关,应用前面同样的分析方法,可以列出其74LS161(2)的状态转移表,如表6.5.6所示。从表中可以看出74LS161(2)组成的是八进制计数器。画出其电压波形图为图6.5.13所示。

结合图6.5.12和图6.5.13,可以看出74LS161(1)是每来5个计数脉冲进位输出一个高电平,并且这个高电平求非后送入74LS161(2)作为计数脉冲的输入,总的进位结果输出在74LS161(2)的CO端,所以整个电路的进位输出是在输入40(5×8)个计数脉冲后得到进位的,总电路是四十进制计数器,总进位端是对输入计数脉冲的40分频。

6.5.2中规模同步时序逻辑电路的设计

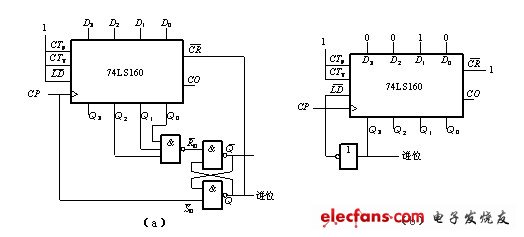

例6.5.3 用74LS160设计七进制计数器,分别用复位法和置数法实现电路。

解:74LS160为十进制计数器,其计数、输入、输出以及其他功能端与74LS161均相同,不同之处在于74LS160的计数输出状态循环是:0000→0001→0010→0011→0100→0101→0110→0111→1000→1001,比74LS161少了6个状态。所以,由74LS160组成十以下的任意进制计数器的方法可以仿照前面74LS161的方法来设计。

(1)采用异步复位法

七进制计数器由七个状态的循环,可以取这七循环状态为000→001→010→011→100→101→110,为了能够在计数状态循环中能够跳过0111、1000和1001这三个计数状态,选取输出端的输出数值0111作为复位信号,而计数输出的最高位Q3在七进制计数状态循环中没有用到,所以舍弃Q3作为复位信号,设计电路时可以将计数输出端Q2、Q1和Q0与-非,然后经RS触发器与![]() 相连即可。设计电路为图6.5.14(a)所示,进位信号从RS触发器的Q获得。

相连即可。设计电路为图6.5.14(a)所示,进位信号从RS触发器的Q获得。

(2)采用同步置数法

从74LS160的计数状态循环中,可以看出选择其中的7个状态循环即可实现七进制计数。计数输出端的最高位Q3只出现了两次高电平,可以利用Q2的高电平来产生置数信号,也就是在计数状态中利用到了状态1000,没有利用状态1001,所以再选择其他6个状态即可,在此选择0010作为起始状态,所以置入的数值也就为0010。置数法中实现七进制计数用到的状态循环为0010→0011→0100→0101→0110→0111→1000。设计电路如图6.5.14(b)所示,进位信号从Q3获得。

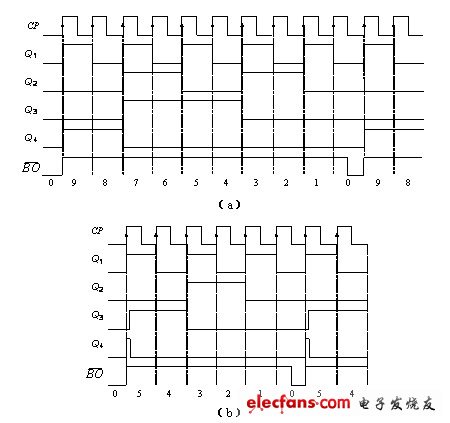

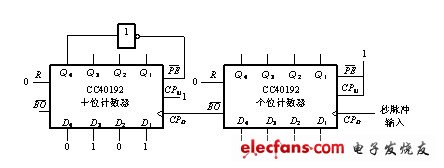

例6.5.4 利用CC40192设计一个60秒倒计时电路。

解:CC40192为双时钟可预置十进制减法计数器。其功能表见表6.3.9所示,简图表示见图6.3.22所示。CC40192有两个时钟端,分别用于加计数和减计数,其预置数是异步实现的,即只要预置端![]() 出现低电平就完成置数,与时钟端无关。

出现低电平就完成置数,与时钟端无关。

设计中要求为60秒倒计时,所以输入的计数脉冲的周期为1秒即可,秒脉冲的获得可以用振荡电路获得(在第七章介绍)。倒计时电路即为减法计数电路,根据题意设计一个60进制的减法计数器即可,CC40192作减法计数器的计数脉冲输入端为CPD,借位输出端为![]() 。CC40192的最大计数输出为十,所以要用到两片芯片。一片作为个位为十进制的减法计数器,一片为十位六进制减法计数器。秒脉冲输入到个位的减法计数器中。十位的计数脉冲的输入端取自个位计数器的借位输出。

。CC40192的最大计数输出为十,所以要用到两片芯片。一片作为个位为十进制的减法计数器,一片为十位六进制减法计数器。秒脉冲输入到个位的减法计数器中。十位的计数脉冲的输入端取自个位计数器的借位输出。

列出十位和个位的状态转移表如表6.5.7所示。

|

表6.5.7 六十进制计数器个位和十位的状态转换表 |

|||||||||

|

十位计数状态循环 |

个位计数状态循环 |

||||||||

|

计数脉冲 |

Q4 |

Q3 |

Q2 |

Q1 |

计数脉冲 |

Q4 |

Q3 |

Q2 |

Q1 |

|

0 1 2 3 4 5 |

0 0 0 0 0 0 |

0 1 1 0 0 0 |

0 0 0 1 1 0 |

0 1 0 1 0 1 |

0 1 2 3 4 5 6 7 8 9 |

0 1 1 0 0 0 0 0 0 0 |

0 0 0 1 1 1 1 0 0 0 |

0 0 0 1 1 0 0 1 1 0 |

0 1 0 1 0 1 0 1 0 1 |

由于个位的减法计数为十进制,所以只需将用于十位减法计数的计数器设计为六进制减法计数器,然后两片计数器连接即可。从表6.5.7可以看出十位减法计数的状态循环中,减法计数是从0101开始的,所以设计十位CC40192的置入数值为0101。CC40192正常的减法计数中,计数输出的状态0000之后的状态为1001,可以利用Q4的高电平来产生异步置数。所以可作出十位和个位计数器电压波形图如图6.5.15所示。

从图6.5.15可以看出,借位输出端的上升沿是在计数器减法计数输出由0000→1001时产生的,所以可以利用个位计数器的借位输出的上升沿作为十位计数的脉冲输入。当个位计数输出由0000→1001时,十位同时进行减法计数,也由0000→1001,十位计数输出端Q4出现高电平,对之求非即得低电平,此低电平作为置数控制信号送![]() 端,十位计数器置数,输出为0101。根据这样得设计方法画出设计电路如图6.5.16所示。 从图6.5.16可以看出,若要利用CC40192来设计其他进制得计数器,可以采用类似得方法进行。

端,十位计数器置数,输出为0101。根据这样得设计方法画出设计电路如图6.5.16所示。 从图6.5.16可以看出,若要利用CC40192来设计其他进制得计数器,可以采用类似得方法进行。