与同步时序逻辑电路相比,异步时序逻辑电路没有统一的时钟,各级触发器的状态变化不是在统一的时钟作用下完成的,电路的状态是直接由输入信号决定,电路结构简单,但是速度慢,随着位数的增加,计数器从接受计数脉冲到稳定状态的建立,时延也大大增加。

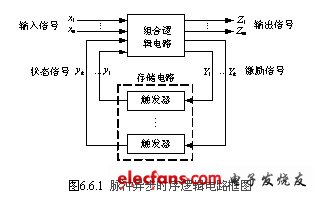

异步时序逻辑电路根据输入信号的形式不同分为脉冲异步时序逻辑电路和电平异步时序逻辑电路。脉冲异步时序逻辑电路框图如图6.6.1所示,其电路由主要由触发器组成,与同步时序逻辑电路相似,不同之处在于触发器中的时钟不统一,分析方法和同步时序逻辑电路的方法也基本相同。

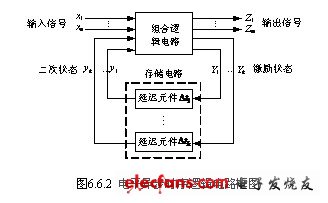

电平异步时序逻辑电路框图如图6.6.2所示,其电路主要由带反馈的组合延迟单元电路组成,其分析方法和前者完全不同,主要用状态流程表和时间图的分析方法。

6.6.1脉冲异步时序逻辑电路

脉冲异步时序逻辑电路的时钟信号不是统一的,各个触发器的时钟端没有连接在一起,所以分析时必须注意各个触发器的时钟信号的边沿变化情况,来决定该触发器的状态是否发生改变。

1. 4为二进制异步计数器

图6.6.3为TTL电路组成的4位二进制异步计数器电路。电路由4个JK触发器组成,J、K输入端均为悬空,即J= K =1,所以4个JK触发器接成了T触发器的形式,T触发器的工作特点是每来一个时钟脉冲的下降沿(有的可能是上升沿)输出端翻转为相反的状态。计数脉冲加在第一个JK触发器的时钟端,后面三个JK触发器分别与前一个JK触发器的Q端相连。所以JK触发器的状态是否发生翻转取决与其时钟端是否有下降沿出现,如果该时钟端出现下降沿,则该JK触发器翻转为相反的状态。

根据T触发器T=1时的状态转移方程:![]() ,可以写出4个JK触发器的状态转移方程为

,可以写出4个JK触发器的状态转移方程为

(6.6.1)

(6.6.1)

式(6.6.1)中的下降箭头表示相应触发器是在对应输出量下降沿到来时状态才发生变化的,如JK触发器2的次态![]() 的状态变化是发生

的状态变化是发生![]() 的下降沿到来。根据式(6.6.1)可以作出状态转移表,如表6.6.1所示。表中的箭头表示该计数输出端的下一个状态为0,即产生下降沿。

的下降沿到来。根据式(6.6.1)可以作出状态转移表,如表6.6.1所示。表中的箭头表示该计数输出端的下一个状态为0,即产生下降沿。

当4个JK触发器处于初态0000时,加入计数脉冲,则只有触发器1状态发生变化,![]() ,计数器状态转换为0001;加入第二个时钟脉冲时,触发器1状态翻转,

,计数器状态转换为0001;加入第二个时钟脉冲时,触发器1状态翻转,![]() ,

,![]() 的值由上一个时钟作用时的1→0,产生了下降沿,作用到触发器2的时钟端,使触发器2的状态也能够翻转为相反的状态,

的值由上一个时钟作用时的1→0,产生了下降沿,作用到触发器2的时钟端,使触发器2的状态也能够翻转为相反的状态,![]() ,此时计数器得状态为0010;加入第三个时钟脉冲,触发器1得状态发生变化,

,此时计数器得状态为0010;加入第三个时钟脉冲,触发器1得状态发生变化,![]() ,计数器状态转换为0011;加入第四个时钟脉冲,触发器1状态翻转,

,计数器状态转换为0011;加入第四个时钟脉冲,触发器1状态翻转,![]() ,

,![]() 的下降沿又使触发器2的状态发生变化,

的下降沿又使触发器2的状态发生变化,![]() ,

,![]() 的下降沿又使触发器3的状态发生变化,

的下降沿又使触发器3的状态发生变化,![]() ,此时计数器的状态为0100,如此可以作出一系列计数脉冲作用下,计数器的输出状态转换情况。

,此时计数器的状态为0100,如此可以作出一系列计数脉冲作用下,计数器的输出状态转换情况。

|

表6.6.1 4位二进制异步计数器状态转移表 |

||||||||

|

时 钟 CP |

初 态 |

次 态 |

||||||

|

Q4 |

Q3 |

Q2 |

Q1 |

Q4 |

Q3 |

Q2 |

Q1 |

|

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 |

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 |

0 0 0 0 1 1 1 1(↓) 0 0 0 0 1 1 1 1(↓) |

0 0 1 1(↓) 0 0 1 1(↓) 0 0 1 1(↓) 0 0 1 1(↓) |

0 1 (↓) 0 1 (↓) 0 1(↓) 0 1(↓) 0 1(↓) 0 1(↓) 0 1(↓) 0 1(↓) |

0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 |

0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 |

0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 |

1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 |

从表中的分析可以看出,某一位的触发器状态是否发生变化,取决于比它更低位的触发器输出结果是否有下降沿产生,这样就会造成计数状态变化的时延,计算速度比同步计数器慢,但是其电路比较简单。

状态转换图与同步计数器相同,在此不在赘述。

2. 集成异步计数器

图6.6.4为二-五-十进制异步计数器74L2S90内部电路结构。电路由四个JK触发器组成,有两个时钟输入端,时钟端不同的组合可以达到多种计数进制的要求。S9(1)、S9(2)和R0(1)、R0(2)为计数器置9端和复位端。

74LS290的计数功能如表6.6.2所示。

|

表6.6.2 74LS90功能表 |

|||||||||

|

R0(1) |

R0(2) |

S0(1) |

S0(2) |

CP1 |

CP2 |

Q4 |

Q3 |

Q2 |

Q1 |

|

1 1 × |

1 1 × |

0 × 1 |

× 0 1 |

× × × |

× × × |

0 0 1 |

0 0 0 |

0 0 0 |

0 0 1 |

|

R0(1)·R0(2)=S0(1)·S0(2)=0 |

CP 0 CP Q4 |

0 CP Q1 CP |

二进制计数 五进制计数 8421BCD码十进制计数 5421BCD码十进制计数 |

||||||

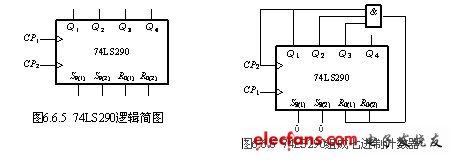

从表中可以看出74LS290具有多种计数模式。当计数输入端加在CP1,CP2不加入计数脉冲,Q1作为计数结果的输出端,则74LS290工作在二进制计数方式,输出是对输入信号的二分频。当计数脉冲加到CP2,CP1不加入计数脉冲,Q2、Q3、Q4作为计数结果的输出端,则74LS290工作在五进制计数方式。当计数脉冲加到CP1,CP2接输出端Q1,Q1、Q2、Q3、Q4作为计数结果的输出端,则74LS290工作在十进制计数方式,以8421BCD码方式输出。当计数脉冲加到CP2,CP1接输出端Q4,Q1、Q2、Q3、Q4作为计数结果的输出端,则74LS290也是工作在十进制计数方式,但是输出端以5421BCD码方式输出。74LS290的逻辑简图如图6.6.5所示。

利用74LS290的置位和复位端同样可以构成十以下的任何一种进制数的运算。图6.6.6为用74LS290组成七进制计数器的电路。其工作原理可以结合前面讲到的复位法获得任意进制数的计数,请读者自己分析其状态转换图。

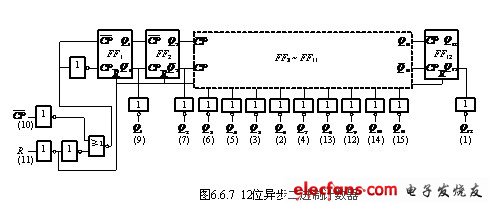

图6.6.7为12位异步二进制计数器CC4040内部逻辑电路,电路由12个触发器组成,每个触发器的输入取决于前级的输出,对应12个输出端。![]() 为计数脉冲的输入端,下降沿计数。R为异步复位端,高电平有效。Q1~Q12为计数结果输出端。CD4040的最大计数可达十进制数的212。

为计数脉冲的输入端,下降沿计数。R为异步复位端,高电平有效。Q1~Q12为计数结果输出端。CD4040的最大计数可达十进制数的212。

利用CD4040可以构成分频系数较大的分频电路。如果输入到![]() 端的信号的频率为4096Hz,则输出端Q12的信号频率1 Hz(212 分频)。

端的信号的频率为4096Hz,则输出端Q12的信号频率1 Hz(212 分频)。

集成中规模异步计数器还有:4位二进制异步计数器74LS197、74 LS 293、74 LS 393,7位二进制异步计数器CC4024,14位异步计数器CD4020、CD4060,十进制异步计数器74LS196、74LS90,双二-五-十进制异步计数器74LS390,异步双十进制异步计数器74LS490等。

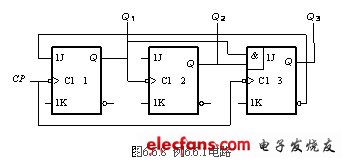

例6.6.1 分析图6.6.8异步计数器电路

解:结合电路可以写出各个JK触发器的时钟信号

(6.6.2)

(6.6.2)

均为下降沿计数。

根据电路写出3个JK触发器的驱动方程为

(6.6.3)

(6.6.3)

根据JK触发器的特性方程,可以得到3个JK触发器的状态方程为

(6.6.4)

(6.6.4)

有了状态转移方程可以假设电路的初始状态为000,然后加入时钟脉冲,得到各个触发器的新状态。第一个时钟脉冲的下降沿到来时,该下降沿作用在触发器1和触发器3上,这两个触发器的状态都可能发生翻转,此时3个触发器的初态为![]() ,将初态值及时钟的下降沿代入式(6.6.4),Q1的状态会发生变化,得到

,将初态值及时钟的下降沿代入式(6.6.4),Q1的状态会发生变化,得到![]() ,此时Q1的上升沿作用到了触发器2上,由于触发器2也是下降沿触发,所以此时的Q2状态不会发生变化,得到

,此时Q1的上升沿作用到了触发器2上,由于触发器2也是下降沿触发,所以此时的Q2状态不会发生变化,得到![]() ,对于触发器3,由于

,对于触发器3,由于![]() ,得到

,得到![]() ,于是第一个时钟脉冲之后,得到计数器的新状态为001。当第二个时钟脉冲的下降沿到来时,同样的分析方法,结合式(6.6.4)以及前一个状态作为现在时钟作用时的初态,得到新的状态为010,分析所得到的状态转移关系如表6.6.3所示。

,于是第一个时钟脉冲之后,得到计数器的新状态为001。当第二个时钟脉冲的下降沿到来时,同样的分析方法,结合式(6.6.4)以及前一个状态作为现在时钟作用时的初态,得到新的状态为010,分析所得到的状态转移关系如表6.6.3所示。

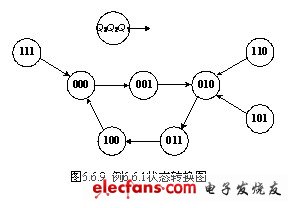

表6.6.3中表示出了初始状态000,输入5个时钟脉冲后回到初始状态的循环。由此可见该计数器完成的功能是五进制计数。将五进制计数循环之外的状态带入式

6.6.4,可以得到次态的结果,如表6.6.3所示。作出状态转换图如图6.6.9所示。

|

表6.6.3 例6.6.1状态转移表 |

|||||||

|

|

时 钟 CP |

初 态 |

次 态 |

||||

|

Q3 |

Q2 |

Q1 |

Q3 |

Q2 |

Q1 |

||

|

有效状态 |

1 2 3 4 5 |

0 0 0 0 1 |

0 0 1 1 0 |

0 1 (↓) 0 1 (↓) 0 |

0 0 0 1 0 |

0 1 1 0 0 |

1 0 1 0 0 |

|

偏离状态 |

↓ ↓ ↓ |

1 1 1 |

0 1 1 |

1 (↓) 0 1 (↓) |

0 0 0 |

1 1 0 |

0 0 0 |

从状态转换图可以看出该异步计数器能够自启动。从脉冲异步时序逻辑电路的分析来看,方法基本上和同步时序逻辑电路的分析相同。在分析中,触发器下一个逻辑状态的得出,必须考虑该触发器的时钟端是否有触发信号的下降沿。

6.6.2电平异步时序逻辑电路分析

电平异步时序逻辑电路的特点是:电路的状态改变是由输入信号电位的变化直接引起的,而脉冲异步时序电路状态的改变是由于输入脉冲信号的边沿(上升沿或者下降沿);电路的二次状态和激励状态仅仅相差一个时间延迟,即二次状态是激励状态延时后的再现;输入信号的一次变化可能引起二次状态多次变化;电路中存在稳态和非稳态。

电平异步时序逻辑电路的分析方法为:写出激励函数表达式、作出流程表、作出总态图、总结逻辑功能。

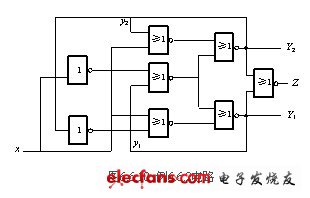

例6.6.2:分析图6.6.10所示电平异步时序逻辑电路。

解:电路中有一个输入端x,三个输出端Y1、Y2和Z,同时将Y1和Y2反馈到电路的或-非门中。

(1)写出激励函数表达式与输出状态表达式

![]()

![]() (6.6.6)

(6.6.6)

(2)作流程表

流程表反映的是电路中输出端和输入端之间的关系,表格中包括输出信号Y1和Y2、激励状态、输入信号x、二次状态y2y1等之间的关系。例6.6.2的流程表如表6.6.4所示。在流程表中,按照编码相邻的原则依次列出输入端的所用可能组合情况,本例中输入只有一个量x,所以其组合的情况只有两种。表格左列列出所有二次状态,也是采用相邻编码的方式列出其组合情况,这里二次状态有y2y1,其组合的可能性是4种。根据输入量和二次状态的取值,结合激励函数表达式(6.6.5)式,将运算得到的激励状态填入表中。例如,当![]() 时,假设此时二次状态为

时,假设此时二次状态为![]() ,代入式(6.6.5)中,可以得到激励状态为01。如果

,代入式(6.6.5)中,可以得到激励状态为01。如果![]() 时,假设此时二次状态为

时,假设此时二次状态为![]() ,代入式(6.6.5)中,可以得到激励状态为00。按照这样的方法依次将输入量x的取值和二次状态的取值带入式(6.6.5)得到表6.6.4所有激励状态。

,代入式(6.6.5)中,可以得到激励状态为00。按照这样的方法依次将输入量x的取值和二次状态的取值带入式(6.6.5)得到表6.6.4所有激励状态。

|

表6.6.4 例6.6.2流程表 |

|||

|

二次状态 |

激励状态Y2Y1 |

||

|

y2 |

y1 |

|

|

|

0 0 1 1 |

0 1 1 0 |

01/1

10/0

|

11/0

00/0 |

在表6.6.4中,如果二次状态为00,输入![]() 时,得到的激励状态为01,与二次状态不同,所以00这样的二次状态在输入

时,得到的激励状态为01,与二次状态不同,所以00这样的二次状态在输入![]() 时,为非稳态;如果二次状态为00,输入

时,为非稳态;如果二次状态为00,输入![]() 时,得到的激励状态为00,与二次状态相同,所以00这样的二次状态在输入

时,得到的激励状态为00,与二次状态相同,所以00这样的二次状态在输入![]() 时,为稳态。表中将稳态用圆圈圈出,非稳态没有圈出。

时,为稳态。表中将稳态用圆圈圈出,非稳态没有圈出。

从表6.6.4中看出电路有4个稳定状态,分别为00、01、11和10。状态之间的转化是在输入量x的作用下完成的。

(3)作出时间图

为了较容易作出时间图,先作出总态响应序列,然后在根据总态响应序列作出时间图。总态是指电路输入和二次状态的组合。流程表中行列对应的状态就是总态。总态图是反映电路稳定状态之间转换关系及相应输出的一种有图形。下面通过作总态图的方法来表现状态之间的转化。设输入量x的值作如下变化循环:1→0→1→0→1,设在![]() 时,初始状态为Y2 = Y1 = 0,即初始总态为(1,00)。根据流程表可以列出总态响应序列为

时,初始状态为Y2 = Y1 = 0,即初始总态为(1,00)。根据流程表可以列出总态响应序列为

|

时刻( t ): |

t0 |

t1 |

t2 |

t3 |

t4 |

|

|

输入( x ): |

1 |

0 |

1 |

0 |

1 |

|

|

总态(x,y2y1): |

(1, 00) |

(0, 00) (0, 01) |

(1, 01) (1, 11) |

(0, 11) (0, 10) |

(1, 10) (1, 00) |

|

|

输出Z: |

1 |

0 |

0 |

0 |

1 |

|

从总态响应序列看出,如果某一时刻下面只有一个总态,那么这个这个总态是稳定的,如t0时刻的总态(1, 00);如果某时刻下面有两个或多个总态,则最下面的那个总态才是稳定的,其它总态均为不稳定总态,如t1时刻的总态(0, 00)为不稳定总态,下面的总态(0, 01)为稳定总态。

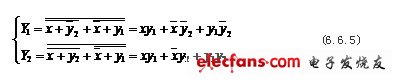

根据总态响应序列,作出时间图如图6.6.11所示。图中t0时刻总态为(1, 00),即x = 1,y2 =0,y1 =0,此状态保留到t1时刻,由此可以作出t0~t1时间段的波形。在t1时刻的总态为(0, 00),即x=0,y2 =0,y1 =0,此状态是不稳定的,其持续时间为Dt,由此可以作出t1~t’1时间段的波形。在t’1时刻,总态为(0, 01),即x = 0,y2 =0,y1 =1,此状态是稳定的,该总态一直保留到输入x的值发生变化的t2时刻。按此方法,可以作出输入x的序列作用下,电路完整的时间图。

根据总态响应序列,还可以作出总态转换图如图6.6.12所示。从总态转换图中可以看出该电路是一个输入数值变化的监测器,如果输入信号x变化了4次,则完成4个状态的循环。