重点

● TSMC认证基于新思科技3DIC Compiler统一平台的CoWoS®和InFO设计流程

● 3DIC Compiler可提高先进封装设计生产率

● 集成Ansys芯片封装协同分析解决方案,可实现可靠的签核和设计实时分析

新思科技(Synopsys)近日宣布与TSMC合作,为先进封装解决方案提供经认证的设计流程。这些解决方案使用新思科技3DIC Compiler产品,进行CoWoS®-S (基于硅中介层的CoWoS)和InFO-R(基于高密度晶圆级RDL InFO)设计。3DIC Compiler为当今高性能计算、汽车电子和移动产品等应用场景所需的复杂多裸片系统提供了封装设计解决方案。

“人工智能和5G网络等应用对高集成度、低功耗、小尺寸和快速产出的要求不断提升,推动了对先进封装技术的需求。TSMC创新的3DIC技术,例如CoWoS®和InFO,以极具竞争力的成本为客户提供更强的功能和更高的系统性能,协助客户实现创新。我们与新思科技合作,为使用TSMC CoWoS®和InFO封装技术的客户提供经认证的解决方案,协助其高效快速完成功能化产品。”

—— Suk Lee

设计基础设施管理部门资深部长

TSMC

新思科技3DIC Compiler解决方案提供了统一的芯片封装协同设计和分析环境,可在封装中创建最佳的2.5D/3D多裸片系统。该解决方案包括TSMC设计宏单元(MACRO)支持以及基于CoWoS®技术的高密度中介层连接器自动布线等功能。对于基于RDL的InFO设计,通过自动DRC感知、全角度多层信号和电源/接地布线、电源/接地层创建和虚拟金属插入,以及对TSMC设计宏单元的支持,可将计划时间从数月缩短到几周。

对于CoWoS-S和InFO-R设计,需要在封装和整个系统的背景下分析裸片。裸片感知封装和封装感知裸片的电源完整性、信号完整性和热分析对于设计验证和签核至关重要。将Ansys的RedHawk™系列芯片封装协同分析解决方案集成到3DIC Compiler可以满足这一关键需求,从而实现无缝分析,更快地收敛到最佳解决方案。通过优化设计冗余,客户可以实现更小尺寸的设计和更高的性能。

责任编辑:haq

-

芯片

+关注

关注

459文章

51945浏览量

433943 -

解决方案

+关注

关注

0文章

531浏览量

40569 -

人工智能

+关注

关注

1804文章

48468浏览量

245139 -

5G

+关注

关注

1360文章

48681浏览量

569276

发布评论请先 登录

DevOps与功能安全:Perforce ALM通过ISO 26262合规认证,简化安全关键系统开发流程

新思科技与Vector达成战略合作

Lenovo荣获Microsoft六项解决方案合作伙伴认证

NX CAD软件:数字化工作流程解决方案(CAD工作流程)

新思科技再获台积公司多项OIP年度合作伙伴大奖

思科推出Cisco 360合作伙伴计划

新思科技7月份行业事件

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

新思科技引领EMIB封装技术革新,推出量产级多裸晶芯片设计参考流程

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

新思科技推出业界首款PCIe 7.0 IP解决方案

新思科技推出业界首款PCIe 7.0 IP解决方案

经纬恒润助力微宏动力荣获ISO/SAE 21434网络安全流程认证证书

联想与思科建立全球战略合作伙伴关系

是德科技联合新思科技、Ansys推出了一个全新的集成射频设计迁移流程

压敏(MOV)在电机上的应用剖析

一前言有刷直流电机是一种较为常见的直流电机。它的主要特点包括:1.结构相对简单,由定子、转子、电刷和换向器等组成;2.通过电刷与换向器的接触来实现电流的换向,从而使电枢绕组中的电流方向周期性改变,保证电机持续运转;3.具有调速性能较好等优点,可以通过改变电压等方式较为方便地调节转速。有刷直流电机在许多领域都有应用,比如一些电动工具、玩具、小型机械等。但它也存

硬件原理图学习笔记

这一个星期认真学习了硬件原理图的知识,做了一些笔记,方便以后查找。硬件原理图分为三类1.管脚类(gpio)和门电路类输入输出引脚,上拉电阻,三极管与门,或门,非门上拉电阻:正向标志作用,给悬空的引脚一个确定的状态三极管:反向三极管(gpio输出高电平,NP两端导通,被控制端导通,电压为0)->NPN正向三极管(gpio输出低电平,PN两端导通,被控制端导通,

TurMass™ vs LoRa:无线通讯模块的革命性突破

TurMass™凭借其高传输速率、强大并发能力、双向传输、超强抗干扰能力、超远传输距离、全国产技术、灵活组网方案以及便捷开发等八大优势,在无线通讯领域展现出强大的竞争力。

RZT2H CR52双核BOOT流程和例程代码分析

RZT2H是多核处理器,启动时,需要一个“主核”先启动,然后主核根据规则,加载和启动其他内核。本文以T2H内部的CR52双核为例,说明T2H多核启动流程。

干簧继电器在RF信号衰减中的应用与优势

在电子测试领域,RF(射频)评估是不可或缺的一部分。无论是研发阶段的性能测试,还是生产环节的质量检测,RF测试设备都扮演着关键角色。然而,要实现精准的RF评估,测试设备需要一种特殊的电路——衰减电路。这些电路的作用是调整RF信号的强度,以便测试设备能够准确地评估RF组件和RF电路的各个方面。衰减器的挑战衰减器的核心功能是校准RF信号的强度。为了实现这一点,衰

ElfBoard嵌入式教育科普|ADC接口全面解析

当代信息技术体系中,嵌入式系统接口作为数据交互的核心基础设施,构成了设备互联的神经中枢。基于标准化通信协议与接口规范的技术架构,实现了异构设备间的高效数据交换与智能化协同作业。本文选取模数转换接口ADC作为技术解析切入点,通过系统阐释其工作机理、性能特征及重要参数,为嵌入式学习者爱好者构建全维度接口技术认知框架。

深入理解C语言:C语言循环控制

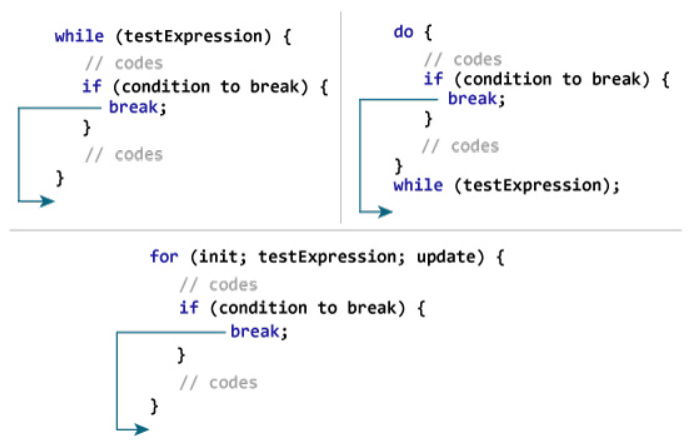

在C语言编程中,循环结构是至关重要的,它可以让程序重复执行特定的代码块,从而提高编程效率。然而,为了避免程序进入无限循环,C语言提供了多种循环控制语句,如break、continue和goto,用于改变程序的执行流程,使代码更加灵活和可控。本文将详细介绍这些语句的作用及其应用场景,并通过示例代码进行说明。Part.1break语句C语言中break语句有两种

第 21 届(顺德)家电电源与智能控制技术研讨会圆满落幕--其利天下斩获颇丰

2025年4月25日,其利天下应大比特之邀出席第21届(顺德)家电电源与智能控制技术研讨会,已圆满落幕。一、演讲回顾我司研发总监冯建武先生在研讨会上发表了主题为《重新定义风扇驱动:一套算法兼容百种电机的有效磁链观测器方案》的演讲,介绍了我司研发自适应技术算法(简称),该方案搭载有效磁链观测器,适配百种电机类型,结合FOC算法可实现免调参稳定启动、低速静音控制

来自资深工程师对ELF 2开发板的产品测评

来自资深工程师对ELF 2开发板的使用测评

飞凌嵌入式2025嵌入式及边缘AI技术论坛圆满结束

飞凌嵌入式「2025嵌入式及边缘AI技术论坛」在深圳深铁皇冠假日酒店盛大举行,此次活动邀请到了200余位嵌入式技术领域的技术专家、企业代表和工程师用户,共享嵌入式及边缘AI技术的盛宴!

常用运放电路总结记录

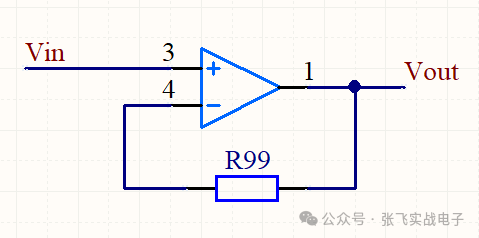

一、电压跟随器电压跟随器,电路图如下:电路分析:(本文所有的运放电路分析,V+表示运放同向输入端的电压,V-表示反向输入端的电压。)1.1电压跟随器反馈电阻需不需要?在上面的电压跟随器示例中,我画上了一个反馈电阻R99,大家在学习的运放的时候,可能很多地方也会提一下这个反馈电阻,很多地方会说可加可不加,效果一样。电阻需不需要加:但是本文这里个人建议使用电压跟

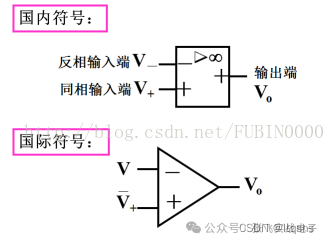

运放-运算放大器经典应用电路大全-应用电路大全-20种经典电路

20种运放典型电路总结,电路图+公式1、运放的符号表示2、集成运算放大器的技术指标(1)开环差模电压放大倍数(开环增益)大Ao(Ad)=Vo/(V±V-)=107-1012倍;(2)共模抑制比高KCMRR=100db以上;(3)输入电阻大ri>1MW,有的可达100MW以上;(4)输出电阻小ro=几W-几十W3、集成运放分析方法(V+=V-虚短,ib-=ib

RDK X3新玩法:超沉浸下棋机器人开发日记

一、项目介绍产品中文名:超沉浸式智能移动下棋机器人产品英文名:Hackathon-TTT产品概念:本项目研发的下棋机器人,是一款能自主移动、具备语音交互并能和玩家在真实的棋盘上进行“人机博弈”的移动下棋平台,能够带给对弈者如同真人对弈的完美沉浸式体验——棋开得胜团队。该智能下棋机器人具备3个显著优点:真实棋盘棋子对弈:通过使用真实棋子、棋盘和机械臂,给对弈者

芯对话 | 微处理器监控电路革新:CBM70X系列 重构系统可靠性

总述在工业自动化、消费电子、汽车电子等领域,微处理器作为系统核心,其稳定运行依赖可靠的电源监控。据统计,65%的系统故障源于电源异常——工业控制设备因电压波动导致的停机频率每月平均达3.2次,便携式设备因电池管理不当造成的续航缩水普遍超过25%,汽车电子ECU因电源扰动引发的误判率在复杂工况下高达18%。传统监控方案的三大核心痛点极端电压适应性不足:当电压低

喜讯!米尔电子与安路科技达成IDH生态战略合作,共筑FPGA创新生态

以芯为基,智创未来。近日,领先的嵌入式模组厂商-米尔电子正式与国产FPGA企业安路科技达成IDH生态战略合作。双方将围绕安路科技飞龙SALDRAGON系列高性能FPSoC,联合开发核心板、开发板及行业解决方案,助力开发者开发成功,加速工业控制、边缘智能、汽车电子等领域的创新应用落地。米尔电子&安路科技IDH生态合作证书硬核技术+生态协同安路科技作为

新思科技与TSMC合作为封装解决方案提供经认证的设计流程

新思科技与TSMC合作为封装解决方案提供经认证的设计流程

评论