在人们的认知中,金属材料通常具有良好的延展性,而陶瓷材料在外力下呈现脆性断裂。造成这种变形能力差异的根本原因是原子之间成键方式的不同。金属中原子之间成金属键,价电子可以在原子核外自由移动,使其在滑移过程中不会引起电荷阻力,因此变形能力较好;而陶瓷材料中具有方向性的共价键和离子键使得材料在变形时存在静电阻力,因此在断裂前只能产生有限的变形(通常小于0.2%)。陶瓷材料的脆性很大程度地限制了其应用,因此,人们一直在寻求改善陶瓷脆性的方法。

将材料尺寸减小到纳米尺度,以减少其内部容易引起断裂的缺陷,进而获得材料固有塑性,是减少陶瓷因缺陷而产生断裂,以研究其固有塑性的一种可行方法。不论是金属还是陶瓷,越小的样品通常塑性变形能力越显著。

钙钛矿型氧化物材料的变形行为对材料科学和地质科学领域都具有重要的意义。在材料科学中,钙钛矿氧化物表现出多种优异性能,比如铁电、多铁、超导、压电、光伏等。而在地质科学中,一种富含 MgSiO3 的钙钛矿相被认为是占据控制地震活动的地球区域的主要物质组成。在具有钙钛矿结构的氧化物中,人们对SrTiO3的力学性能研究较为充分,并认为它是钙钛矿氧化中具有较好塑性变形能力的代表。

近期,悉尼大学与合作单位的研究人员利用原位扫描、透射电子显微学,通过对比研究发现具有钙钛矿结构的弛豫铁电体Pb(In1/2Nb1/2)O3-Pb(Mg1/3Nb2/3)O3-PbTiO3(PIN-PMN-PT)具有比SrTiO3高出一个数量级的变形能力——直径大于150 nm的SrTiO3纳米柱表现为脆性断裂,而直径为2.1 µm的PIN-PMN-PT微柱仍可产生大的塑性变形。引起这种优异塑性变形的根本原因是PIN/PMN/PT中的微界面上包含大量的氧空位,氧空位弱化共价键,进而获得优异的塑性变形能力。

该工作的主要结论如下:

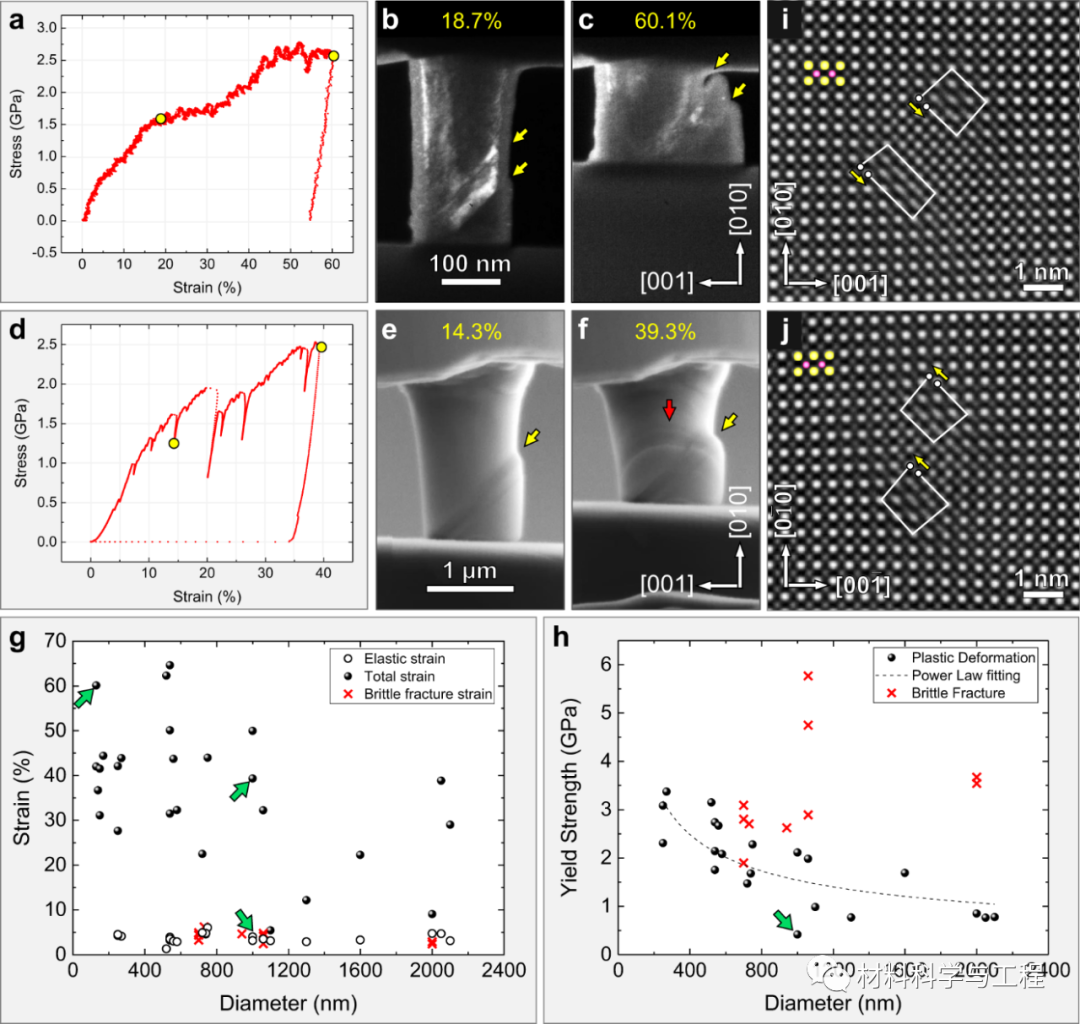

1. 直径为2.1 µm的PIN-PMN-PT圆柱在沿《100》方向进行压缩时,表现出高达40%的塑性变形。其滑移系为 {110} 《1-10 》,变形时产生成对的1/2a《011》型且沿垂直于滑移面方向攀移分解的位错。

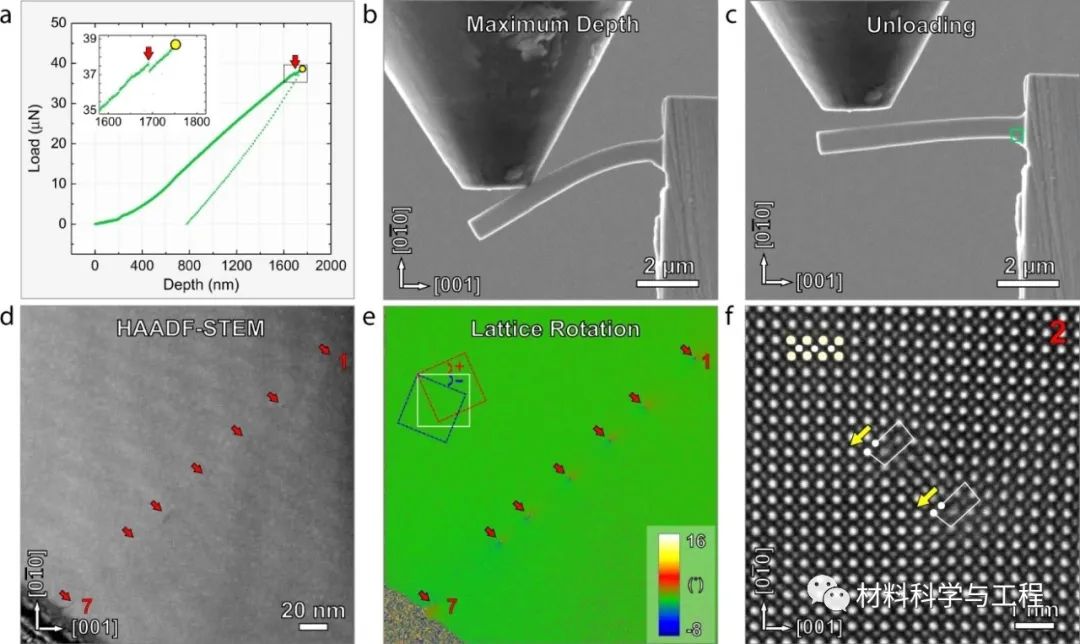

2. 对长度约为6 µm,宽度为0.67 µm,厚度为0.8 µm 的悬臂梁沿《100》方向进行弯曲测试。悬臂梁产生6.8%的弹性应变,1.4%的塑性应变而未发生断裂。伴随塑性变形,在悬臂梁根部产生一排1/2a《011》型位错。

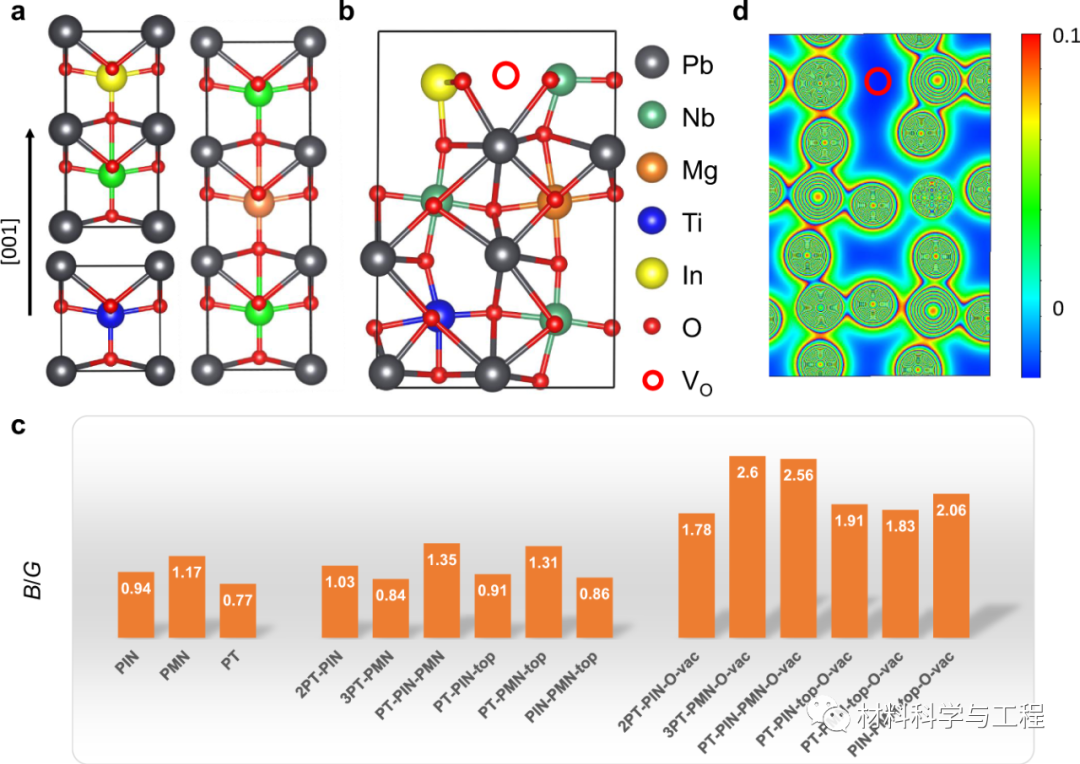

3. 在PIN-PMN-PT中,伴随变形产生攀移分解的位错。这不同于以往报道的室温变形下,钙钛矿氧化物中所产生的滑移分解位错。由于位错攀移离不开点缺陷的扩散,而在钙钛矿氧化物中主要点缺陷是空位而非间隙原子,由此推测在PIN-PMN-PT中存在大量的铅空位或氧空位缺陷(这两种在铅基钙钛矿中较为常见)。针对该推测,第一性原理模拟结果显示:(A)氧空位使得体系能量降低而铅空位相反;(B)氧空位使得块体模量与剪切模量的比值增大,从小于1.75到大于1.75,实现脆性到延展性的转变(B/G ratio大于1.75被认为具有延展性);(C)对电子态密度进行分析发现,氧空位削弱局部共价键,导致变形变容易。

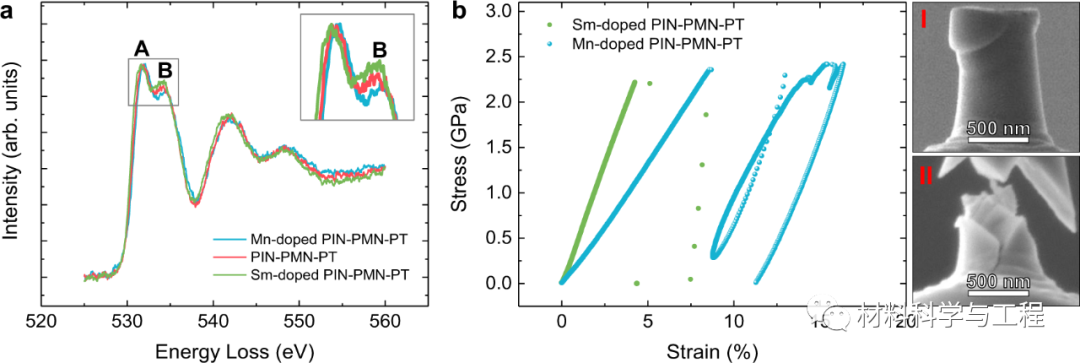

4. 通过对富铅空位的Sm掺杂的PIN-PMN-PT和富氧空位的Mn掺杂的PIN-PMN-PT亚微米圆柱进行力学性能研究,发现富氧空位的PIN-PMN-PT确实塑性变形能力更为优异。利用电子能量损失谱,氧空位含量的差异得到验证。

PIN-PMN-PT具有优异的力电耦合特性(大的挠曲电、压电以及力电耦合系数),在微纳米尺度下,优异的弯曲变形能力以及位错/滑移带周围的巨大应变梯度会引起极大的挠曲电极化。使其在基于挠曲电的微致动器和探测器应用中具有很大的前景,并有可能在微机电系统以及物联网中发挥重要作用。

图1. PIN-PMN-PT纳米柱和微米柱的压缩测试。压缩150 nm(a-c)以及1 µm(d-f)直径的PIN-PMN-PT圆柱得到的工程应力-应变曲线以及压缩过程中得到的透射电镜和扫描电镜图像。(g)压缩多个圆柱得到的应变-圆柱直径关系的统计结果。(h)屈服强度-圆柱直径曲线。(i, j)高分辨像显示变形产生的位错。

图2. PIN-PMN-PT悬臂梁弯曲测试。(a)载荷-位移曲线。(b,c)悬臂梁最大变形时以及卸载后的扫描电镜图。(d)悬臂梁根部的低倍高分辨扫描透射电子显微像。(e)对图(d)进行几何相位分析得出的显示晶格旋转的2D彩图。1-7显示位错。(f)位错2的高分辨像。

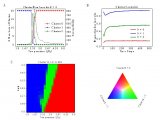

图3.(a)PIN,PMN,PT亚单胞示意图。(b)在PMN/PT界面上存在一个氧空位的PIN-PMN-PT示意图。(c)第一性原理得到的不同组合/排布方式的PIN/PMN/PT块体模量/剪切模量值(B/G ratio)。(d)第一性原理模拟得到的 (b)图结构对应的电荷密度二维分布图。

图4. (a)锰掺杂(蓝),钐掺杂(绿)和无掺杂(红)PIN-PMN-PT中O的电子能量损失谱。B峰强度差异显示三种PIN-PMN-PT中的氧空位含量:锰掺杂》无掺杂》钐掺杂。(b)原位压缩锰掺杂(蓝)和钐掺杂(绿)PIN-PMN-PT得到的工程应力-应变曲线。(I)和(II)分别是锰掺杂和钐掺杂PIN-PMN-PT纳米柱压缩后的扫描电镜像。

-

探测器

+关注

关注

14文章

2691浏览量

74061 -

显微

+关注

关注

0文章

20浏览量

18237 -

钙钛矿

+关注

关注

3文章

93浏览量

8066

原文标题:文章转载丨悉尼大学《Nature Commun》:弛豫铁电体室温下超高变形能力!

文章出处:【微信号:hzwtech,微信公众号:鸿之微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

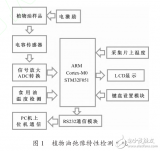

嵌入式杯突试验机测控系统的工作原理是什么?

压痕诱发GaAs单晶的塑性变形

金属的塑性变形与再结晶(验证性)

热处理变形的原因_减小热处理变形的方法

弛豫铁电材料优异性能的结构起源是铁电材料领域的主要挑战之一

Au纳米晶体在剪切加载下通过孪晶界滑移主导的塑性变形机制

晶体知识:塑性变形对材料组织与性能的影响

基于Mn顺磁弛豫和纳米催化的多信号生物传感器开发

弛豫振荡器的原理和应用

弛豫频率与截止频率计算

有几种电平转换电路,适用于不同的场景

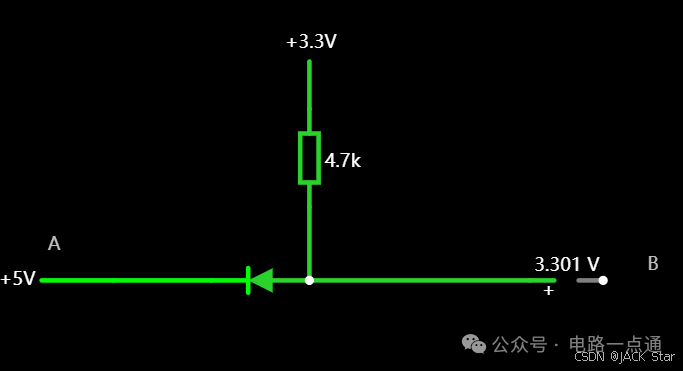

一.起因一般在消费电路的元器件之间,不同的器件IO的电压是不同的,常规的有5V,3.3V,1.8V等。当器件的IO电压一样的时候,比如都是5V,都是3.3V,那么其之间可以直接通讯,比如拉中断,I2Cdata/clk脚双方直接通讯等。当器件的IO电压不一样的时候,就需要进行电平转换,不然无法实现高低电平的变化。二.电平转换电路常见的有几种电平转换电路,适用于

瑞萨RA8系列教程 | 基于 RASC 生成 Keil 工程

对于不习惯用 e2 studio 进行开发的同学,可以借助 RASC 生成 Keil 工程,然后在 Keil 环境下愉快的完成开发任务。

共赴之约 | 第二十七届中国北京国际科技产业博览会圆满落幕

作为第二十七届北京科博会的参展方,芯佰微有幸与800余家全球科技同仁共赴「科技引领创享未来」之约!文章来源:北京贸促5月11日下午,第二十七届中国北京国际科技产业博览会圆满落幕。本届北京科博会主题为“科技引领创享未来”,由北京市人民政府主办,北京市贸促会,北京市科委、中关村管委会,北京市经济和信息化局,北京市知识产权局和北辰集团共同承办。5万平方米的展览云集

道生物联与巍泰技术联合发布 RTK 无线定位系统:TurMass™ 技术与厘米级高精度定位的深度融合

道生物联与巍泰技术联合推出全新一代 RTK 无线定位系统——WTS-100(V3.0 RTK)。该系统以巍泰技术自主研发的 RTK(实时动态载波相位差分)高精度定位技术为核心,深度融合道生物联国产新兴窄带高并发 TurMass™ 无线通信技术,为室外大规模定位场景提供厘米级高精度、广覆盖、高并发、低功耗、低成本的一站式解决方案,助力行业智能化升级。

智能家居中的清凉“智”选,310V无刷吊扇驱动方案--其利天下

炎炎夏日,如何营造出清凉、舒适且节能的室内环境成为了大众关注的焦点。吊扇作为一种经典的家用电器,以其大风量、长寿命、低能耗等优势,依然是众多家庭的首选。而随着智能控制技术与无刷电机技术的不断进步,吊扇正朝着智能化、高效化、低噪化的方向发展。那么接下来小编将结合目前市面上的指标,详细为大家讲解其利天下有限公司推出的无刷吊扇驱动方案。▲其利天下无刷吊扇驱动方案一

电源入口处防反接电路-汽车电子硬件电路设计

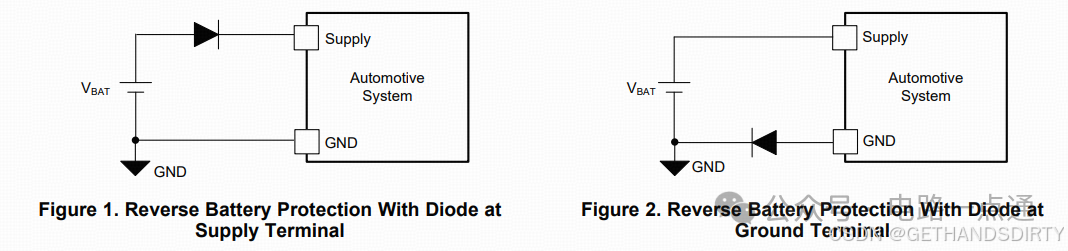

一、为什么要设计防反接电路电源入口处接线及线束制作一般人为操作,有正极和负极接反的可能性,可能会损坏电源和负载电路;汽车电子产品电性能测试标准ISO16750-2的4.7节包含了电压极性反接测试,汽车电子产品须通过该项测试。二、防反接电路设计1.基础版:二极管串联二极管是最简单的防反接电路,因为电源有电源路径(即正极)和返回路径(即负极,GND),那么用二极

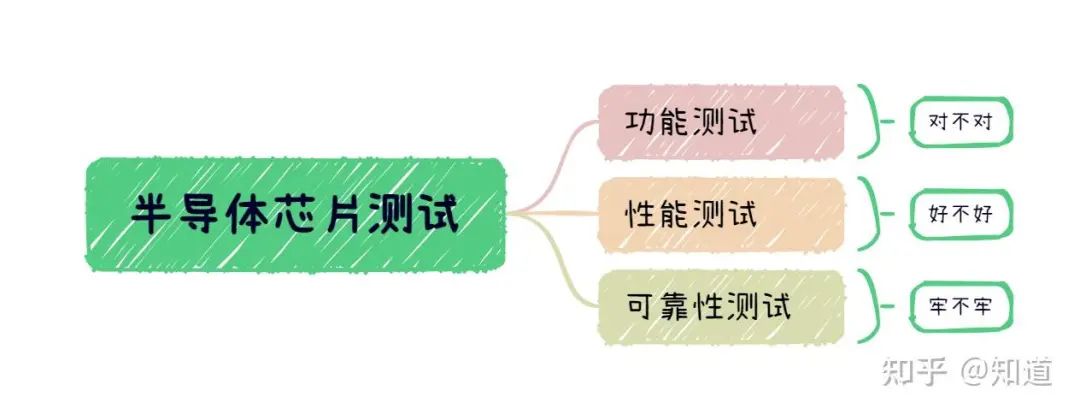

半导体芯片需要做哪些测试

首先我们需要了解芯片制造环节做⼀款芯片最基本的环节是设计->流片->封装->测试,芯片成本构成⼀般为人力成本20%,流片40%,封装35%,测试5%(对于先进工艺,流片成本可能超过60%)。测试其实是芯片各个环节中最“便宜”的一步,在这个每家公司都喊着“CostDown”的激烈市场中,人力成本逐年攀升,晶圆厂和封装厂都在乙方市场中“叱咤风云”,唯独只有测试显

解决方案 | 芯佰微赋能示波器:高速ADC、USB控制器和RS232芯片——高性能示波器的秘密武器!

示波器解决方案总述:示波器是电子技术领域中不可或缺的精密测量仪器,通过直观的波形显示,将电信号随时间的变化转化为可视化图形,使复杂的电子现象变得清晰易懂。无论是在科研探索、工业检测还是通信领域,示波器都发挥着不可替代的作用,帮助工程师和技术人员深入剖析电信号的细节,精准定位问题所在,为创新与发展提供坚实的技术支撑。一、技术瓶颈亟待突破性能指标受限:受模拟前端

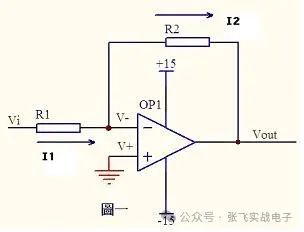

硬件设计基础----运算放大器

1什么是运算放大器运算放大器(运放)用于调节和放大模拟信号,运放是一个内含多级放大电路的集成器件,如图所示:左图为同相位,Vn端接地或稳定的电平,Vp端电平上升,则输出端Vo电平上升,Vp端电平下降,则输出端Vo电平下降;右图为反相位,Vp端接地或稳定的电平,Vn端电平上升,则输出端Vo电平下降,Vn端电平下降,则输出端Vo电平上升2运算放大器的性质理想运算

ElfBoard技术贴|如何调整eMMC存储分区

ELF 2开发板基于瑞芯微RK3588高性能处理器设计,拥有四核ARM Cortex-A76与四核ARM Cortex-A55的CPU架构,主频高达2.4GHz,内置6TOPS算力的NPU,这一设计让它能够轻松驾驭多种深度学习框架,高效处理各类复杂的AI任务。

米尔基于MYD-YG2LX系统启动时间优化应用笔记

1.概述MYD-YG2LX采用瑞萨RZ/G2L作为核心处理器,该处理器搭载双核Cortex-A55@1.2GHz+Cortex-M33@200MHz处理器,其内部集成高性能3D加速引擎Mail-G31GPU(500MHz)和视频处理单元(支持H.264硬件编解码),16位的DDR4-1600/DDR3L-1333内存控制器、千兆以太网控制器、USB、CAN、

运放技术——基本电路分析

虚短和虚断的概念由于运放的电压放大倍数很大,一般通用型运算放大器的开环电压放大倍数都在80dB以上。而运放的输出电压是有限的,一般在10V~14V。因此运放的差模输入电压不足1mV,两输入端近似等电位,相当于“短路”。开环电压放大倍数越大,两输入端的电位越接近相等。“虚短”是指在分析运算放大器处于线性状态时,可把两输入端视为等电位,这一特性称为虚假短路,简称

飞凌嵌入式携手中移物联,谱写全国产化方案新生态

4月22日,飞凌嵌入式“2025嵌入式及边缘AI技术论坛”在深圳成功举办。中移物联网有限公司(以下简称“中移物联”)携OneOS操作系统与飞凌嵌入式共同推出的工业级核心板亮相会议展区,操作系统产品部高级专家严镭受邀作《OneOS工业操作系统——助力国产化智能制造》主题演讲。

ATA-2022B高压放大器在螺栓松动检测中的应用

实验名称:ATA-2022B高压放大器在螺栓松动检测中的应用实验方向:超声检测实验设备:ATA-2022B高压放大器、函数信号发生器,压电陶瓷片,数据采集卡,示波器,PC等实验内容:本研究基于振动声调制的螺栓松动检测方法,其中低频泵浦波采用单频信号,而高频探测波采用扫频信号,利用泵浦波和探测波在接触面的振动声调制响应对螺栓的松动程度进行检测。通过螺栓松动检测

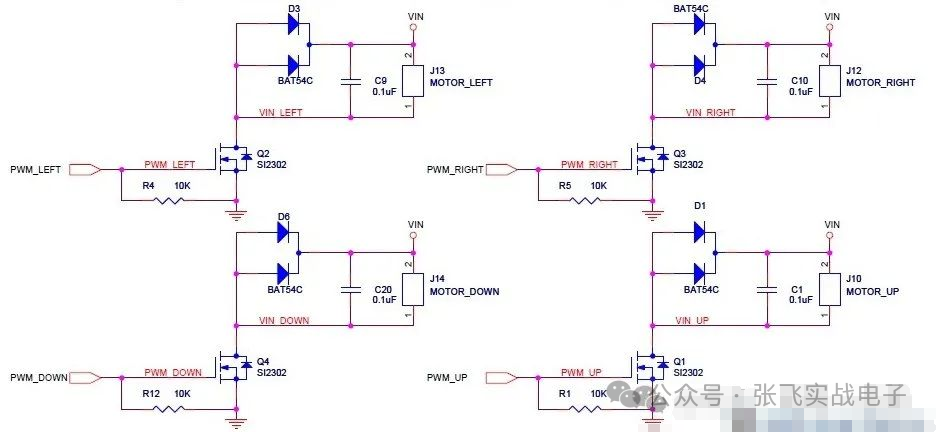

MOS管驱动电路——电机干扰与防护处理

此电路分主电路(完成功能)和保护功能电路。MOS管驱动相关知识:1、跟双极性晶体管相比,一般认为使MOS管导通不需要电流,只要GS电压(Vbe类似)高于一定的值,就可以了。MOS管和晶体管向比较c,b,e—–>d(漏),g(栅),s(源)。2、NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以

弛豫铁电体室温下获得优异的塑性变形能力

弛豫铁电体室温下获得优异的塑性变形能力

评论