近年来,多媒体技术逐渐深入到人们的生活中。MP3播放器已经成为流行的便携式音频播放设备,由于MP3编码算法非常复杂,目前,一部分MP3播放器的录音功能主要基于ADPCM算法和DSP来实现。本文阐述了ADPCM语音编解码VLSI芯片的设计方法以及利用FPGA的硬件实现。

ADPCM算法及其编解码器原理

ADPCM(Adaptive Differential Pulse Code Modulation,自适应差分脉冲编码调制)综合了APCM的自适应特性和DPCM系统的差分特性,是一种性能较好的波形编码。它的核心思想是:利用自适应改变量化阶的大小,即使用小的量化阶去编码小的差值,使用大的量化阶去编码大的差值;使用过去的样本值估算下一个输入样本的预测值,使实际样本值和预测值之间的差值总是最小。ADPCM记录的量化值不是每个采样点的幅值,而是该点的幅值与前一个采样点幅值之差。

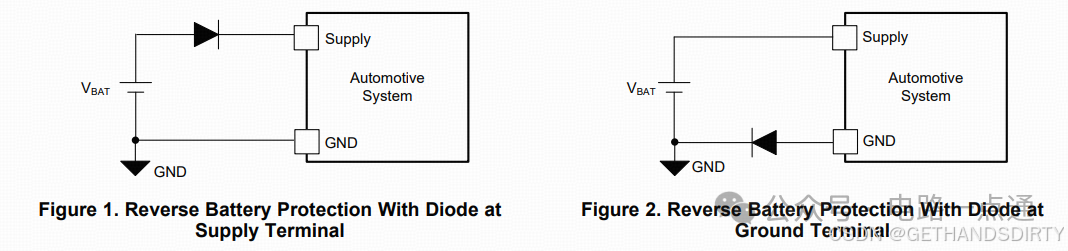

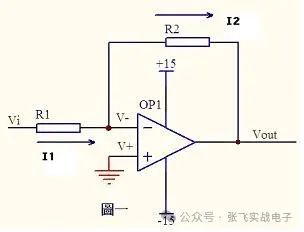

ADPCM是利用样本与样本之间的高度相关性和量化阶自适应来压缩数据的一种波形编码技术。ADPCM标准是一个代码转换系统,它使用ADPCM转换技术实现64kb/s A律或u律PCM(脉冲编码调制)速率和32kb/s速率之间的相互转换。ADPCM的简化框图如图1所示。

ADPCM编解码器的输入信号是G.711 PCM代码,采样率是8kHz,每个代码用8位表示,因此它的数据率为64kb/s。而ADPCM的输出代码是“自适应量化器”的输出,该输出是用4位表示的差分信号,它的采样率仍然是8kHz,它的数据率为32kb/s,这样就获得了2∶1的数据压缩。

电路的整体结构

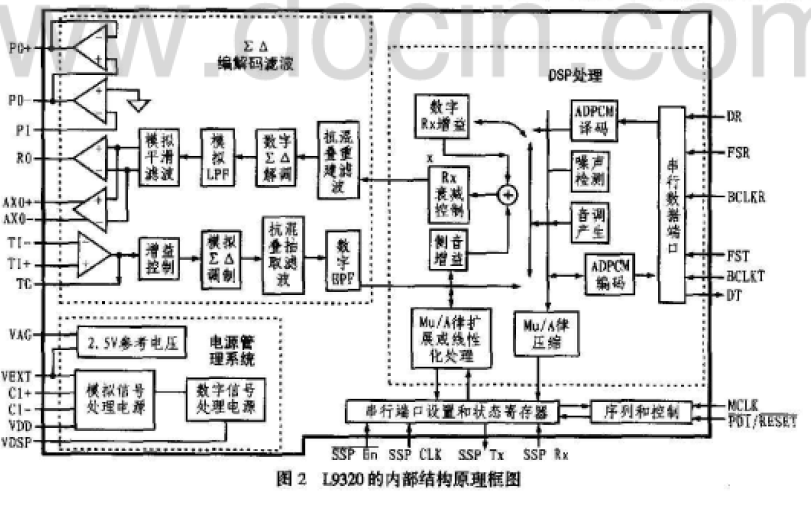

基于ADPCM算法,可将语音编解码VLSI芯片分成编码、解码、存储、控制和时钟几个模块。编码模块实现数据压缩功能,将输入的PCM信号转换成ADPCM码;存储模块在控制模块的作用下,保存编码所得的ADPCM码;解码模块实现解压缩功能,将ADPCM码转换得到PCM码;控制模块的作用是控制其他模块的协调工作;时钟模块主要实现对外部晶振的原始时钟信号进行分频,以得到电路系统实际所需的时钟信号。

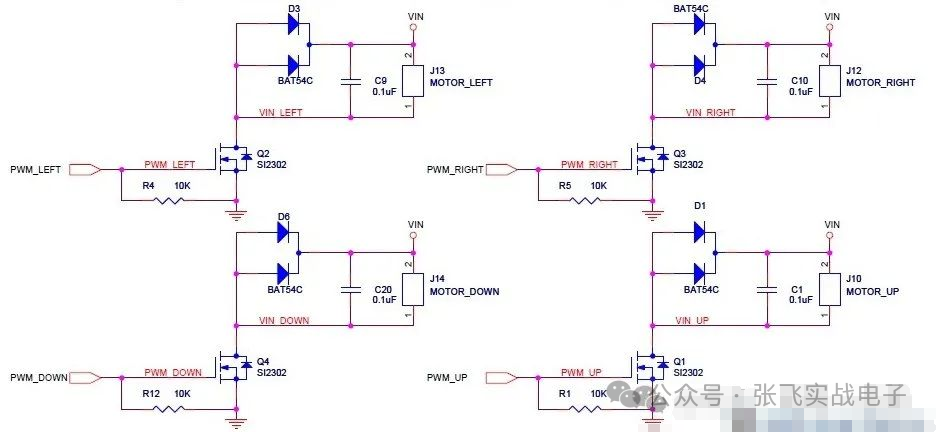

电路整体结构如图2所示,其中En_en、En_de分别是编码和解码的使能信号,RST则为复位信号。当WE为“1”时,RAM写有效,而当 WE为“0”时,RAM读有效,CS为“1”时,RAM可进行写或者读操作。

(a) ADPCM编码器

(b)ADPCM解码器

图1 ADPCM简化框图

电路设计过程

本文采用Top-down方法进行电路设计。主要设计流程如下:首先基于Verilog HDL运用Active-HDL进行电路的RTL级描述和功能仿真;将经过功能仿真正确的程序在Quartus II开发系统中进行综合和适配;接下来将得到的网表文件(.vo)和具有时延信息的反标文件(.sdo)调入ModelSim SE中,并加入所选器件相应的器件库进行时序仿真;时序仿真通过后,将Quartus II得到的“*.sof”文件通过JTAG配置模式下载到FPGA中进行不可掉电的实际测试,也可将“*.pof”文件通过AS配置模式下载到FPGA中进行可掉电的实际测试。电路系统的顶层程序如下。

图2 电路整体结构图

module ADPCM_TOP ( PCM_OUT,PCM_IN ,RECORD,PLAY,CLK, CLK8K);

parameter ADDR_WIDTH=14;

parameter PCM_WIDTH=8;

input [PCM_WIDTH-1:0] PCM_IN ;

wire [PCM_WIDTH-1:0] PCM_IN ;

output [PCM_WIDTH-1:0] PCM_OUT ;

wire [PCM_WIDTH-1:0] PCM_OUT ;

input CLK, RECORD,PLAY;

output CLK8K;

wire [3:0] code_in,code_out;

wire en_encoder,en_decoder,re_rst,pl_rst,WE,CS,CLK_8K;

wire [ADDR_WIDTH-1:0] ADDRESS;

assign CLK8K =CLK_8K;

CLOCK_GE U0 (CLK,RECORD, CLK_8K);

encoder_new U1 ( PCM_IN,re_rst ,en_encoder, CLK_8K ,code_in );

RAM U2 (ADDRESS,WE,CS,CLK_8K,code_in,code_out);

decoder_new U3 (pl_rst, CLK_8K ,code_out ,en_decoder,PCM_OUT);

controllogic U4 (CS,re_rst,pl_rst,en_encoder,en_decoder,WE,ADDRESS,RECORD,PLAY,CLK_8K);

endmodule

子模块电路设计及仿真

整个语音编解码VLSI芯片包括编码电路、解码电路、存储电路、控制电路和时钟电路几个部分。下面分别具体描述关键电路的设计。

1 编码电路

编码电路实现数据压缩功能,将输入的PCM信号转换成均匀的PCM码,然后与预测信号进行差分,得到的差分信号经过“自适应量化器”进行压缩编码得到ADPCM码,ADPCM码被返回经过“逆自适应量化器”以及“自适应预测器”用来构建下一个预测信号。编码电路仿真波形如图3所示,其中PCM_IN为编码器输入信号(PCM码),CODE为编码后得到的输出信号(ADPCM码)。

图3 编码电路仿真波形

2 解码电路

解码电路实现解压缩功能,将ADPCM码经过“逆自适应量化器”得到量化差分信号,量化差分信号与预测值相加得到重构信号,然后转换成PCM码。解码电路仿真波形如图4所示,其中CODE为解码器输入信号(ADPCM码),PCM_OUT为解码后得到的输出信号(PCM码)。与图3中编解码前的PCM_IN对比,可以看出解码误差很小。

3 其他模块

控制电路控制其他电路模块的协调工作,在编码的同时使能存储器写入信号,使编码电路输出数据可以及时存入存储器;在解码的同时使能存储器读出信号,编码和解码不能同时进行。时钟电路主要实现对外部晶振的原始时钟信号进行分频,以得到电路系统实际所需的时钟信号。本系统采用的外部晶振固有频率为14.318MHz,经过分频后可以获得8kHz时钟。存储电路在控制电路的作用下,保存编码所得的ADPCM码(32kb/s),由于只需验证电路的功能,所以只设定了2s的录音存储空间,即64kb存储容量。

整体电路仿真

在子模块电路仿真正确后,对系统整体进行仿真,可以得到图5所示波形。此次仿真输入信号PCM_IN激励采用Testbench产生。在编码使能信号RECORD为“0”时,开始编码,RECORD跳变到“1”时,编码被屏蔽;此时解码使能信号PLAY为“0”,开始解码,PLAY跳变到“1”时,解码被屏蔽。从图中可以看出编码前输入信号PCM_IN的激励和解码后输出PCM_OUT的响应基本符合。由于ADPCM算法本身是有损压缩,可以确定本电路系统的设计是正确可靠的。

FPGA验证及结论

本文基于FPGA验证所设计的电路。这里选用Altera公司Cyclone系列的EP1C6Q240C8器件,其内部有90kb的存储容量,6k个逻辑单元,2 个PLL。由于电路采用8kHz采样频率,编码后的ADPCM码为4位,设定录音时间为2s,所以需要64kb存储容量;同时,设计需要大约400个左右的逻辑单元。所以选用此低成本的FPGA即可满足设计要求,而且基本上充分利用了内部资源。此芯片的引脚有240 个,能满足外面的引脚连接,而且价格也易于接受。

FPGA验证表明:电路的最大时钟延迟为26.903ns,最高工作频率可达37.17MHz,可以很好地再现被录入的语音,具有较高的保真度和很好的实时性。在电子地图、车载信息终端语音播报、治安报警系统,特别是便携式语音记录装置等方面具有较高的应用价值。同时,也指明了数字语音压缩处理高效设计方法的方向。

图4 编码电路仿真波形

图5 系统仿真波形

-

FPGA

+关注

关注

1643文章

21927浏览量

612730 -

解码器

+关注

关注

9文章

1162浏览量

41606 -

存储

+关注

关注

13文章

4479浏览量

86968

发布评论请先 登录

语音和音频统一编解码算法研究

振南对ADPCM音频编解码原理的一些通俗阐述【附振南的ADPCM解码原代码】

如何采用FPGA实现汽车智能语音报警系统设计?

基于DSP Builder的ADPCM算法实现

G.726语音编解码器在SoPC中的实现

G.726语音编解码器在SoPC中的实现

基于ADPCM算法的语音报警系统

基于AMR语音编解码算法的VoIP系统

ADPCM语音编解码VLSI芯片的设计方法

基于ADPCM的语音压缩算法研究

多制式语音编解码算法的DSP设计

智能家居中的清凉“智”选,310V无刷吊扇驱动方案--其利天下

炎炎夏日,如何营造出清凉、舒适且节能的室内环境成为了大众关注的焦点。吊扇作为一种经典的家用电器,以其大风量、长寿命、低能耗等优势,依然是众多家庭的首选。而随着智能控制技术与无刷电机技术的不断进步,吊扇正朝着智能化、高效化、低噪化的方向发展。那么接下来小编将结合目前市面上的指标,详细为大家讲解其利天下有限公司推出的无刷吊扇驱动方案。▲其利天下无刷吊扇驱动方案一

电源入口处防反接电路-汽车电子硬件电路设计

一、为什么要设计防反接电路电源入口处接线及线束制作一般人为操作,有正极和负极接反的可能性,可能会损坏电源和负载电路;汽车电子产品电性能测试标准ISO16750-2的4.7节包含了电压极性反接测试,汽车电子产品须通过该项测试。二、防反接电路设计1.基础版:二极管串联二极管是最简单的防反接电路,因为电源有电源路径(即正极)和返回路径(即负极,GND),那么用二极

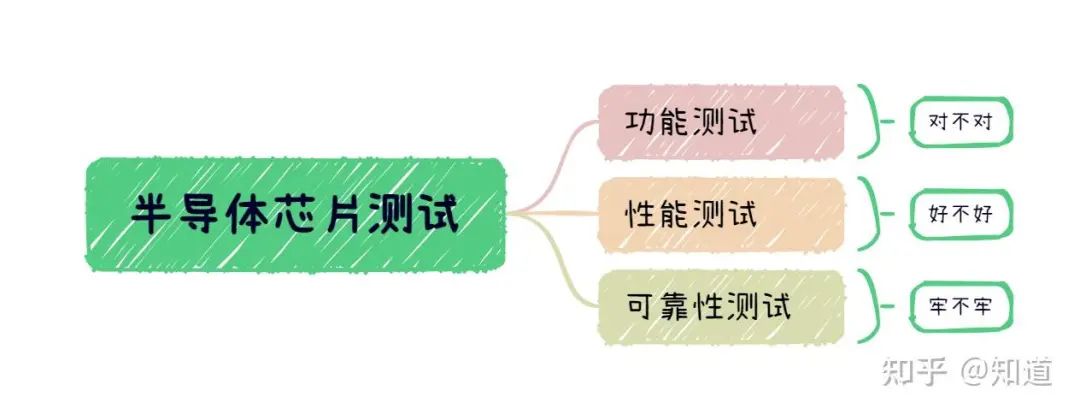

半导体芯片需要做哪些测试

首先我们需要了解芯片制造环节做⼀款芯片最基本的环节是设计->流片->封装->测试,芯片成本构成⼀般为人力成本20%,流片40%,封装35%,测试5%(对于先进工艺,流片成本可能超过60%)。测试其实是芯片各个环节中最“便宜”的一步,在这个每家公司都喊着“CostDown”的激烈市场中,人力成本逐年攀升,晶圆厂和封装厂都在乙方市场中“叱咤风云”,唯独只有测试显

解决方案 | 芯佰微赋能示波器:高速ADC、USB控制器和RS232芯片——高性能示波器的秘密武器!

示波器解决方案总述:示波器是电子技术领域中不可或缺的精密测量仪器,通过直观的波形显示,将电信号随时间的变化转化为可视化图形,使复杂的电子现象变得清晰易懂。无论是在科研探索、工业检测还是通信领域,示波器都发挥着不可替代的作用,帮助工程师和技术人员深入剖析电信号的细节,精准定位问题所在,为创新与发展提供坚实的技术支撑。一、技术瓶颈亟待突破性能指标受限:受模拟前端

硬件设计基础----运算放大器

1什么是运算放大器运算放大器(运放)用于调节和放大模拟信号,运放是一个内含多级放大电路的集成器件,如图所示:左图为同相位,Vn端接地或稳定的电平,Vp端电平上升,则输出端Vo电平上升,Vp端电平下降,则输出端Vo电平下降;右图为反相位,Vp端接地或稳定的电平,Vn端电平上升,则输出端Vo电平下降,Vn端电平下降,则输出端Vo电平上升2运算放大器的性质理想运算

ElfBoard技术贴|如何调整eMMC存储分区

ELF 2开发板基于瑞芯微RK3588高性能处理器设计,拥有四核ARM Cortex-A76与四核ARM Cortex-A55的CPU架构,主频高达2.4GHz,内置6TOPS算力的NPU,这一设计让它能够轻松驾驭多种深度学习框架,高效处理各类复杂的AI任务。

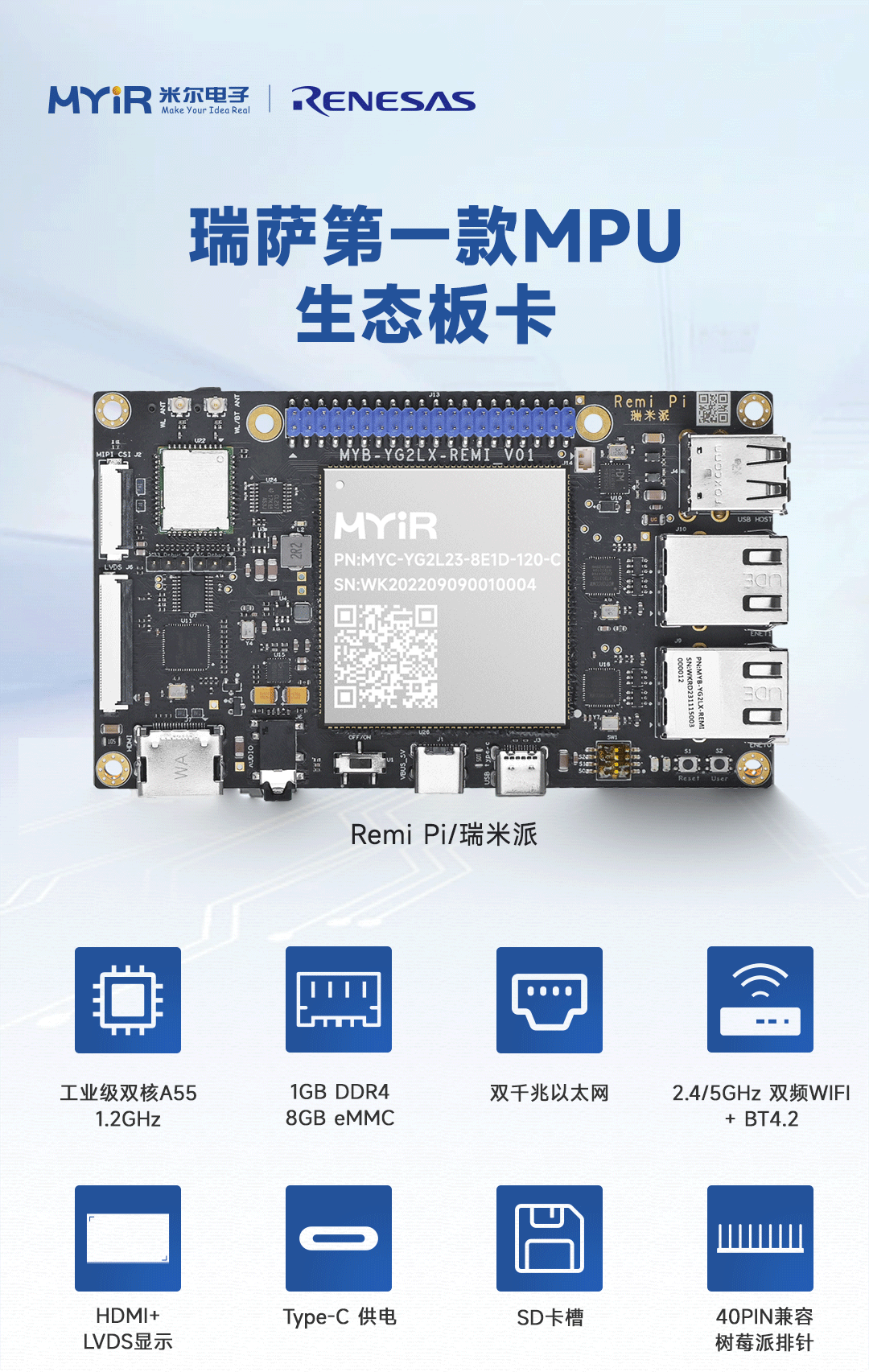

米尔基于MYD-YG2LX系统启动时间优化应用笔记

1.概述MYD-YG2LX采用瑞萨RZ/G2L作为核心处理器,该处理器搭载双核Cortex-A55@1.2GHz+Cortex-M33@200MHz处理器,其内部集成高性能3D加速引擎Mail-G31GPU(500MHz)和视频处理单元(支持H.264硬件编解码),16位的DDR4-1600/DDR3L-1333内存控制器、千兆以太网控制器、USB、CAN、

运放技术——基本电路分析

虚短和虚断的概念由于运放的电压放大倍数很大,一般通用型运算放大器的开环电压放大倍数都在80dB以上。而运放的输出电压是有限的,一般在10V~14V。因此运放的差模输入电压不足1mV,两输入端近似等电位,相当于“短路”。开环电压放大倍数越大,两输入端的电位越接近相等。“虚短”是指在分析运算放大器处于线性状态时,可把两输入端视为等电位,这一特性称为虚假短路,简称

飞凌嵌入式携手中移物联,谱写全国产化方案新生态

4月22日,飞凌嵌入式“2025嵌入式及边缘AI技术论坛”在深圳成功举办。中移物联网有限公司(以下简称“中移物联”)携OneOS操作系统与飞凌嵌入式共同推出的工业级核心板亮相会议展区,操作系统产品部高级专家严镭受邀作《OneOS工业操作系统——助力国产化智能制造》主题演讲。

ATA-2022B高压放大器在螺栓松动检测中的应用

实验名称:ATA-2022B高压放大器在螺栓松动检测中的应用实验方向:超声检测实验设备:ATA-2022B高压放大器、函数信号发生器,压电陶瓷片,数据采集卡,示波器,PC等实验内容:本研究基于振动声调制的螺栓松动检测方法,其中低频泵浦波采用单频信号,而高频探测波采用扫频信号,利用泵浦波和探测波在接触面的振动声调制响应对螺栓的松动程度进行检测。通过螺栓松动检测

MOS管驱动电路——电机干扰与防护处理

此电路分主电路(完成功能)和保护功能电路。MOS管驱动相关知识:1、跟双极性晶体管相比,一般认为使MOS管导通不需要电流,只要GS电压(Vbe类似)高于一定的值,就可以了。MOS管和晶体管向比较c,b,e—–>d(漏),g(栅),s(源)。2、NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以

压敏(MOV)在电机上的应用剖析

一前言有刷直流电机是一种较为常见的直流电机。它的主要特点包括:1.结构相对简单,由定子、转子、电刷和换向器等组成;2.通过电刷与换向器的接触来实现电流的换向,从而使电枢绕组中的电流方向周期性改变,保证电机持续运转;3.具有调速性能较好等优点,可以通过改变电压等方式较为方便地调节转速。有刷直流电机在许多领域都有应用,比如一些电动工具、玩具、小型机械等。但它也存

硬件原理图学习笔记

这一个星期认真学习了硬件原理图的知识,做了一些笔记,方便以后查找。硬件原理图分为三类1.管脚类(gpio)和门电路类输入输出引脚,上拉电阻,三极管与门,或门,非门上拉电阻:正向标志作用,给悬空的引脚一个确定的状态三极管:反向三极管(gpio输出高电平,NP两端导通,被控制端导通,电压为0)->NPN正向三极管(gpio输出低电平,PN两端导通,被控制端导通,

TurMass™ vs LoRa:无线通讯模块的革命性突破

TurMass™凭借其高传输速率、强大并发能力、双向传输、超强抗干扰能力、超远传输距离、全国产技术、灵活组网方案以及便捷开发等八大优势,在无线通讯领域展现出强大的竞争力。

RZT2H CR52双核BOOT流程和例程代码分析

RZT2H是多核处理器,启动时,需要一个“主核”先启动,然后主核根据规则,加载和启动其他内核。本文以T2H内部的CR52双核为例,说明T2H多核启动流程。

基于FPGA验证所设计的ADPCM算法语音编解码电路

基于FPGA验证所设计的ADPCM算法语音编解码电路

评论