摘要:在m序列产生原理的基础上,利用2片74LS194级联及少量门电路,采用手动置数和自启动2种方法设计了2种m序列发生器电路,然后分析比较了2种电路的产生原理.最后分析了实验结果,验证了m序列的均衡性、游程分布特性及移位相加性.电路性能稳定可靠,已作为数字信号源成功应用于通信原理实验中

1、m序列的产生原理

m序列发生器是一种反馈移位型结构的电路,它由n级移位寄存器加异或反馈网络组成,其生成序列长度p=2n-1,且只有1个冗余状态即全0状态,所以称为最长线性反馈移位寄存器序列.由于带有反馈,因此在移位脉冲作用下,移位寄存器各级的状态将不断变化,通常移位寄存器的最后一级做输出,输出序列为邀ak妖=a0a1…an-1…

输出序列是一个周期序列,其特性由移位寄存器的级数、初始状态、反馈逻辑以及时钟速率(决定着输出码元的宽度)所决定.

当移位寄存器的级数与时钟一定时,输出序列就由移位寄存器的初始状态和反馈逻辑所完全确定.当初始状态为全零状态时,移位寄存器输出全0序列.为了避免这种情况,需设置全0排除电路。

2、m序列发生器的电路设计

2.1芯片介绍

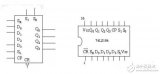

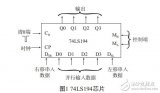

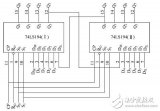

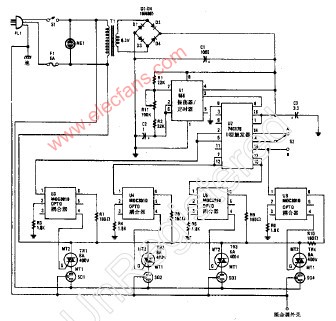

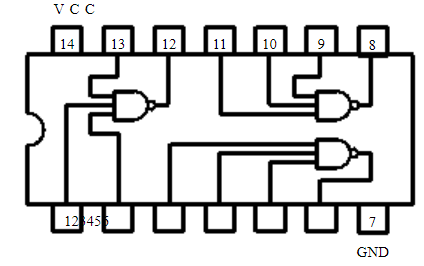

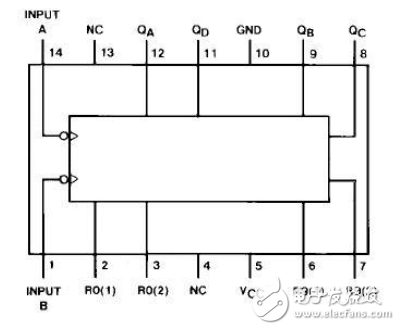

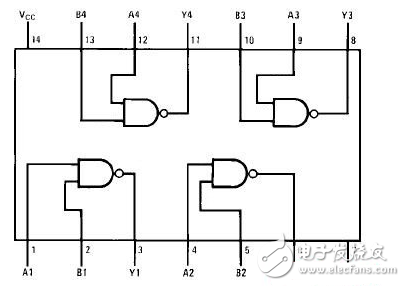

本设计采用2片4级移位寄存器芯片74LS194及少量分立元件构成,74LS194的引脚及内部逻辑图如图2所示.

74LS194是一种典型的中规模集成移位寄存器,由4个RS触发器和一些门电路构成.它是4级双向移位寄存器,是一种功能很强的通用寄存器,其具体逻辑功能由管脚9和管脚10的S0与S1来确定.它具有并行输入、并行输出、左移、右移及保持等5个功能.其中D0,D1,D2和D3为并行数据输入端;Q0,Q1,Q2和Q3为4个触发器输出端;SR为右移串行输入端;SL为左移串行输入端;S0与S1为操作模式控制端;Cr为直接无条件清零端;CP为时钟脉冲输入端.

当S0S1=00时,为状态保持;S0S1=01为数据右移;S0S1=10为数据左移;S0S1=11为并行送数.74LS194功能表如表1所示

2.2电路设计与分析

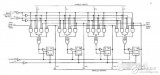

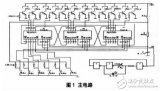

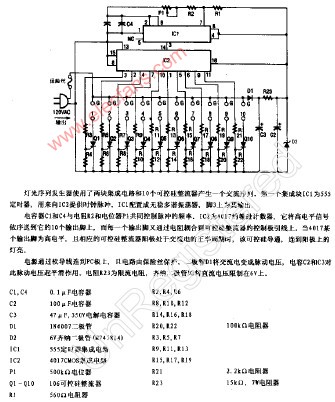

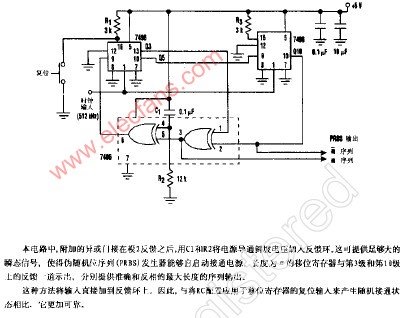

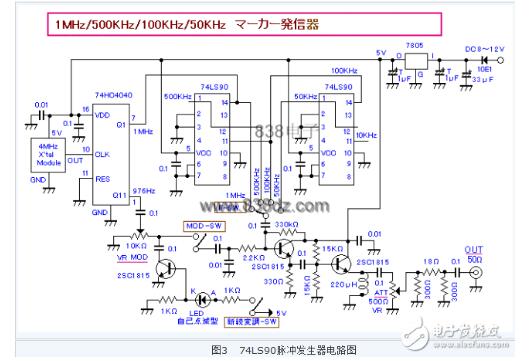

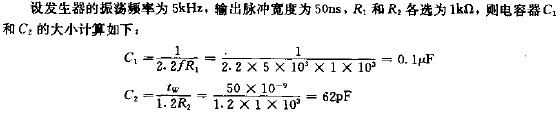

要想产生周期为255的最长序列,要求m序列发生器的特征多项式必须是8次本原多项式,通过查表得到其本原多项式为x8+x4+x3+x2+1,即第8,4,3,2级参与反馈经异或后送入第1级.所设计的8级m序列发生器原理方框图如图3所示.

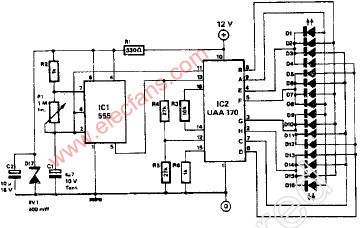

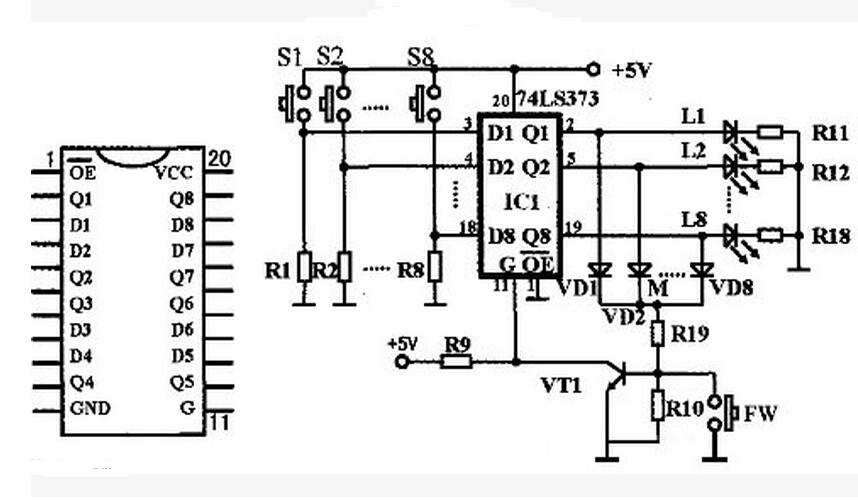

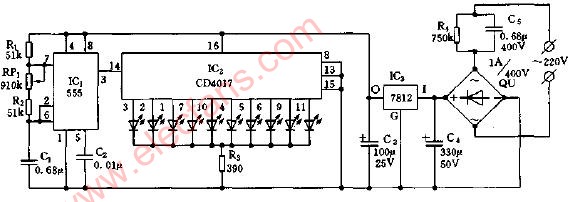

依据上述原理,设计了2种产生电路,分别如图4和图5所示.

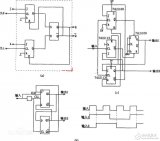

方案1:通过手动置数右移产生m序列.

方案2:利用全0状态重新置数从而实现自启动

方案1的电路设计如图4所示.当电路处于全0状态时,采用此方法设计的m序列发生器不具有自启动特性.为了使电路启动,可以断开开关S1,将74LS194的工作方式控制端S1置高电平,这时S1和S0均为高电平,即S1S0=11,74LS194处于置数状态,把输入端的初始状态10000000置到输出端.然后再闭合开关S1,使74LS194的工作方式控制端S1处于低电平状态.这时工作方式控制端S1与S0分别为低电平和高电平,即S1S0=01,74LS194处于右移状态,在时钟作用下通过不断移位产生m序列.

当初始状态为全零状态时,移位寄存器输出全0序列.为了避免这种情况,需设置全0排除电路.方案2的电路设计如图5所示.利用全0状态重新置数从而实现自启动.当电路处于全0状态时,通过或门和非门电路的作用,S1置高电平,这时候S1和S0均为高电平,即S1S0=11,74LS194处于置数状态,自动把输入端的初始状态01000000置到输出端.通过或门和非门电路的作用,使S1处于低电平状态,即S1S0=01,74LS194处于右移状态,在时钟作用下通过不断移位产生m序列.

比较2种方案,通过设置工作方式控制端使之右移都能产生长度为255的m序列.方案1的电路设计简单,只需手动置数就能产生m序列;方案2的电路设计较方案1复杂,但它能在全0状态下自启动,电路性能稳定。

3.实验结果与性质分析

3.1实验结果

这里只分析方案2的电路,由图5可知,其初始状态为a7=a5=a4=a3=a2=a1=a0=0,a6=1.当m序列发生器利用全0状态重新置数实现自启动时,它能生成长度为255的m序列.如下所示:

邀an妖=111111110010000101001111101010101110000011000101011001100101111110111100110111011100

10101001010001001011010001100111001111000110110000100010111010111101101111100001101001101011011

01010000010011101“100100100110000001110100100011100”01000000010110001111010000.

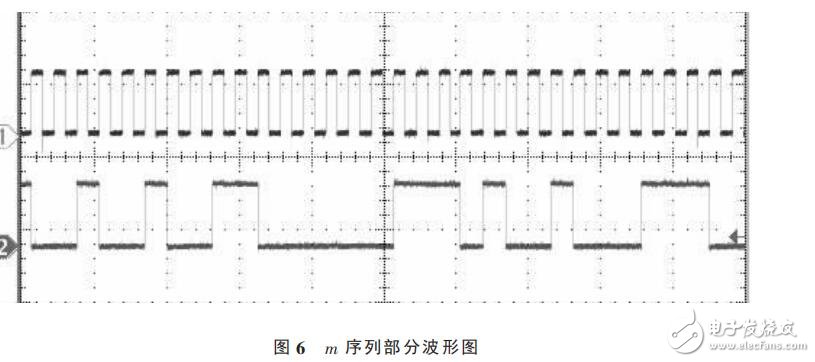

由于示波器显示的波形长度有限,不能一次性显示255位m序列波形[5].图6为255位m序列的部

分波形图.第1路波形为8kHz时钟,第2路波形是产生的m序列部分波形,对应于序列中的引号内部分。

3.2性质分析

3.2.1m序列的均衡性

m序列每一周期中1的个数比0的个数多1个.由于p=2n-1为奇数,因而在每一周期中1的个数为偶数,即(p+1)/2=2n-1;而0的个数为奇数,即(p-1)蛐2=2n-1-1.当p足够大时,在一个周期中1与0出现的次数基本相等.本设计中的8级m序列中p=255,1的个数为128,0的个数为127,即0与1出现的概率几乎相等.

3.2.2m序列的游程分布

将一个序列中取值(1或0)相同连在一起的元素合称为一个游程.在一个游程中元素的个数称为游程长度.统计分析产生序列特性.

对于游程长度0<k≤6,全部游程如下:长度为1的0游程和1游程分别出现32次;长度为2的0游程和1游程分别出现16次;长度为3的0游程和1游程分别出现8次;长度为4的0游程和1游程分别出现4次;长度为5的0游程和1游程分别出现2次;长度为6的0游程和1游程分别出现1次;长度为7的0游程出现1次;长度为8的1游程出现1次,如表2所示。

m序列的一个周期中,游程总数为128.其中长度为1的游程个数占游程总数的1蛐2;长度为2的游程个数占游程总数的1蛐4;长度为3的游程个数占游程总数的1蛐8;……一般地,长度为k的游程个数占游程总数的2-k=2k,其中1≤k≤(n-2),而且,在长度为k的游程中,连1游程与连0游程各占一半,长为(n-1)的游程是连0游程,长为n的游程是连1游程。

3.2.3移位相加特性(线性叠加性)

m序列和其位移序列模2和后所得序列仍是该m序列的某个位移序列.设mr是周期为p的m序列mp经过r次延迟移位后的序列,那么有mp茌mr=ms,其中ms为mp某次延迟移位后的序列。

本设计产生的序列为mp,

mp=111111110010000101001111101010101110000011000101011001100101111110111100110111011100

10101001010001001011010001100111001111000110110000100010111010111101101111100001101001101011011

0101000001001110110010010011000000111010010001110001000000010110001111010000妖.

mp延迟1位后得到序列mr,

mr=0111111110010000101001111101010101110000011000101011001100101111110111100110111011100

10101001010001001011010001100111001111000110110000100010111010111101101111100001101001101011011

010100000100111011001001001100000011101001000111000100000001011000111101000妖.

mp与mr模2和后所得序列ms,

mr=邀1000000010110001111010000111111110010000101001111101010101110000011000101011001100101

11111011110011011101110010101001010001001011010001100111001111000110110000100010111010111101101

111100001101001101011011010100000100111011001001001100000011101001000111000妖.

由运算结果可以看到,ms为mp延迟25位后的序列.

4、结语

文中给出的 2 种 m 序列产生电路经实际硬件测试,输出信号波形符 合 m 序 列 的 均 衡 性、游 程 分 布特性、移位相加性等性质.结果表明:采用 74LS194 加上少量外围芯片,可以方便、准确地产生 m 序列.文中给出的设计方法调试方便,电路性能稳定可靠,具有实际应用价值,已作为数字信号源成功应用于通信原理实验箱。

电子发烧友App

电子发烧友App

评论