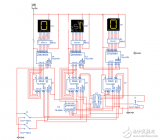

2.设计的实现

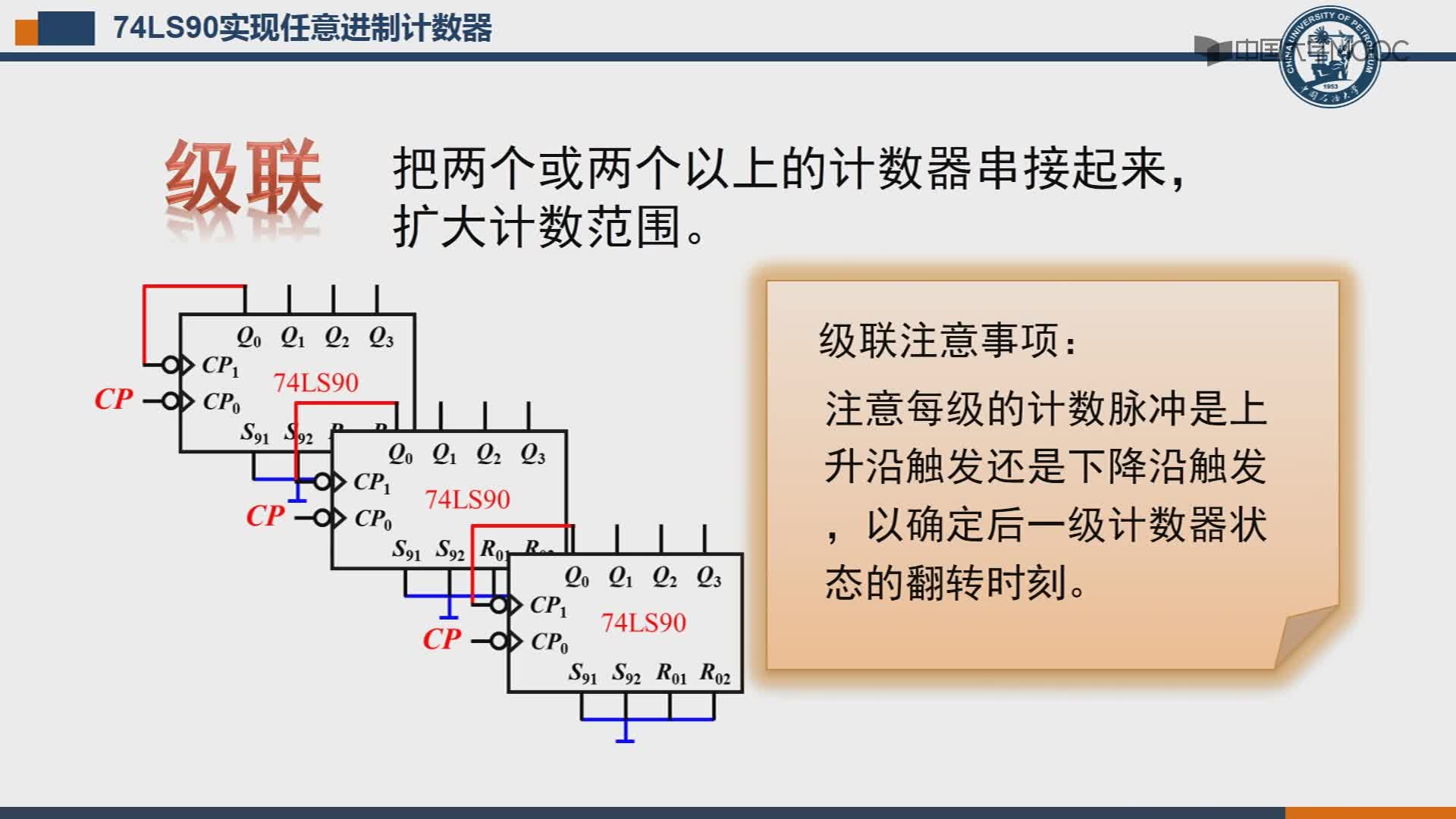

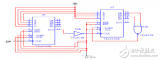

1) 两芯片之间级联;把作高位芯片的进位端与下一级up端连接这是由两片74LS90连接而成的60进制计数器,低位是连接成为一个十进制计数器,它的clk端接的是低位的进位脉冲。高位接成了六进制计数器。当输出端为0101 的时候在下个时钟的上升沿把数据置数成0000 这样就形成了进制计数器,连个级联就成为了60进制计数器,分别可以作为秒和分记时。

2) 方案的实现:

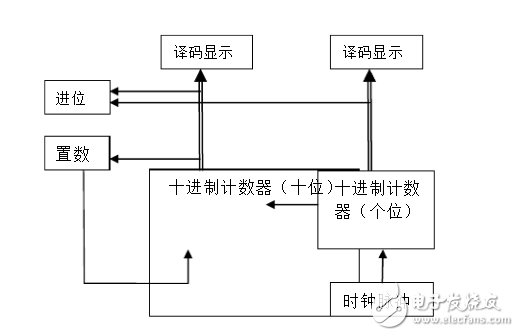

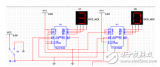

使用200HZ时钟信号作为计数器的时钟脉冲。根据设计基理可知,计数器初值为00,按递增方式计数,增到59时,再自动返回到00。此电路可以作为简易数字时钟的分钟显示。下图为60进制计数器的总体框图。

六十进制计数器的设计与仿真

1.基本电路分析设计

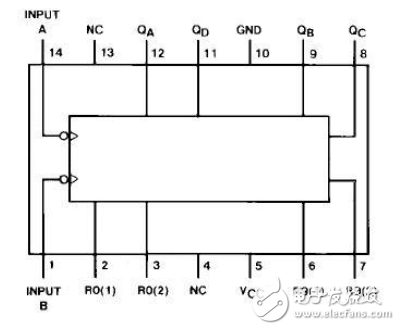

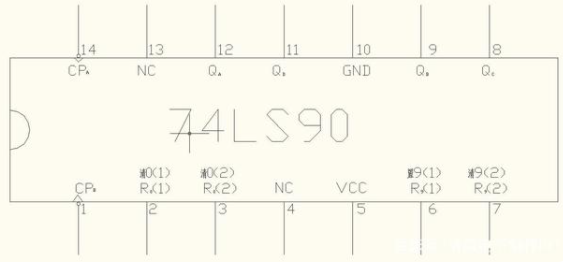

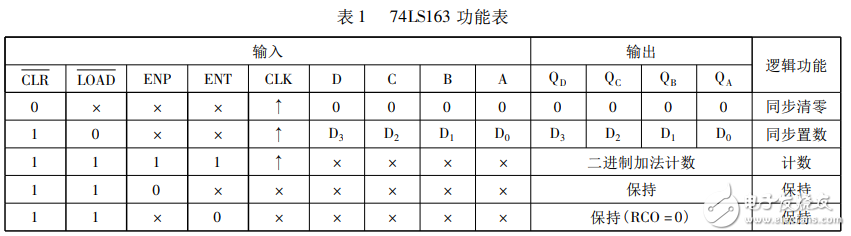

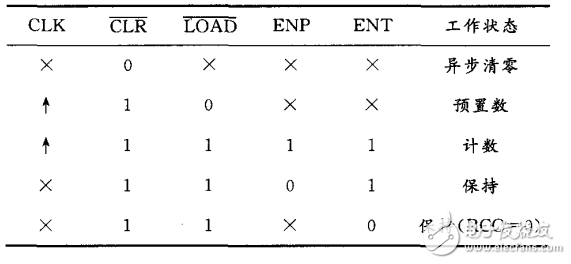

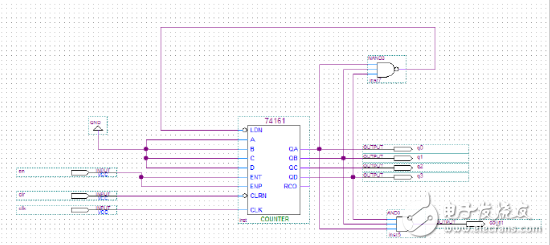

1) 十进制计数器(个位)电路本电路采用74LS160作为十进制计数器,它是一个具有异步清零、同步置数、可以保持状态不变的十进制上升沿计数器。

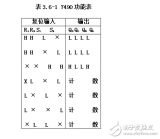

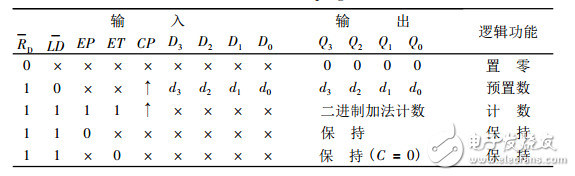

2) 功能表如下;

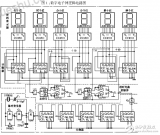

连接方式如下图:

3) 十进制计数器(十位)电路

图3 十进制计数器(十位)

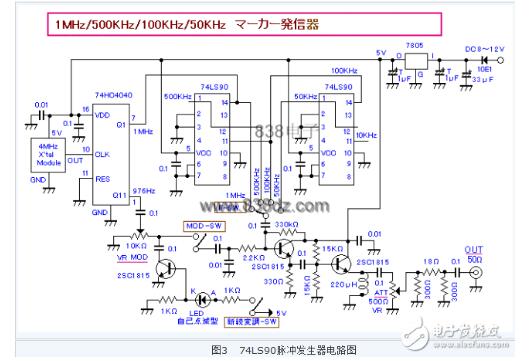

4) 时钟脉冲电路

5) 置数电路

6) 进位电路

7)译码显示电路

8)选定仪器列表

电子发烧友App

电子发烧友App

评论