计数器种类很多。按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。根据计数制的不同,分为二进制计数器、十进制计数器和任意进制计数器。根据计数器的增减趋势,又分为加法、减法和可逆计数器。还有可预制数和可变程序功能计数器等等。目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。使用者只要借助于器件手册提供的功能和工作波形图以及引出端的排列,就能正确运用这些器件。

计数器在现代社会中用途中十分广泛,在工业生产、各种和记数有关电子产品。如定时器,报警器、时钟电路中都有广泛用途。在配合各种显示器件的情况下实现实时监控,扩展更多功能。

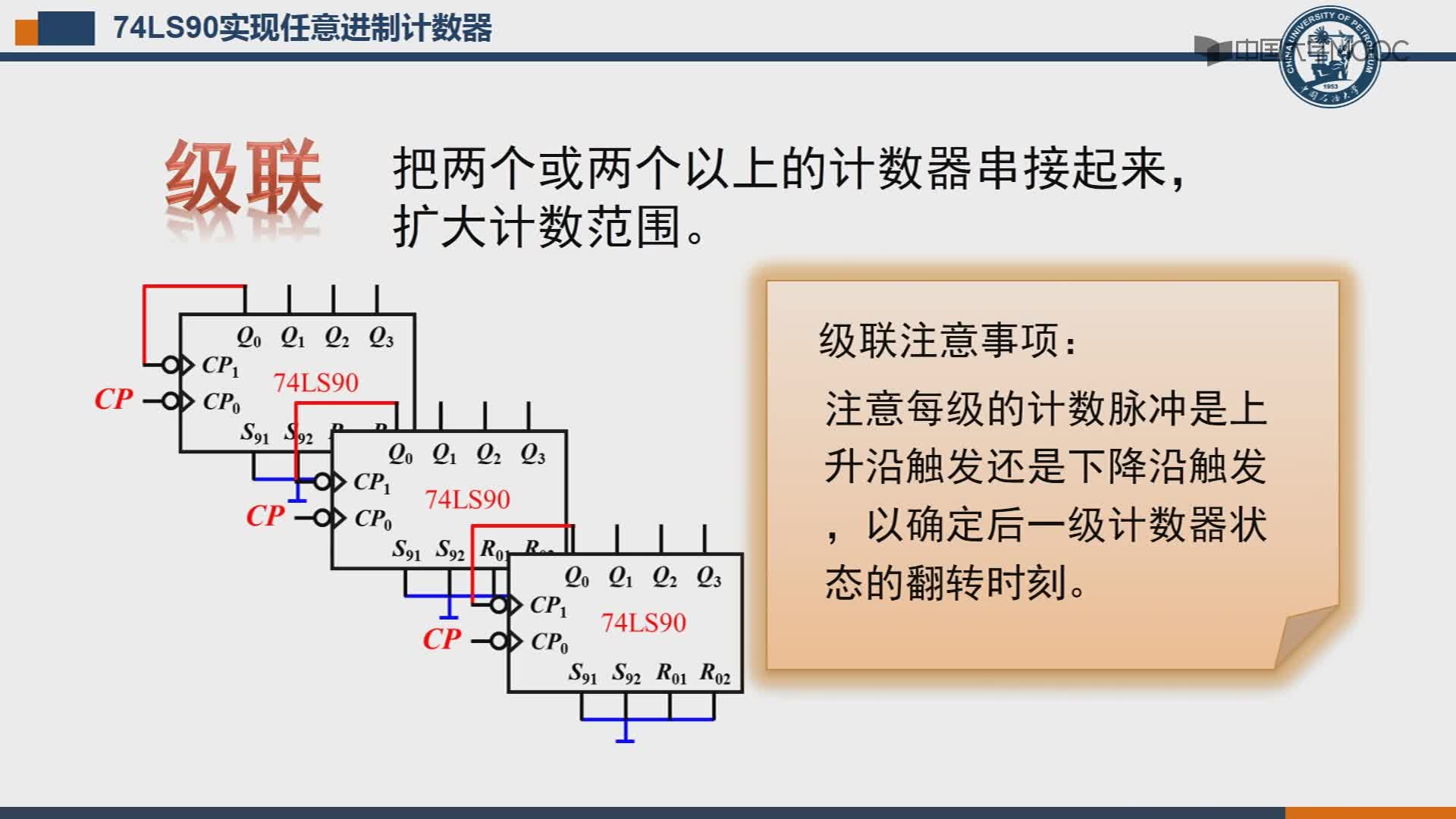

60进制计数器,由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的十进制计数器,从设计简便考虑,芯片选择同步十进制计数器

1.计数器设计目的

1) 每隔1s,计数器增1;能以数字形式显示时间。

2) 熟练掌握计数器的各个部分的结构。 3) 计数器间的级联。

4) 不同芯片也可实现六十进制。

2.计数器设计组成

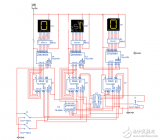

1) 用两个74ls192芯片和一个与非门实现。

2) 当定时器递增到59时,定时器会自动返回到00显示,然后继续计时。

3) 本设计主要设备是两个74LS160同步十进制计数器,并且由200HZ,5V电源供给。作高位芯片与作低芯片位之间级联。

4) 两个芯片间的级联。

六十进制计数器设计描述

1.设计的思路

1) 芯片介绍:

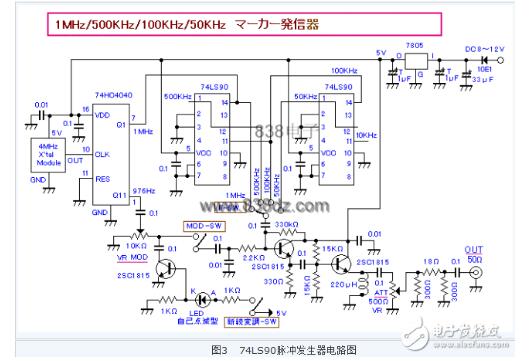

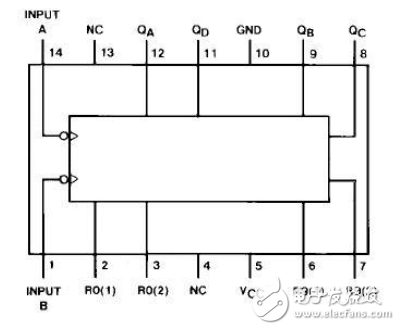

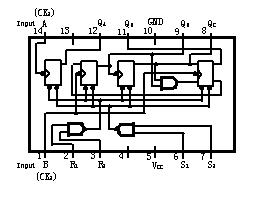

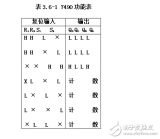

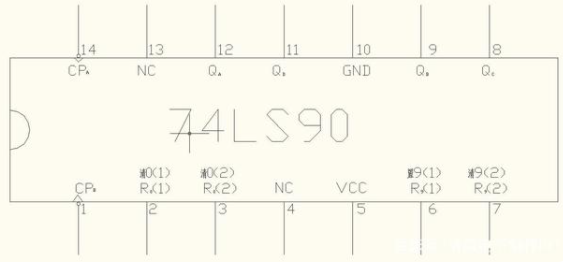

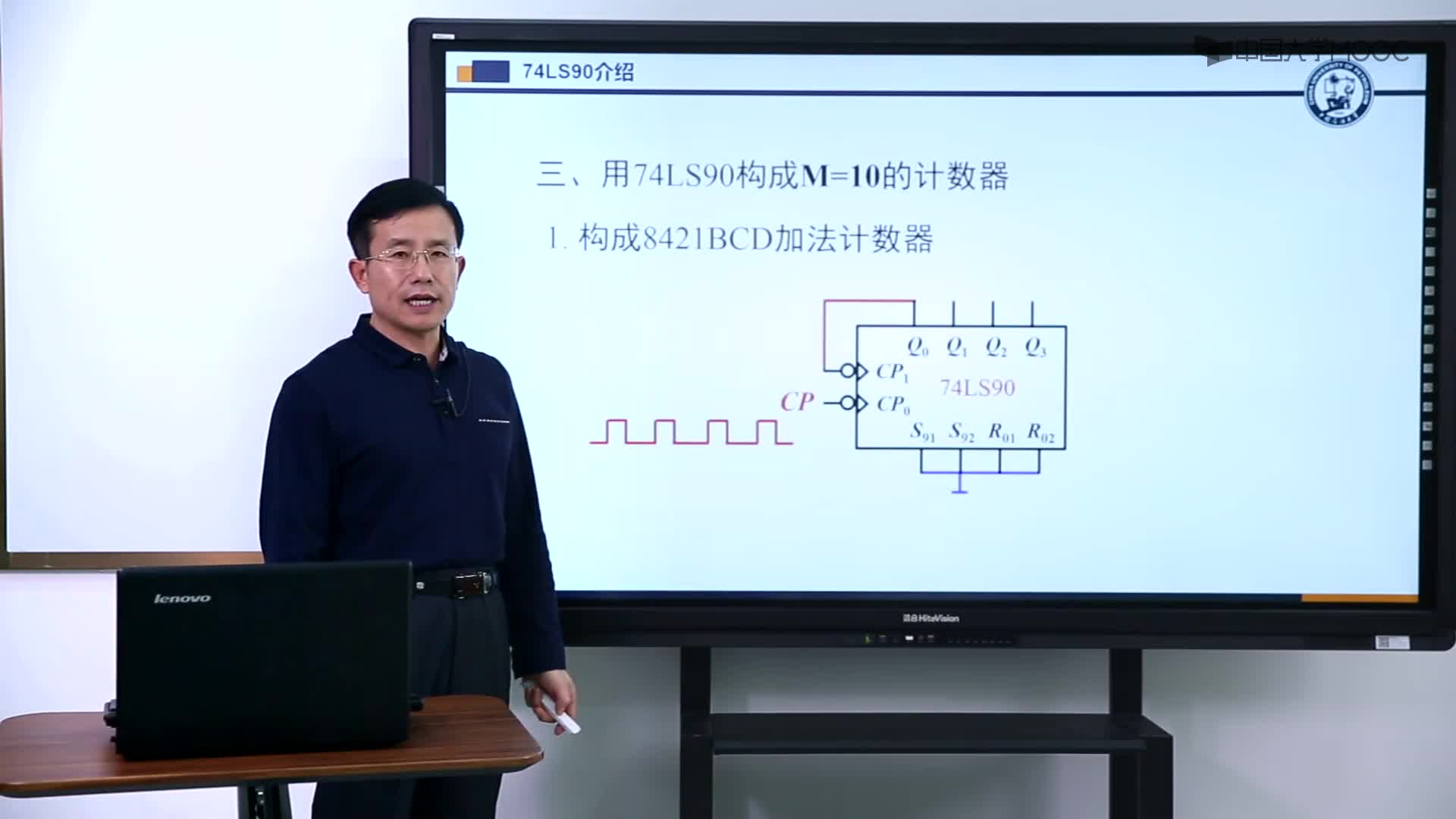

74LS90计数器是一种中规模二-五-十进制异步计数器,管脚图如图所示。 R01、R02是计数器置0端,同时为1有效;R91和R92为置9端,同时为1时有效;若用A输入,QA输出,为二进制计数器;如B为输入,QB-QD可输出五进制计数器;将QA与B相连,A做为输入端,QA-QD输出十进制计数器;若QD与A输入端相连,B为输入端,电路为二-五混合进制计数器。

74LS192 为加减可逆十进制计数器,CPU端是加计数器时钟信号,CPD是减计数时钟信号RD=1 时无论时钟脉冲状态如何,直接完成清零功能。RD=0,LD=0 时,无论时钟脉冲状态如何,输入信号将立即被送入计数器的输出端,完成预置数功能。

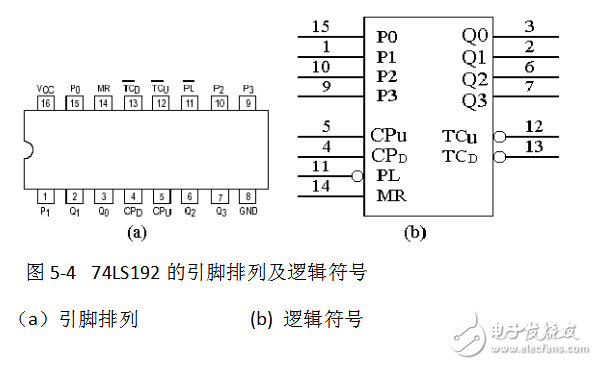

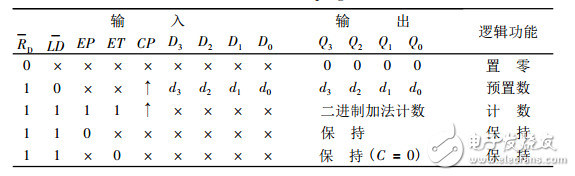

2) 十进制可逆计数器74LS192引脚图管脚及功能表

3) 74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

图中:PL为置数端,CPu为加计数端,CPd为减计数端,TCu为非同步进位输出端, TCd为非同步借位输出端,P0、P1、P2、P3为计数器输入端,MR为清除端,Q0、Q1、Q2、Q3为数据输出端。

4) 利用两片74ls192分别作为六十进制计数器的高位和低位,分别与数码管连接。把其中的一个芯片连接构成十进制计数器,另一个通过一个与门器件构成一个六进制计数器。

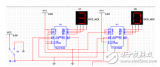

5) 如下图:

2.设计的实现

1) 两芯片之间级联;把作高位芯片的进位端与下一级up端连接这是由两片74LS90连接而成的60进制计数器,低位是连接成为一个十进制计数器,它的clk端接的是低位的进位脉冲。高位接成了六进制计数器。当输出端为0101 的时候在下个时钟的上升沿把数据置数成0000 这样就形成了进制计数器,连个级联就成为了60进制计数器,分别可以作为秒和分记时。

2) 方案的实现:

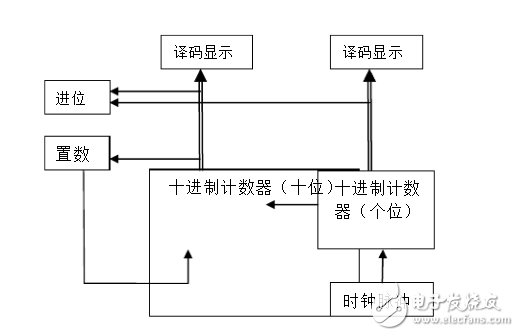

使用200HZ时钟信号作为计数器的时钟脉冲。根据设计基理可知,计数器初值为00,按递增方式计数,增到59时,再自动返回到00。此电路可以作为简易数字时钟的分钟显示。下图为60进制计数器的总体框图。

六十进制计数器的设计与仿真

1.基本电路分析设计

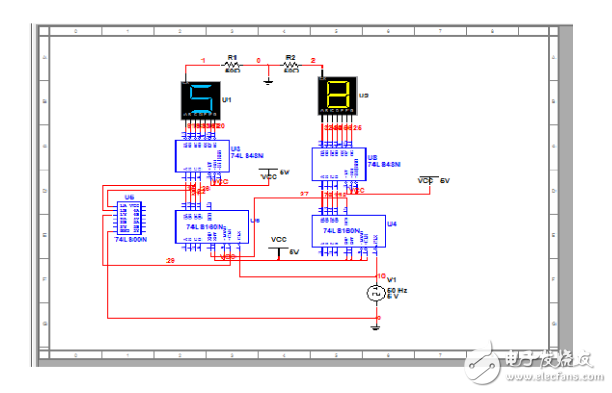

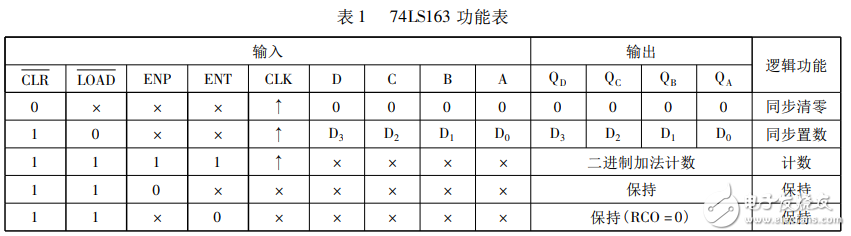

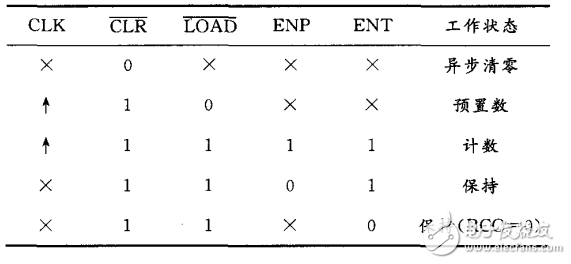

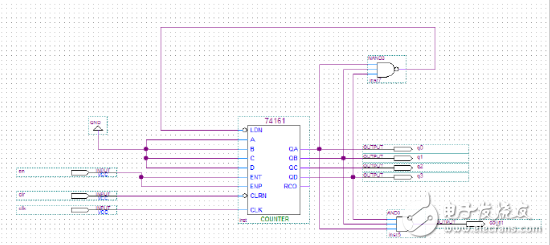

1) 十进制计数器(个位)电路本电路采用74LS160作为十进制计数器,它是一个具有异步清零、同步置数、可以保持状态不变的十进制上升沿计数器。

2) 功能表如下;

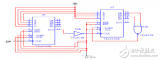

连接方式如下图:

3) 十进制计数器(十位)电路

图3 十进制计数器(十位)

4) 时钟脉冲电路

5) 置数电路

6) 进位电路

7)译码显示电路

8)选定仪器列表

仿真电路图

实训总结

1.遇到的问题及解决方法

1) 在设计过程中我查阅了大量的资料,了解了许多关于计数器设计方面的问题,进一步理解了各种元器件的使用方法。

2) 这次课程设计让我学到了很多,不仅掌握了简单的电子电路的设计与制作,也掌握了毕业设计写作的方法和格式。在制作电路时,我深深体会到连接电路时一定要认真仔细,每一步骤都要认真分析。

3) 本次课程设计也反映出很多问题,比如竞争—冒险现象是很常见的,并且消除此现象并不是很容易,尤其是对结构复杂的电路而言,往往消除了一处竞争—冒险现象,又产生了另一处,此问题需要我以后多加注意。

电子发烧友App

电子发烧友App

评论