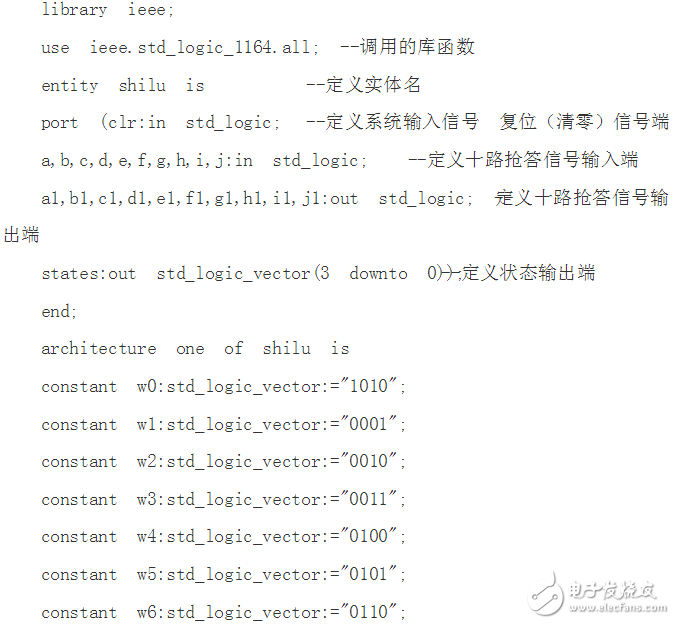

五人表决器电路设计方案五:基于FPGA的五人表决器

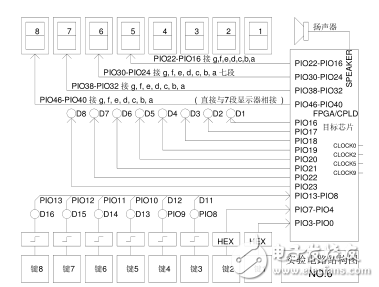

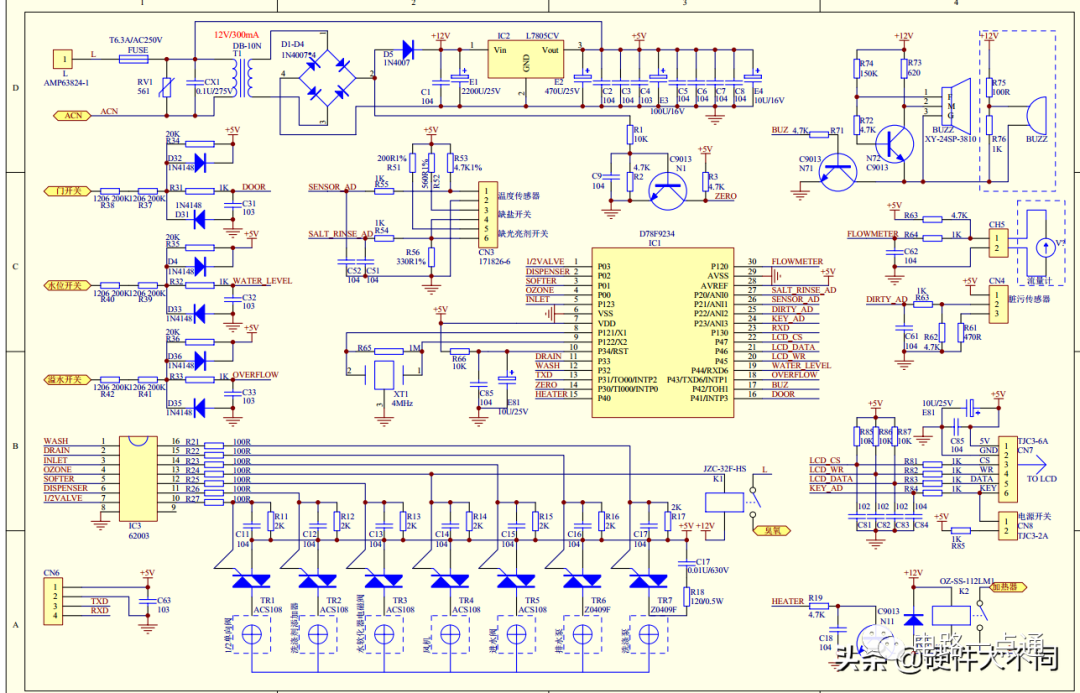

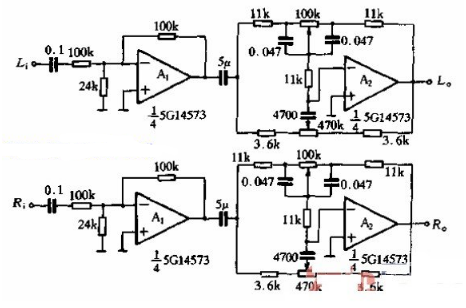

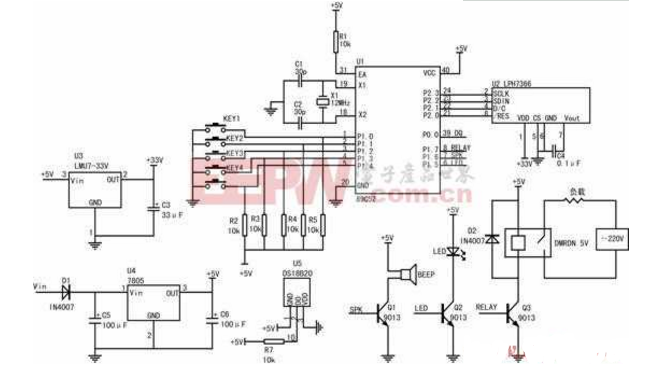

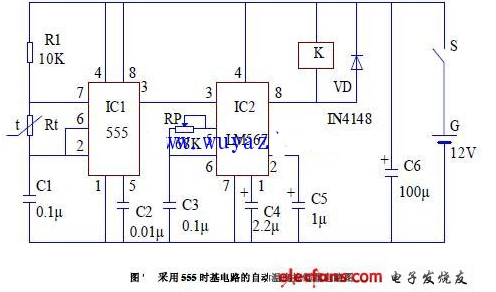

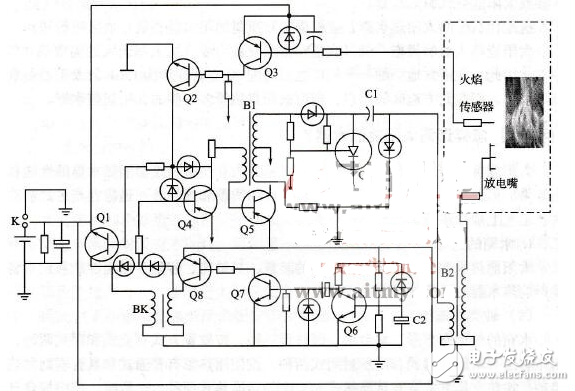

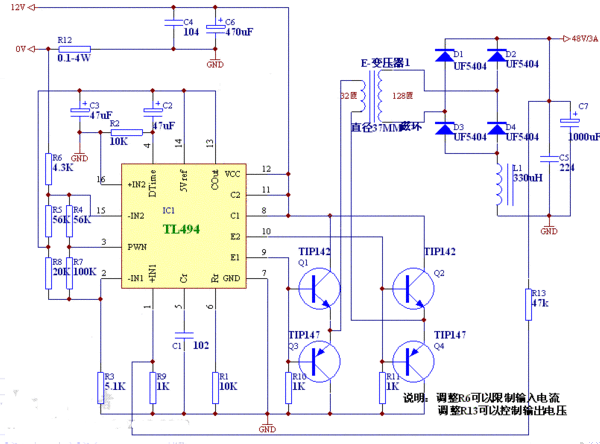

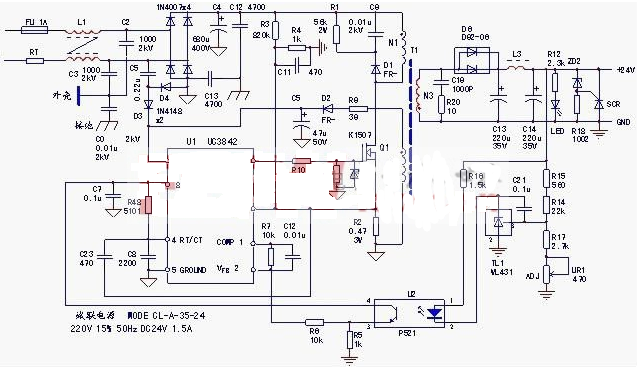

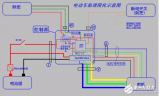

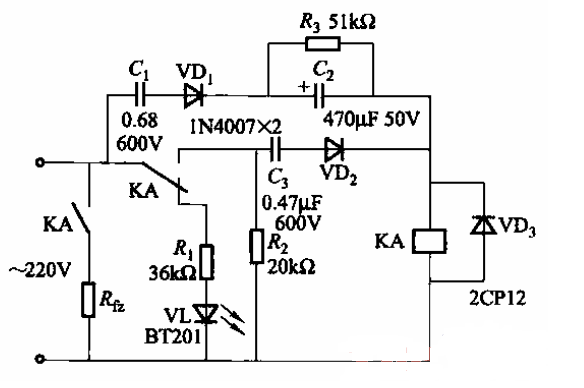

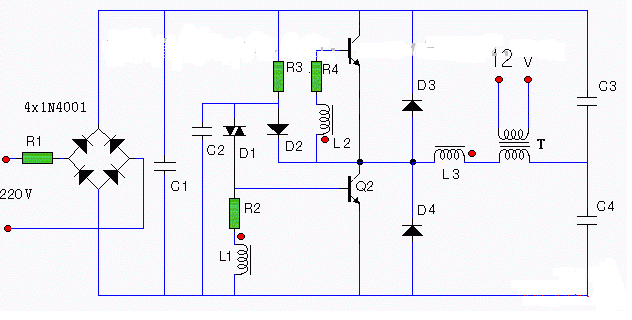

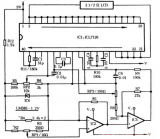

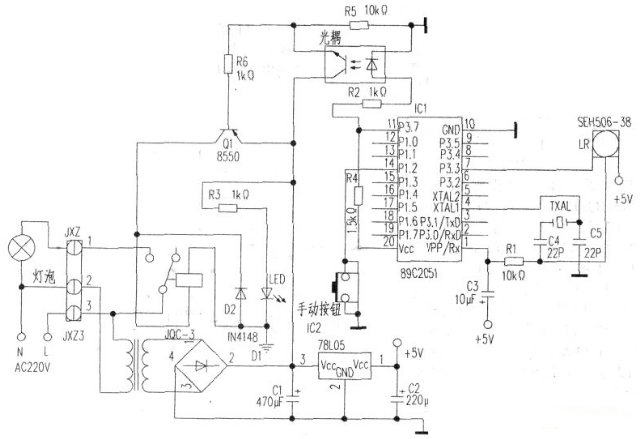

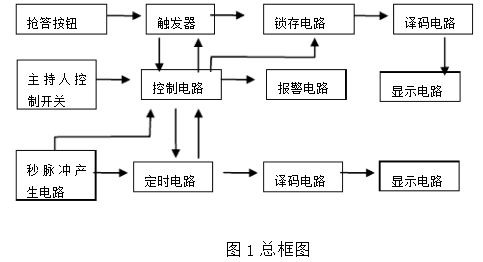

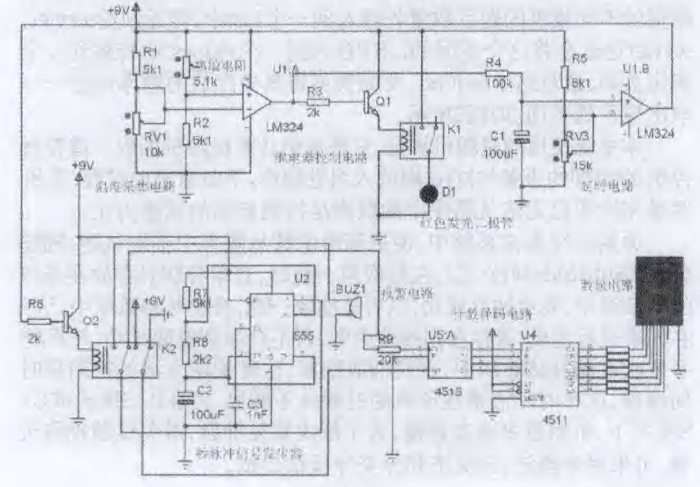

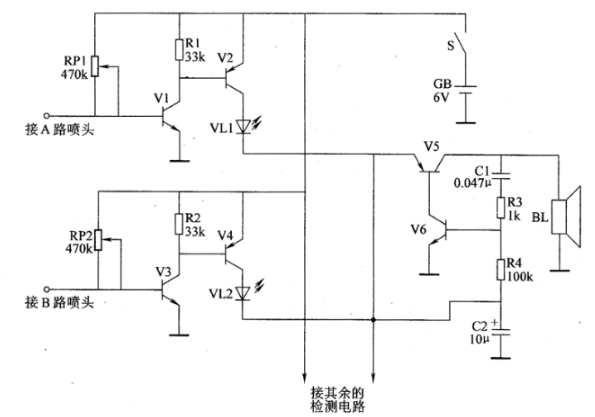

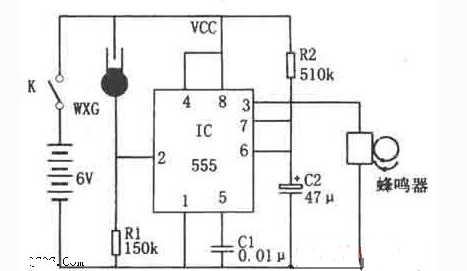

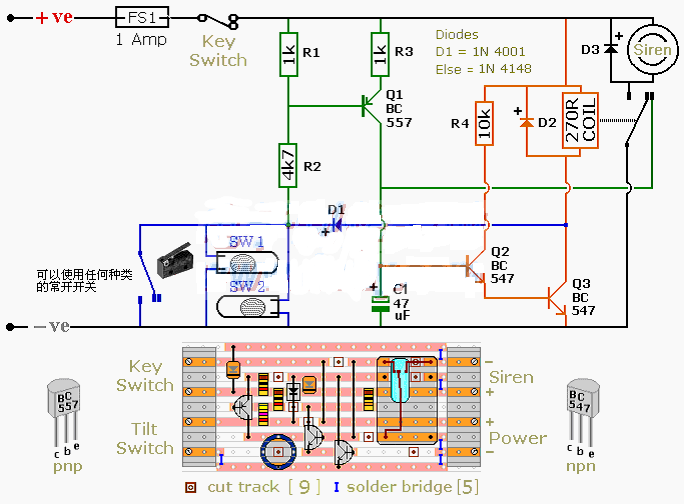

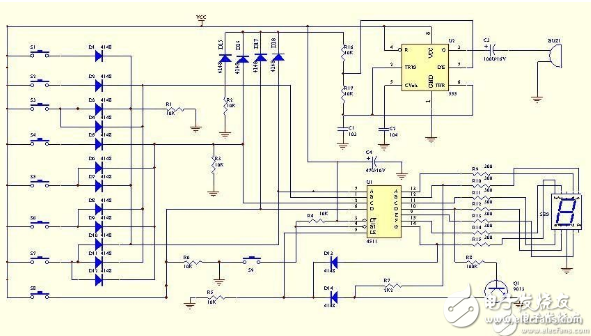

电路原理图

此电路图可实现表决器的控制与显示。键8 到键2 分别为五位投票者和复位,开始键。通过数码管显示投票人数,和剩余时间。二极管D8 显示通过与不通过。

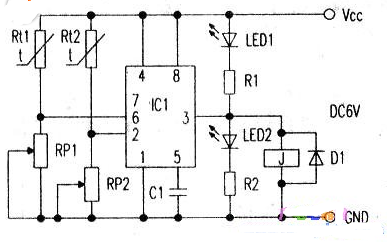

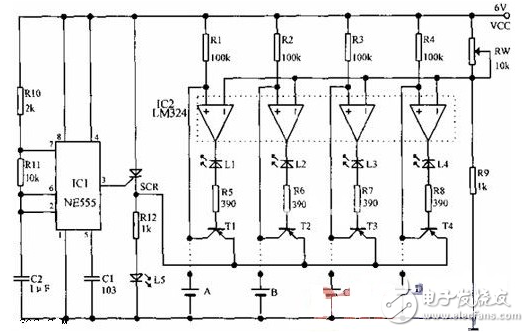

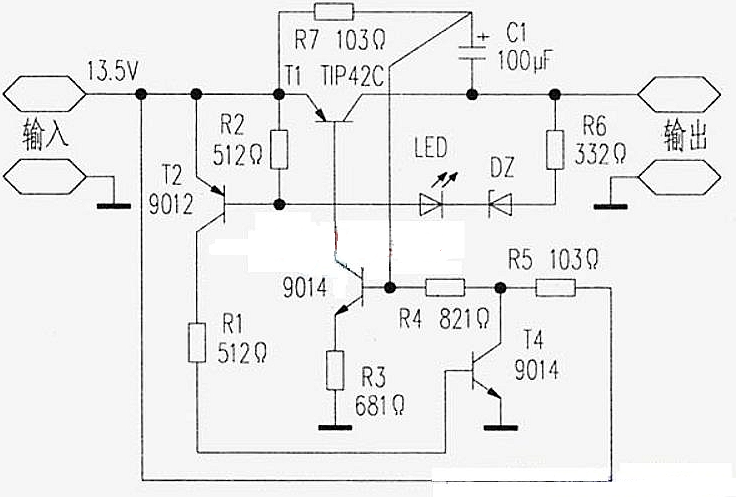

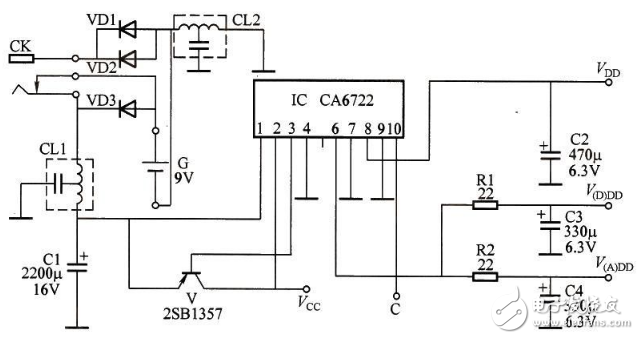

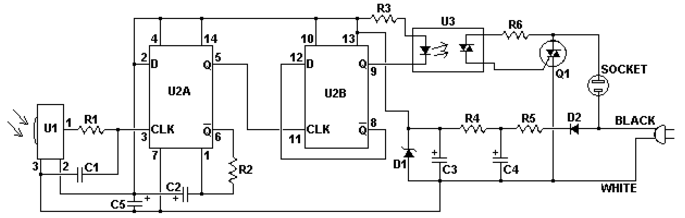

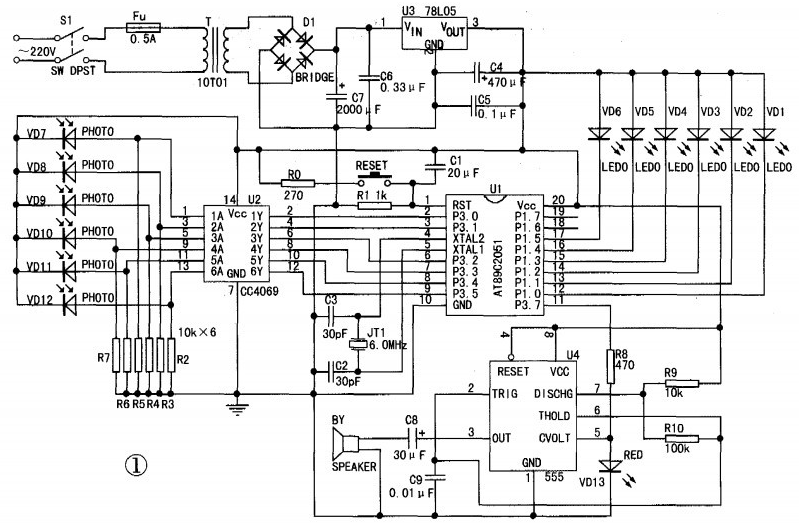

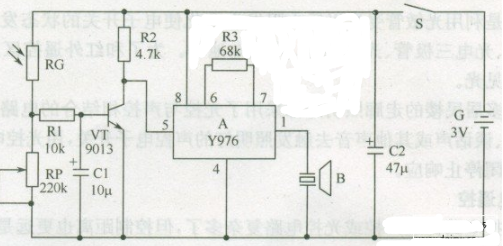

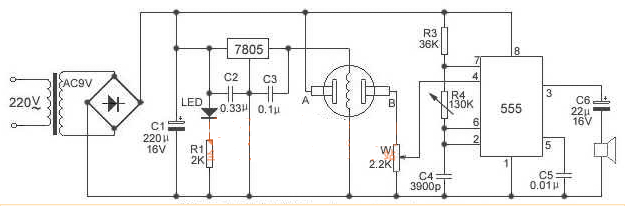

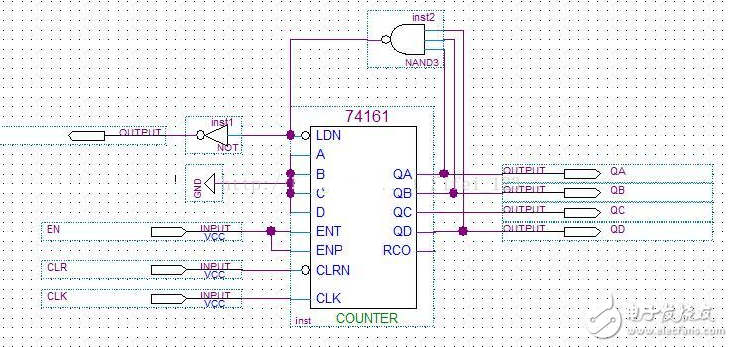

引脚锁定

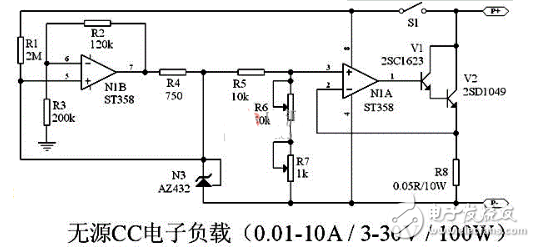

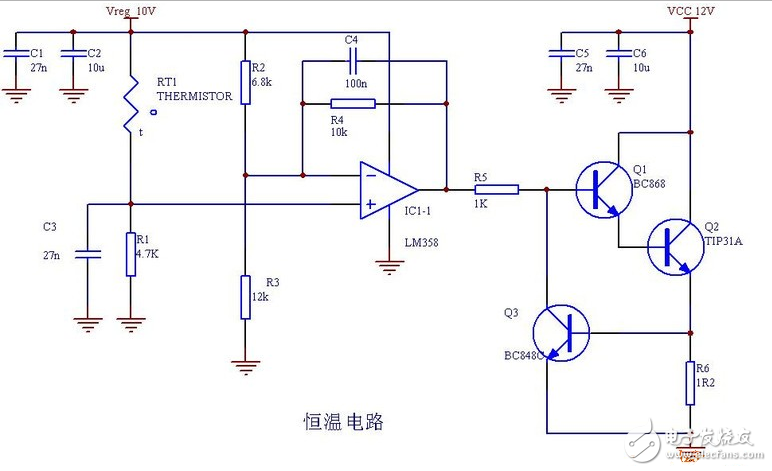

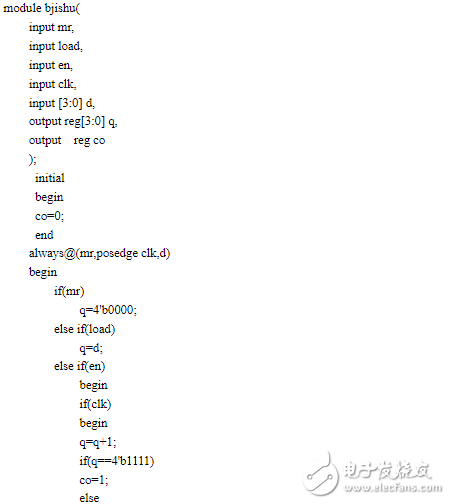

仿真

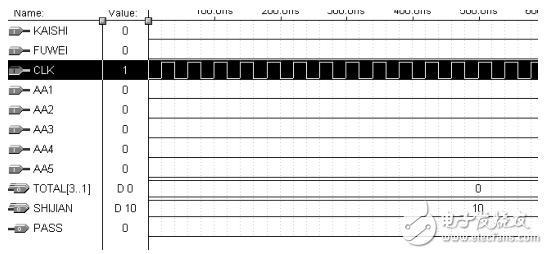

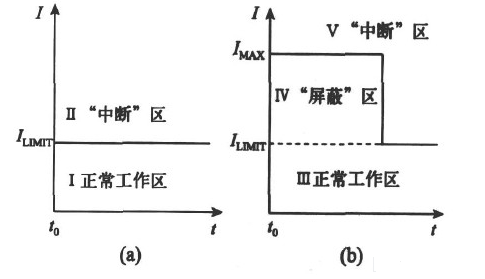

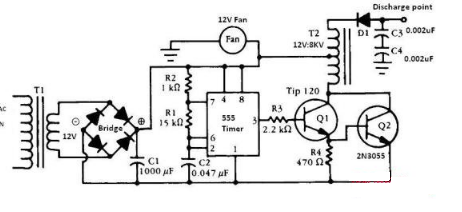

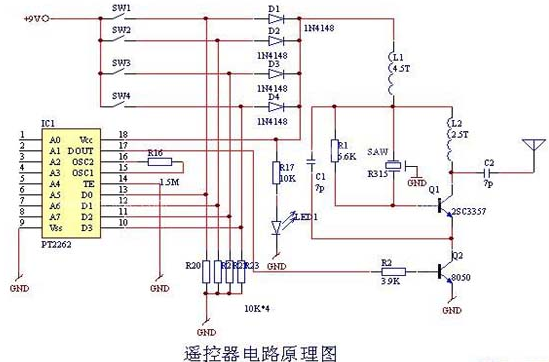

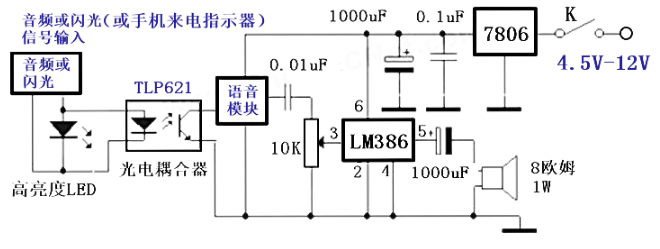

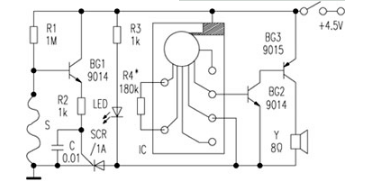

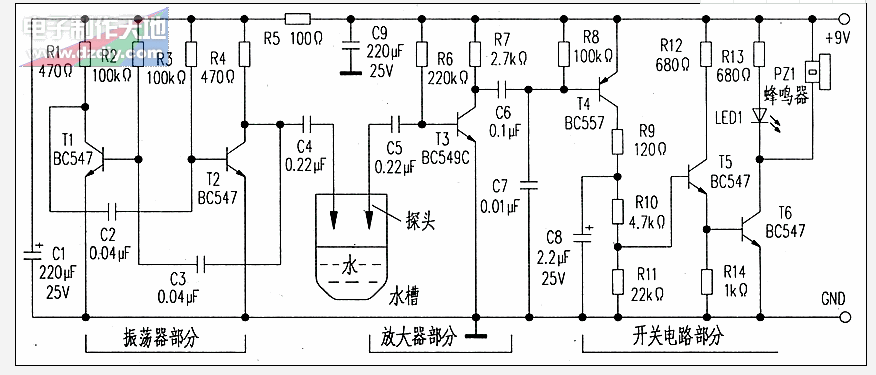

当处于复位状态时,外界的输入对结果没有影响。故时间仍为10 秒,输出统计人数为0。仿真波形如下图所示。

复位时的模拟结果

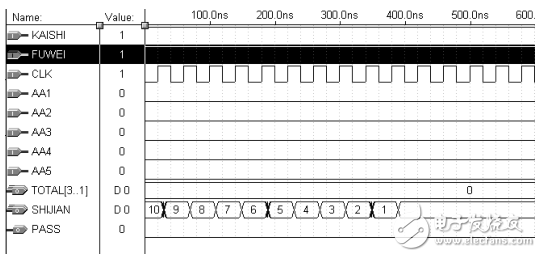

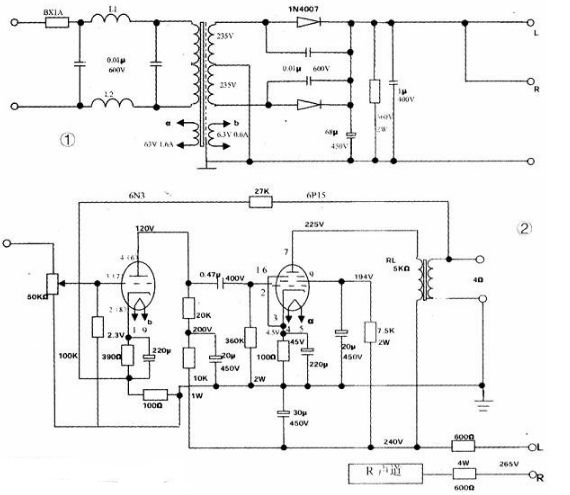

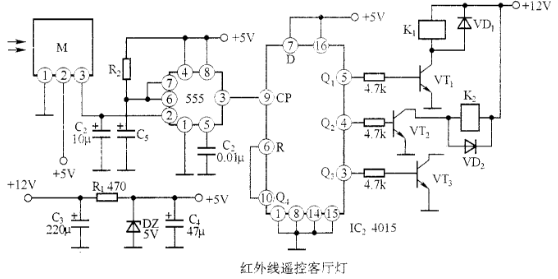

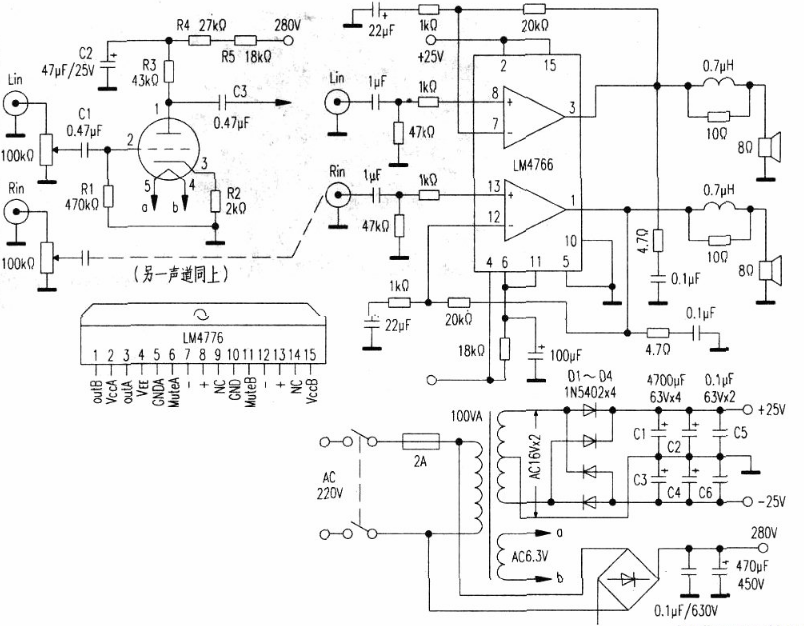

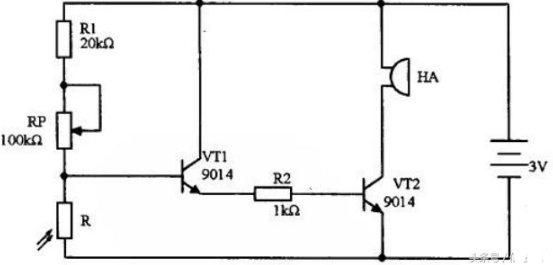

在非复位状态下,主持人按下开始键。表决开始。在没有人投票的情况下。时间变为0。表决结束。仿真波形如下图所示。

无人赞成时的模拟结果

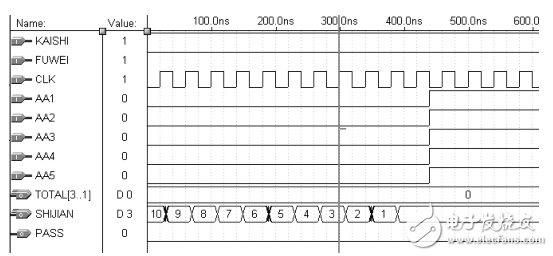

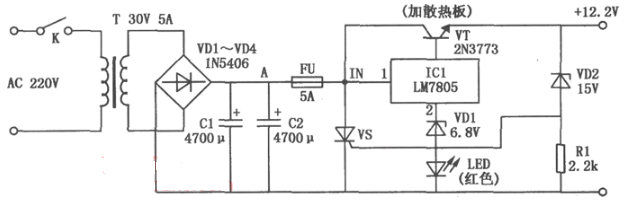

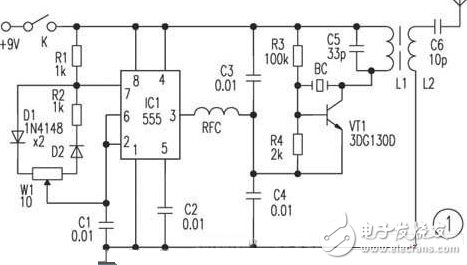

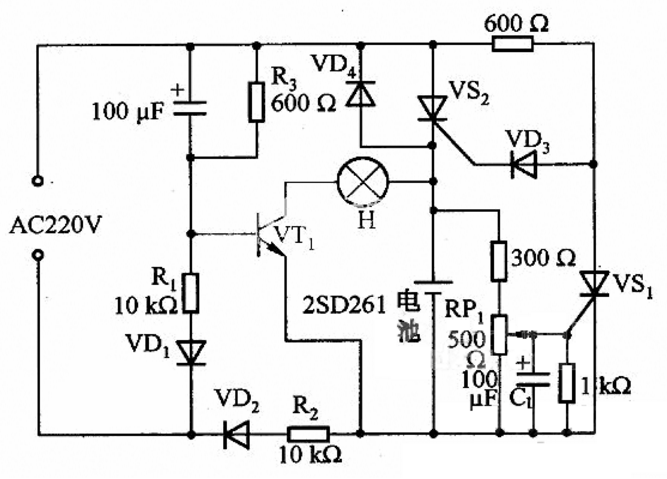

在非复位状态下,主持人按下开始键。表决开始。当超出表决时间时才进行表决,此表决无效。仿真波形如下图所示。

规定时间外的模拟结果

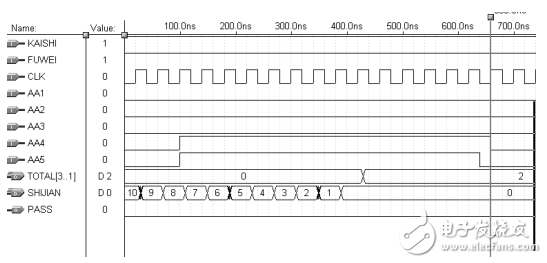

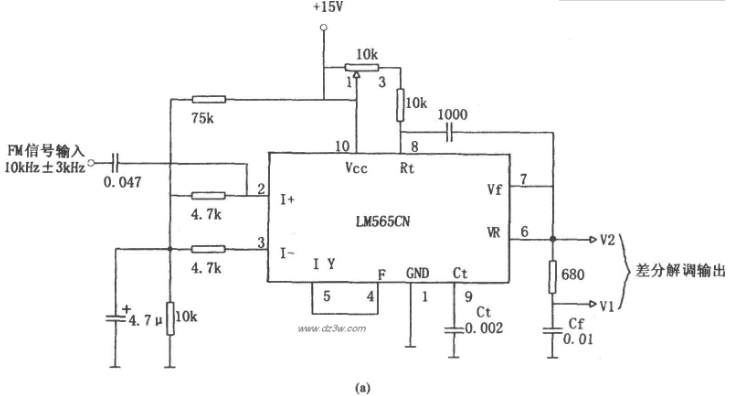

在非复位状态下,主持人按下开始键。表决开始。在规定时间内只有两人赞同。仿真波形如下图所示。

两人赞成时的结果

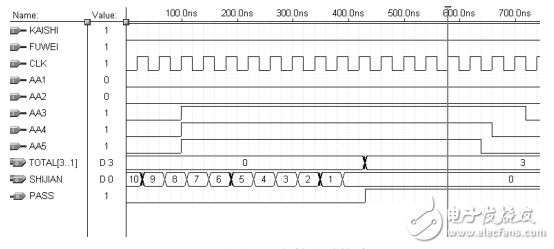

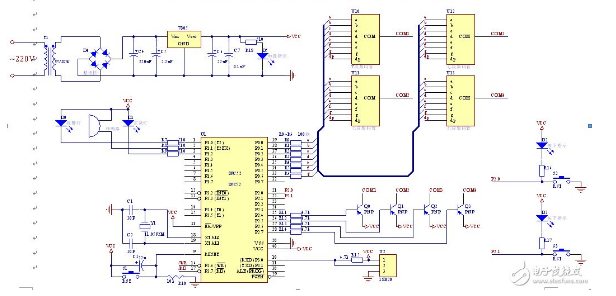

在非复位状态下,主持人按下开始键。表决开始。在规定时间内只有三人赞同。仿真波形如下图所示。

三人赞成时的结果

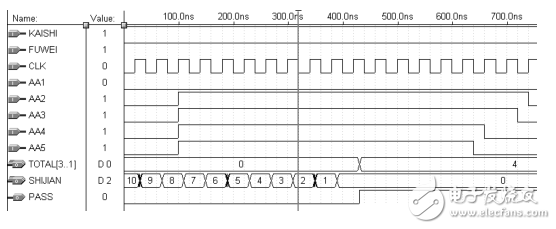

在非复位状态下,主持人按下开始键。表决开始。在规定时间内只有四人赞同。仿真波形如下图所示。

四人赞成时的结果

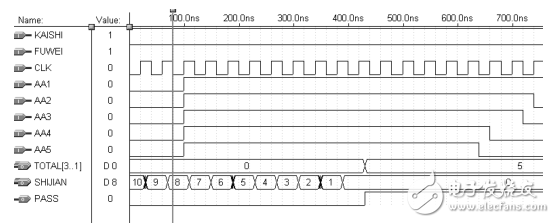

在非复位状态下,主持人按下开始键。表决开始。在规定时间内只有五人赞同。仿真波形如下图所示。

五人赞成时的结果

电子发烧友App

电子发烧友App

评论