74ls160数字钟仿真电路(一)

数字钟是计数电路的一种典型应用,其构成原理框图如下图所示。它主要由三部分组成:

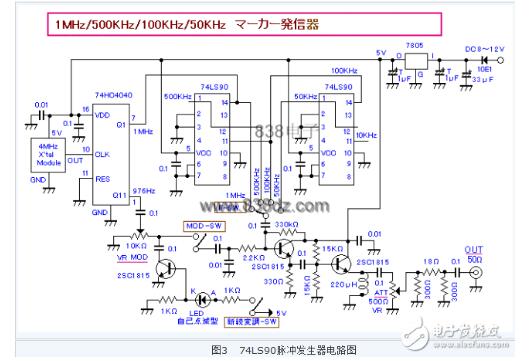

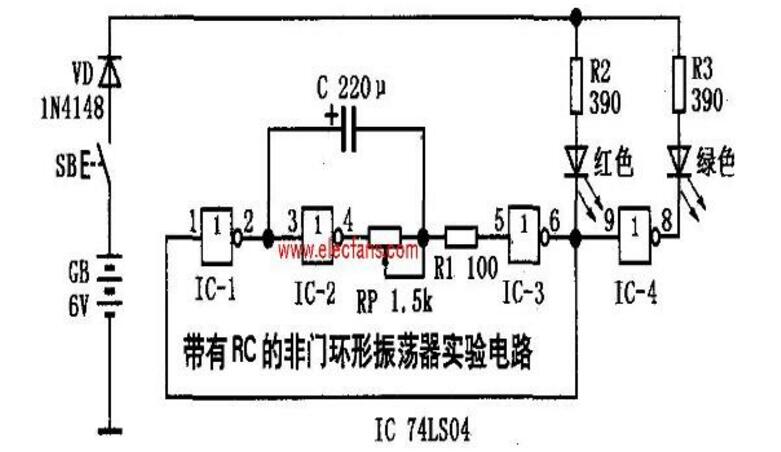

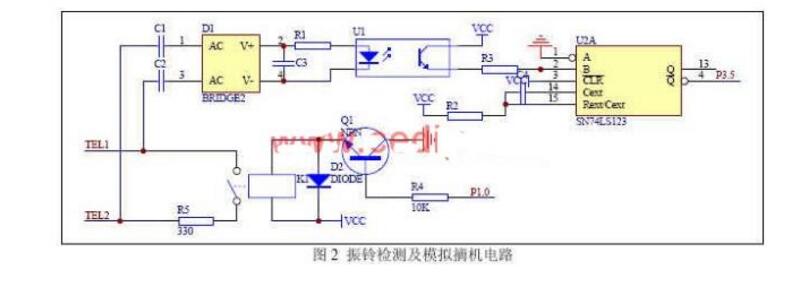

(1)秒脉冲发生电路

它由32768Hz的石英晶体振荡器和若干级分频电路构成,振荡器产生32768Hz的方波,由于使用了晶体,振荡频率准确且稳定,经过216=65536分频后,再经过2倍频,得到秒脉冲信号,该秒脉冲信号经过控制门进入秒计数器进行计数。

(2)时间校准电路

时间调整由3个开关AN1、AN2、AN3以及3个R-S触发器构成。当3个开关都拨到右边时,R-S触发器的输出Q1、Q2、Q3都为1,因此控制门的3个右边门开启,秒、分、时脉冲可以正常进入相应计数器进行计数。当某开关拨到左边时,R-S触发器翻转,例如当“秒调整”开关拨到左边,Q1-0、,控制门的右门关、左门开,秒脉冲不能通过,而0.5s的脉冲信号却可以进入秒计数器实现“秒调整”。分、时的调校原理与此相同,使用R—S触发器的目的是为了消除开关抖动产生的影响。

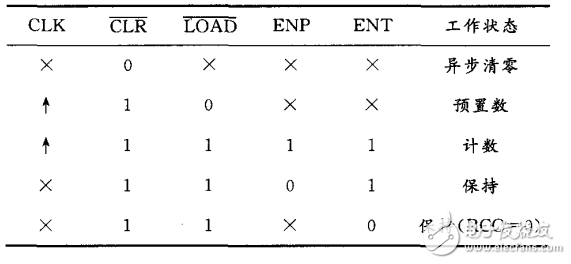

(3)时、分、秒计数电路

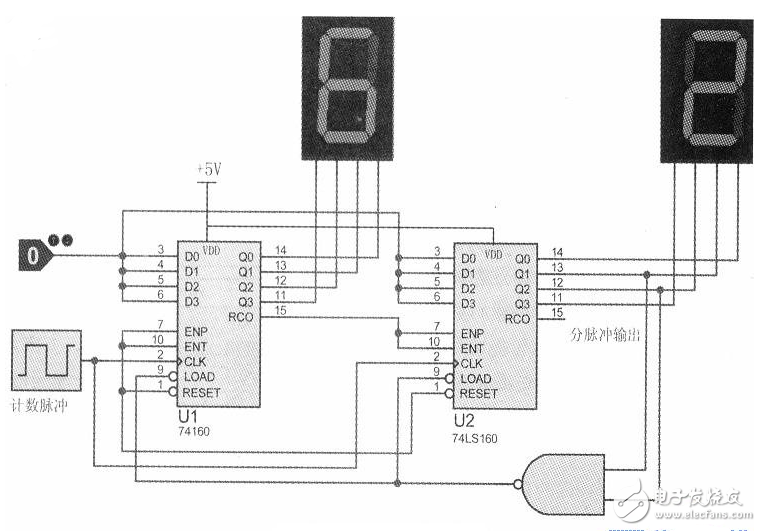

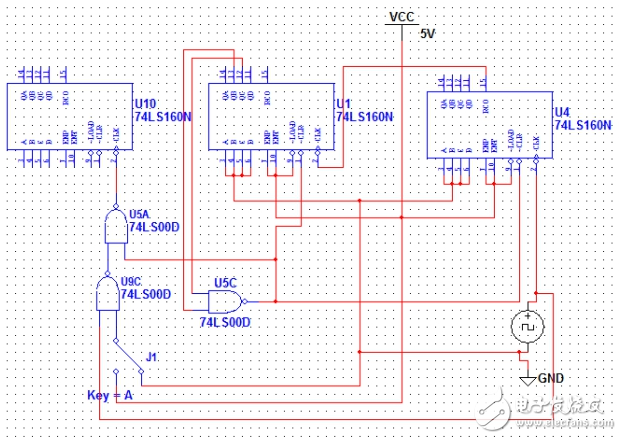

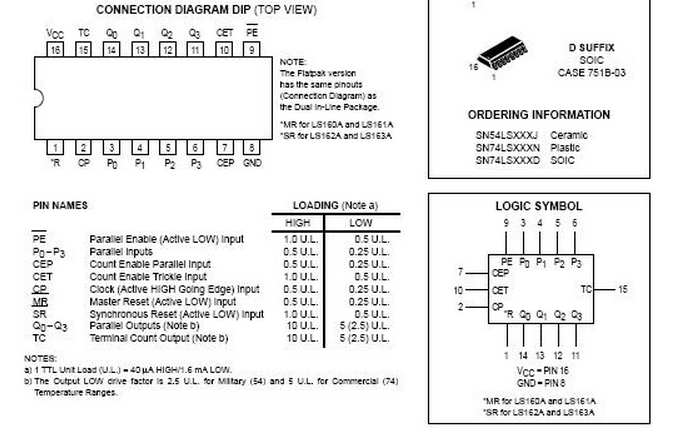

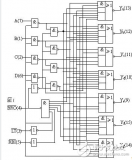

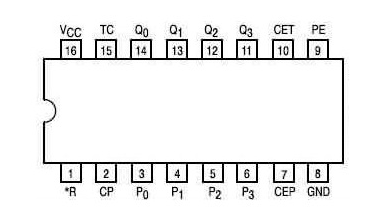

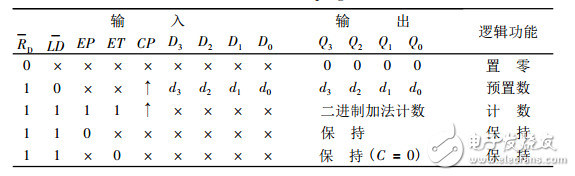

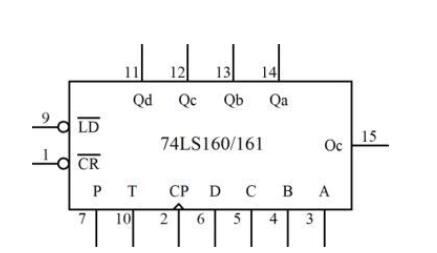

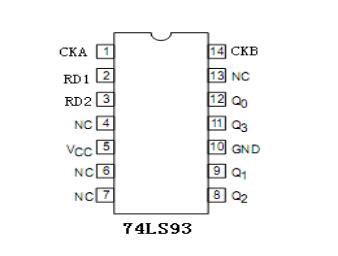

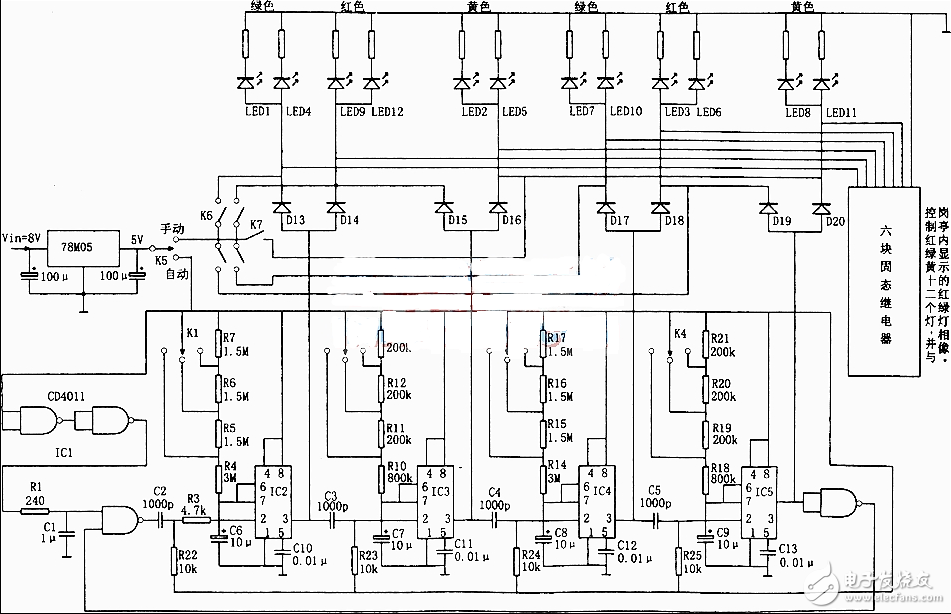

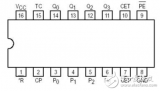

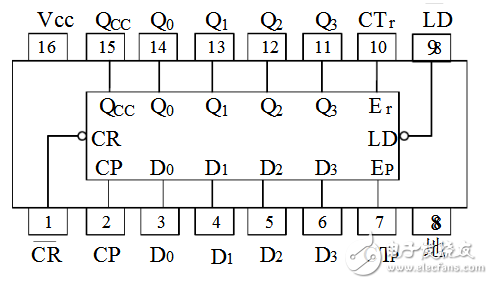

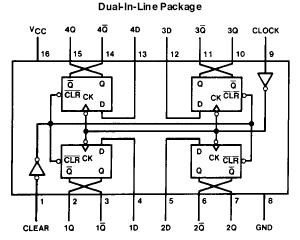

采用两片74LS160按下图所示连接,可以构成作60分频计数,用于数字钟中的秒计数器。

标准秒脉冲经过控制门进入秒计数器,并显示其计数值,当计数满60时得到一个进位“分”脉冲,同时秒计数器自动清零。“分”脉冲经控制门送入“分计数器”又作60分频计数,当计数满后得到进位“时”脉冲。“时”脉冲再经控制门送入“时计数器”计数。“分计数器”与“时计数器”的计数、复零和显示原理与“秒计数器”相同,可以自行设计。

74ls160数字钟仿真电路(二)

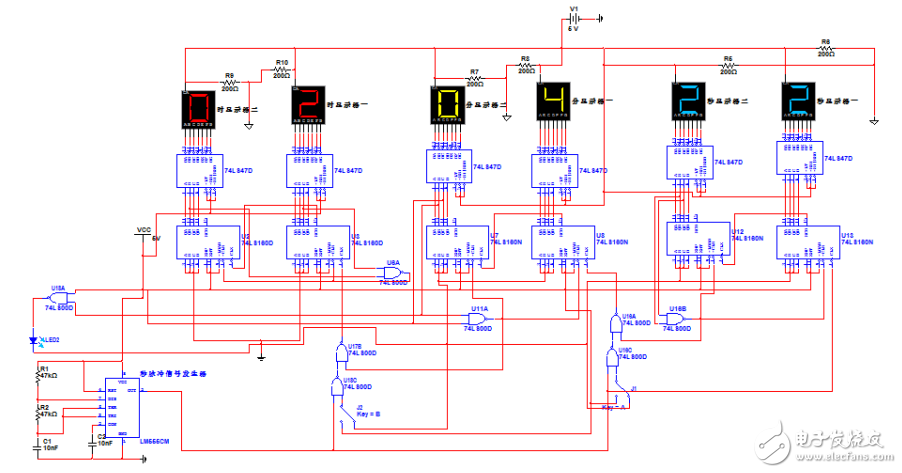

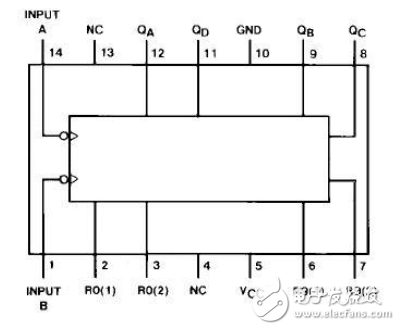

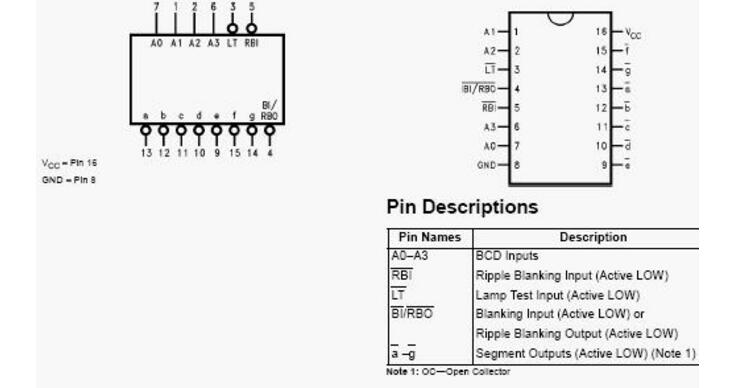

电子钟计时分为小时、分钟和秒,其中小时为二十四进制,分钟和秒均为六十进制,输出可以用数码管显示,所以要求二十四进制为00000000~00100100计数,六十进制为00000000~01100000计数,并且均为8421码编码形式。

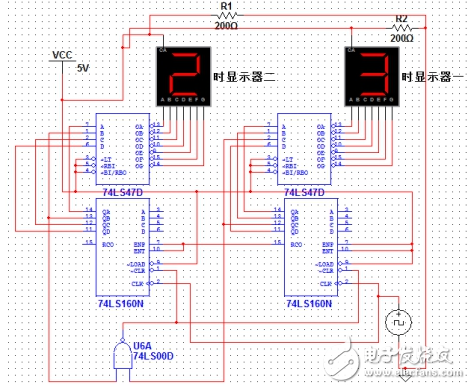

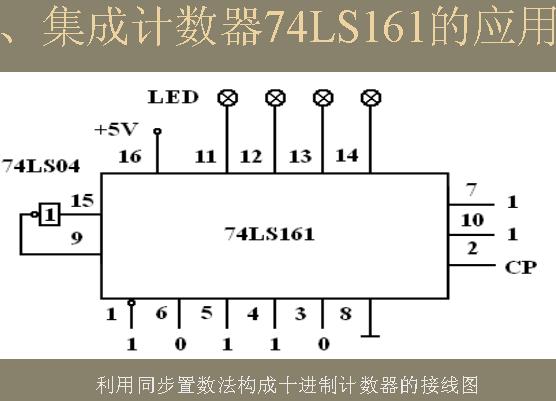

(1)小时计数——二十四进制电路仿真

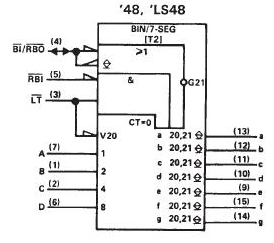

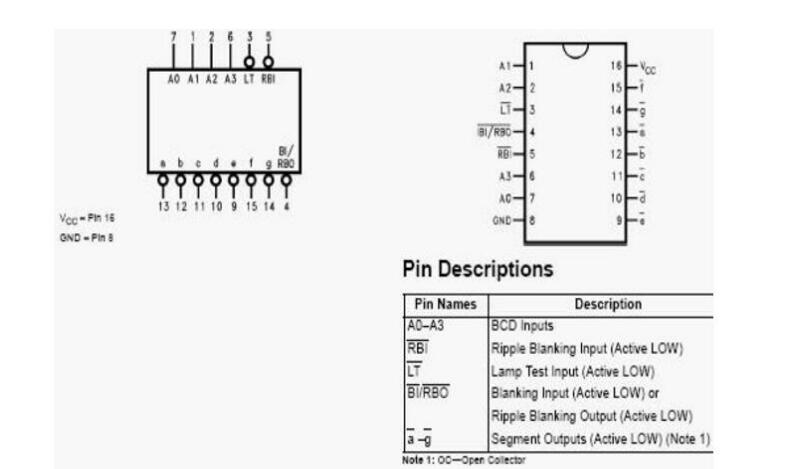

用两片74LS160N(分A片、B片)设计一个一百进制的计数器,在24(00100100)处直接取出所有为1的端口,经过输入与非门74LS00D,再给两个清零端CLR。使用74LS160N异步清零功能完成二十四进制循环,计数范围为0~23。然后用七段显示译码器74LS47D将A、B两片74LS160N的输出译码给LED数码管。仿真电路如图九所示。:

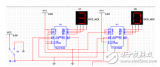

图九24进制——时计数器仿真电路

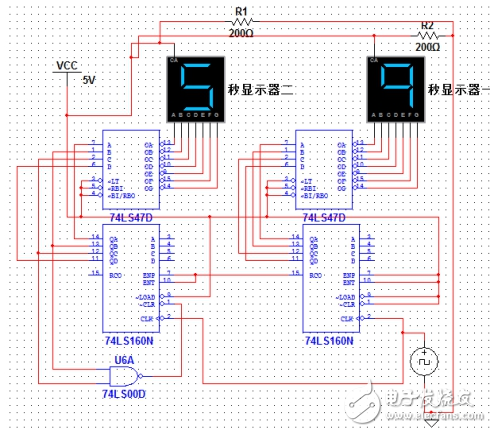

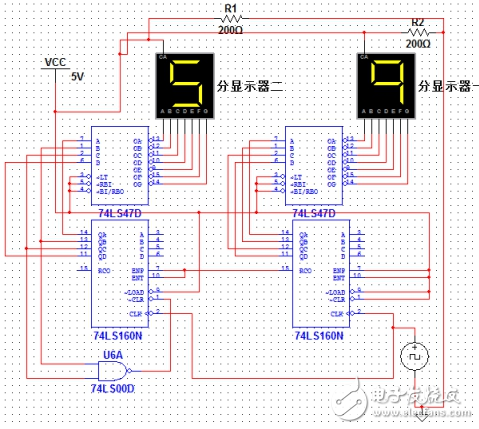

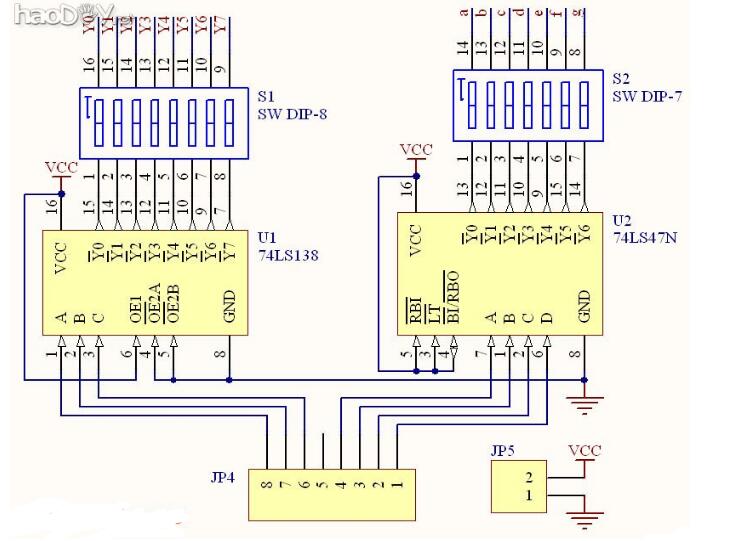

(2)分钟、秒计数——六十进制电路仿真

此电路类似于二十四进制计数器,采用74LS160N设计出一百进制的计数器,在60(01100000)处直接取出所有为1的端口,经过输入与非门74LS00D,再给两个清零端CLR。使用74LS160N异步清零功能完成六十进制循环,计数范围为0~59。然后用七段显示译码器74LS47D将A、B两片74LS160N的输出译码给LED数码管。仿真电路如图所示:

图十60进制——秒计数器仿真电路

图十一60进制——分计数器仿真电路

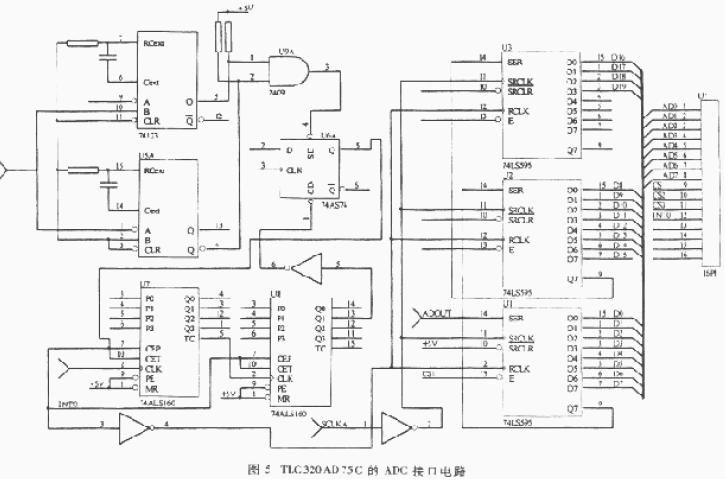

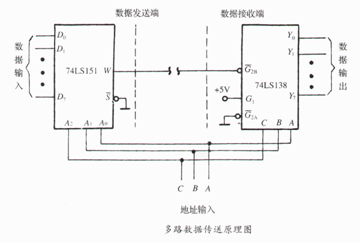

(四)校时校分(秒)电路。

数字钟应具有分校正和时校正功能,因此,应截断分个位和时个位的直接计数通路,并采用正常计时信号与校正信号可以随时切换的电路接入其中。这里利用两个与非门加一个单刀双掷开关来实现校时功能。第一个74LS00D与非门的输入端一端接清零信号,另一端接第二个与非门的输入端,第二个74LS00D的输入端一端接计数脉冲,另一端接一个单刀双掷开关。开关接通的一段接地,另一端接高电平。当开关打到另一端时,时或分的个位就单独开始计数,这样就能实现校时功能。其电路图如图所示:

图十二校分仿真电路

数字时钟仿真电路图如下图所示,在Multisim11.0中进行仿真,可以实现数字时钟的显示功能、校时功能。显示功能中,小时实现的是24进制,分和秒实现的是60进制,通过校时电路能够分别校对时和分。

图十三数字时钟仿真电路

电子发烧友App

电子发烧友App

评论