基于Altera ASI IP核的ASI发送卡实现(2)

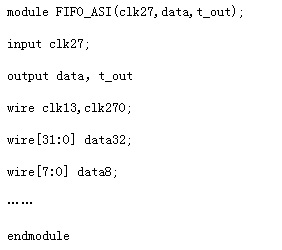

把生成的ASI 核添加的自己的工程中,顶层部分代码如下:

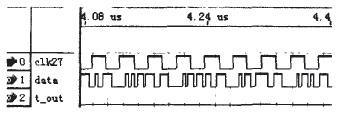

对其进行仿真,波形如下:

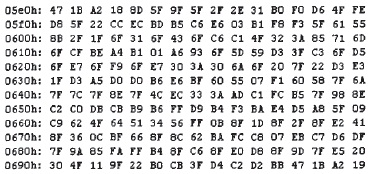

外部接 27M 的时钟,连接到clk27,做为ASI IP 核27M 的输入参考时钟。t_out 为一个 时钟输出信号,对27M 分频,作为指示灯信号,来监测程序是否下载到FPAG 中。在指示灯正常闪烁情况下,表明程序已经下到芯片中,并且能够工作。经过ASI IP 核编码的ASI 数 据由data 输入。在本工程中,通过一电脑不断地发送TS 流给板卡,经过ASI 编码后通过 ASI 接口输出。在接收端,通过一个ASI 接收卡,读出接收的数据,可以看出ASI 工作正常。 在发送TS 流时采突发模式,其读出的数据如下:

在调试阶段,PC 机连续发送相同的MPEG-2 编码的TS 包。在接收到的数据中,可以看到连 续的MPEG-2 编码的TS 包,且与发送的数据相同。其中TS 包的接收采用一块ASI 接收卡作 为接收端,通过USB 接口输入到电脑里,用相应的软件读取数据后显示。

4.应用意义

本文设计的基于Altera 公司的ASI IP 核实现的DVB-ASI 卡,实现了ASI 数据的正确编 码和发送。用FPGA 实现逻辑控制和数据缓存,可以方便的实现系统升级,实现多个ASI 数 据的发送。与用Cypress 公司的CY7B923 实现的ASI 的发送卡相比,本卡更适合批量生产,可以节约成本,提高了市场竟争力,具有很好的市场前景。

本文作者创新观点是用Altera 公司的ASI IP 核代替Cypress 公司的CY7B923 专用ASI 发送芯片,实现ASI 数据的稳定发送。本方案降低了成本,设计灵活,并且方便升级到多路ASI 数据发送。

- 第 1 页:基于Altera ASI IP核的ASI发送卡实现(1)

- 第 2 页:ASI 工程及仿真波形#

本文导航

非常好我支持^.^

(0) 0%

不好我反对

(0) 0%

相关阅读:

- [新品快讯] Altera、Apical和AltaSens联合发布业界首款HD宽动态范 2011-04-07

- [嵌入式设计应用] FreeARM7 IP核的微处理器逻辑扩展与验证 2011-04-06

- [电子常识] ASIC和FPGA的优势与劣势 2011-03-31

- [新品快讯] Altera发布光纤互连可编程器件 2011-03-31

- [电子技术] 赛灵思可能领先于Altera进入28纳米节点 2011-03-21

- [厂商新闻] Altera有机会2012年超越Xilinx成FPGA龙头 2011-03-14

- [新品快讯] ASIX亚信电子推出多款嵌入式有线/无线局域网路芯 2011-03-09

- [新品快讯] Altera业界首款集成增强前向纠错(EFEC) IP内核 2011-03-09

( 发表人:发烧友 )