对于设计人员而言,根据应用的效能、电源、记忆体及介面等需求,寻找特定的嵌入式处理器,不是件容易的事,即便是相似的系统也存在显着的差异。儘管ARM处理器提供十多种选择,系统设计人员仍然很难找到完美搭配的解决方案。

本文将重点介绍各种标準介面,并说明不同嵌入式晶片厂商的差异。瞭解基本介面有助于设计人员优先考量,哪些介面应该整合于晶片。虽然标準介面具有很高的使用价值,但为提供额外的单晶片资源,也需要可客製化的单晶片介面,本文将介绍此两种周边区块。

通用序列匯流排(USB)介面最初的开发目的,是用以连接个人电脑与周边。随着时间推移,已经成为工业与基础架构应用的常用介面。键盘、滑鼠及示波器等人机介面设备(HID),通常採用USB介面,这表示必须获得系统嵌入式处理器的支援。实现此一目标的最有效方法,是採用单晶片周边。

除了HID之外,工业与基础架构应用也可使用另外两种装置类别。USB通讯装置类(CDC)不但适用于数据机与传真机,也透过提供用于乙太网路封包传输的介面,来支援简单的网路功能。同样地,USB大量储存装置(MSD)主要针对硬碟驱动器及其他储存媒体。

USB 2.0规格需要主机进行所有入埠及出埠的传输。此规格也定义叁种基本装置:主机控制器、集线器及周边。

USB 2.0的实体互连,是在各个星型配置使用一个集线器的分层星型拓朴。各个线段都是一个主机与集线器或功能之间的点对点连接,或连接至其他集线器与其他功能的集线器。

USB 2.0系统中,用于装置的定址机制,可供单一主机连接多达127个装置,可以是集线器或周边的任何组合。复合或组合装置可以是选自于其中两个或两个以上的装置。

虽然USB 2.0很可能是工业和许多基础架构应用的首选,但周边装置在不使用主机的情况下相互通讯时,仍需要部署USB On-the-Go(OTG)。为了实作点对点通讯,USB OTG 引入一种新的装置,这种装置包含使两个周边共享资料的有限主机功能。

OTG 补充定义主机协商通讯协定(HNP)的新交握方式(handshake)。使用HNP,能够预设周边进行连接的装置,并请求成为主机,为现有USB 2.0主机装置範例提供点对点通讯。另外也定义阶段作业要求通讯协定(SRP)。

USB标準的普及与稳定的状态,嵌入式处理器厂商皆针对特定USB功能提供软体程式库,大幅缩短开发时间。系统设计人员不需要自行撰写程式码,只需要执行函式唿叫 (function call)即可进行介面操作。

这些程式库需通过认证,证明已通过USB设计论坛USB装置及嵌入式主机规範测试。德州仪器(TI)等多家厂商,皆为自家嵌入式处理器提供广泛的USB程式库。

2007年,高速USB推广团队成立,这种USB类型不仅向下相容以前的USB标準,而且资料速率比USB 2.0快10倍。USB 3.0採用新的讯号处理机制,并透过保留USB 2.0双线式介面,达到向下相容的效果。

EMAC

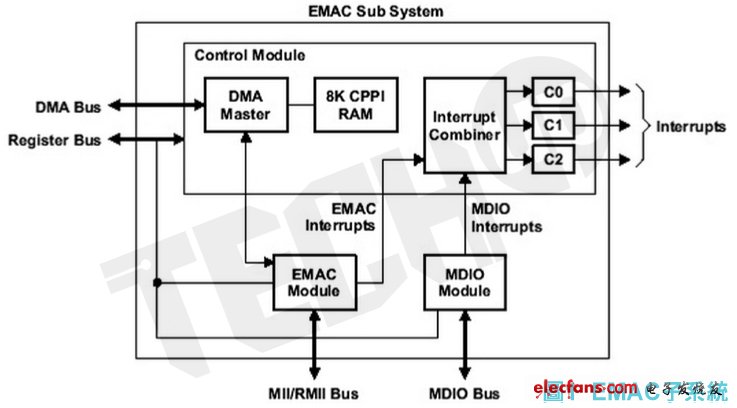

符合IEEE 802.3乙太网路标準的介面,一般会被误认为乙太网路媒体存取控制器(EMAC),但完整的EMAC子系统介面实际上包括叁个区块,这叁个区块可能已整合或未整合于晶片:实体层介面(PHY)、2.乙太网路MAC,这可实作通讯协定的EMAC层、3.一般称为MAC控制模组的自订介面。

EMAC模组可控制从系统到PHY的封包资料流。MDIO模组可执行PHY的配置以及状态监控。这两个模组均可透过MAC控制模组存取系统核心,并且优化资料流。在TI嵌入式处理器等完全整合式解决方案中,自订介面被视为EMAC/MDIO周边不可或缺的组成部分。

完整的EMAC子系统如图1所示。

EMAC控制模组不仅可控制装置中断,也整合一个8K位元组内部随机存取记忆体(RAM),用以存留EMAC缓衝区描述元。MDIO模组採用802.3序列管理介面,来检视和控制多达32个共用双线式匯流排连接至装置的乙太网路PHY。

主机软体使用MDIO模组,来配置连接至EMAC的各个PHY的自动协商参数、撷取协商结果,并在EMAC模组中配置所需的参数,以进行正确的操作。此模组可使得MDIO介面达到几乎透明的操作,不需要核心处理器的维护。

EMAC模组可在网路与处理器之间提供高效率的介面。EMAC模组通常可提供10Base-T(10Mbps)与100BaseTX(100Mbps)、半双工与全双工模式,以及硬体流控制与服务品质(QoS)支援。部份处理器现在也支援高达1000Mbps资料速率的GB EMAC容量。

由于乙太网路受到广泛运用,嵌入式处理器一般都在单晶片整合一个或多个EMAC介面。不同的厂商在实作上述完整的EMAC子系统时,採用的方法各有不同。实作乙太网路介面时,所需软体支援与程式库的品质和範围,是选择嵌入式处理器厂商必须考量的另一个问题。

路由器或交换机等应用,所需的EMAC有时不止一个。这些应用能够透过多个EMAC进行同步通讯,同时与多个装置通讯。

序列ATA(SATA)可将主机匯流排转接器,与硬碟机与光碟机等大量储存装置连接。这个规格已经几乎取代之前的平行ATA(PATA)。PATA需要长度不超过18英吋的40/80线平行缆线。PATA的最大资料传输率为133MBps,而SATA序列资料格式,则使用两个差动支援连接资料储存装置的介面,线路速率为1.5Gbps(SATA版本1)、3.0Gbps(SATA版本2)与6.0Gbps(SATA版本3)。SATA 1和SATA 2现已问世,SATA 3将在不久的将来推出。

SATA控制器需要的缆线较细,而且长达3英呎。细缆线的灵活度较高,一方面可达到更简便的佈线,另一方面更有利于大量储存装置机壳内部的空气流通。

序列连结可达到高效能的部份塬因,是採用进阶系统记忆体结构,来储存高速序列资料。这种进阶主机控制器介面(AHCI)记忆体结构,可为控制、状态及命令清单资料表提供通用区域。命令清单的每笔记录均包含SATA装置程式设计的资讯,以及在系统记忆体与装置之间传输资料的描述符表(discriptor table)。

大多数SATA控制器均支援热抽换(hot swapping),也採用连接埠倍增器(port multiplier),来增加可连接至单一HBA连接埠的装置数量。SATA标準支援许多功能,但少有SATA控制器支援所有功能。较为常见功能包括:

• 支援AHCI控制器规格1.1版

• 整合SERDES PHY

• 整合接收与传输资料缓衝区

• 支援SATA电源管理功能

• 各连接埠内部?DMA引擎

• 多达32笔记录的硬体辅助塬生命令伫列(NCQ)

• 32位元定址

• 支援连接埠倍增器

• 支援活动LED

• 机械控制开关

由于SATA能够储存高达兆位元(terabyte)範围的大量资料,因此应用相当广泛,其中包括小笔电、笔记型电脑、桌上型电脑、多媒体装置及可携式资料终端等。此外,SATA也可用于需要感测器或系统监控器储存大量资料,以供后续分析的工业应用。

DDR2/行动DDR

DDR2是双倍资料速率(DDR)SDRAM规格的后继标準,这两个标準并不相容。DDR2在匯流排时脉讯号的上升与下降边缘传输资料,并以更高的匯流排速度运作,再进行各个内部时脉週期四次的资料传输。

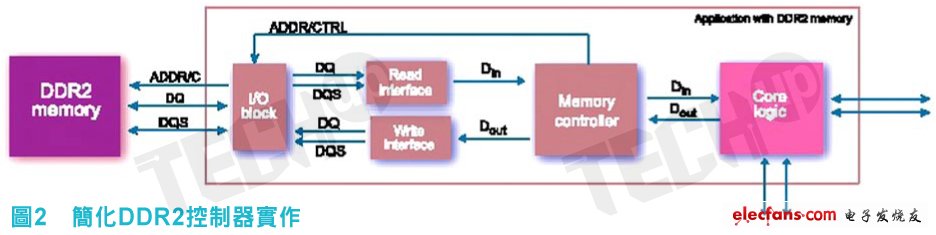

简化型DDR2控制器包括以下设计区块:

• 记忆体控制

• 读取介面

• 写入介面

• I/O区块

这些区块及其与DDR2记忆体晶片和核心逻辑的关係如图2所示。

记忆体控制区块从记忆体存取应用特定核心逻辑,或从应用特定核心逻辑存取记忆体。读取实体区块负责处理在各个读取週期中,撷取资料的外部讯号时序,而写入实体区块,则使用适当的外部讯号时序来管理时脉与资料的发出。

位元组宽双向资料回应(DQS)随资料(DQ)透过对外传输,用以进行撷取。DQS在读取记忆体时,由控制器透过边缘对齐的方式传输,在写入记忆体时,则採取中央对齐的方式。单晶片延迟锁相迴路(DLL),用以锁定DQS及对应的DQ。可在电压及温度发生变化时确保能够相互追踪。

DDR2 SRAM具有差动时脉输入,可降低时脉输入负载週期变化所造成的影响。DDR2 SRAM也支援资料遮罩讯号(data mask signal),可在各个写入週期中为资料位元加入遮罩。

行动DDR(MDDR)也称低功耗双倍资料传输率记忆体(LPDDR),传统记忆体运作电压为2.5V或3.3V,而其运作电压为1.8V,通常用于可携式电子产品。行动DDR记忆体也支援传统DDR2记忆体不具备的低功耗状态。与所有DDR记忆体一样,双倍资料传输率是透过装置时脉上下边缘同时传输资料而达成。

uPP

由于单晶片周边的数量受成本或其他限制条件约束,系统设计人员通常寻求将资料传入与传出晶片的新方法。其中一种是利用未使用的视讯连接埠资源,高速收发非视讯资料。这种方法的其中一个缺点是资料必须转为视讯格式(video frame),在运作中需要部份处理器MIPS的支援,而在设计週期中则需要佔用宝贵的程式设计时间。

其他的方法存在类似的困难,而且大多数标準单晶片资料介面都是序列连接埠,无法执行高速传输。

因此,许多系统设计人员认识到,将不符合特定介面标準但能够以多种方式配置的弹性高速周边专用于资料传输,可达到显着的优势。如果系统处理器必须与高速DAC、ADC、DSP及FPGA连接而达到250MBps的高速资料传输,则此类知识就相当有助益。

这种周边的基本架构很简单,具有许多个别平行匯流排的通道,经过配置可容纳超过一个字元长度(word length)以上。其中也有内部DMA区块,其运作不需要佔用核心的 MIPS。单倍或双倍资料速率以及多种资料封包格式也适用。

TI各种嵌入式处理器均提供通用平行连接埠(uPP),包括Sitara ARM9 AM1808与AM1806微处理器(MPU),以及包含TMS320C674x核心与ARM9核心的OMAP-L138处理器。与SPI及UART等序列周边不同,uPP可为设计人员提供平行资料匯流排的优势,各通道资料宽度为8位元及16位元。

uPP在以75MHz的最高时脉速率运作时,能以远远高于序列连接埠周边的速度传输资料。例如,以75MHz速率运作的单一16位元uPP通道,比以50MHz速率运作的SPI周边快24倍。图3显示简化的配置图。

uPP最重要的功能包括:

?具有个别资料匯流排的两个独立通道:通道可同时以相同或相反方向运作

?I/O速度高达75MHz,各通道资料宽度为8至16位元

?内部DMA-可释放CPU EDMA

?具有极少控制接脚的简单通讯协定(可配置:各通道2至4个)

?单倍及双倍资料速率(使用时脉讯号的单边或两边):双倍资料速率需要37.5MHz的最高时脉速率

?支援9至15位元资料宽度的多种资料封包格式

?资料交错模式(限单通道)

uPP与另一种专用于可配置资料处理的TI周边「主机连接埠介面」(HPI)有某些相似处。HPI是一种可供外部主机直接存取处理器内部记忆体的平行介面。然而,不同于HPI,uPP不允许外部装置直接存取记忆体,而需要装置软体对I/O传输进行伫列。最大的差异在于uPP比HPI更快速,而且通讯协定也更简单。

uPP主要用于FPGA或DSP等需要晶片外即时处理的应用,能够为医疗领域等立即需要资料的市场带来极大的优势。透过uPP,决策处理器能够运用最新资讯做出结论。

PRU

可程式即时单元(PRU)是一种小型32位元处理引擎,可为单晶片即时处理提供更多的资源。PRU专门用于AM1x MPU与OMPAP-L138解决方案中的TI嵌入式处理器,能为系统设计人员提供具有高弹性的额外措施,可降低元件成本。

PRU的四匯流排架构,随着资料传输同步提取和执行指令。此外也提供输入暂存器,让外部状态资讯反映在内部处理器的状态暂存器内。

PRU设计的其中一个重要目的,就是儘可能达到弹性,以便执行各种功能。PRU的高弹性有助于开发人员在终端产品(无论是触控萤幕、整合式显示器或储存功能)中整合更多的介面,进一步扩展产品功能或其本身专属介面的功能。此目标主要是透过提供包括所有系统记忆体、I/O及中断在内的PRU全面系统能见度而达成。

虽然PRU能够全面存取系统资源,但内部资源相对而言属于中等程度,PRU具有4KB的指令记忆体和512位元组的资料记忆体,具有本身的GPIO,延迟仅为数奈秒(nanosecond)。

PRU可透过使用简单组合语言程式码的程式设计来实作自订逻辑。此指令集分为四大类:

?将资料移入或移出处理器内部暂存器

?执行演算运算

?执行逻辑运算

?控制程序流程

在工业应用中,通常将PRU配置为I/O区块,用以补足处理器未提供的I/O。例如,在需要UART区块组合的可携式资料终端中,以连接GSM、GPS与Bluetooth、键盘、印表机、LED排灯及RS232连接埠。虽然此处理器系列中的最佳选择仅整合叁个UART,不过PRU可提供更多的UART介面,充分满足不断发展的终端装置对于处理各种功能的需求。

除了补足I/O之外,PRU经过程式设计之后也可执行各种控制、监控或其他单晶片未提供的功能。对于本身的控制需求与标準处理器配置的控制需求不相同的应用而言,如此的弹性特别有助益。

ARM子系统与周边整合

在评估ARM处理器的周边介面时,了解周边与ARM子系统整合方式相当重要。

ARM处理器适合复杂多工的一般用途控制,不仅为大型程式提供记忆体空间,而且也具有良好的环境切换功能,这适合用于运作即时作业系统(RTOS)及精密的高阶作业系统。ARM负责系统配置与控制,包括周边配置与控制、时脉控制、记忆体初始化、中断处理及电源管理等。ARM子系统包含ARM处理器,以及ARM处理器,进行整体处理器系统主控制器功能所需的其他元件。

一般ARM子系统包括下列元件组合:

?ARM核心(例如:ARM926EJ-S或ARM Cortex-A8)-协同处理器15(CP15)、MMU、写入缓衝器、指令快取、资料快取、Java加速器、Neon单一指令多重资料(SIMD)协同处理器、向量浮点协同处理器(VFP)

?ARM内部记忆体-RAM、ROM(ARM开机载入器)

?匯流排仲裁器(bus arbiter)-用以存取内部记忆体的匯流排仲裁器、用以存取系统及周边控制暂存器的匯流排仲裁器、用以存取外部记忆体的匯流排仲裁器

?除错、追踪及模拟模组-JTAG、ICECrusher、嵌入式追踪巨集单元(ETM)

?系统控制周边-ARM中断控制模组、PLL(锁相迴路)及时脉控制模组、电源管理模组、系统控制模组

图 5 ARM 子系统配置图

对于 USB、EMAC、SATA、uPP 及 PRU 等周边而言,ARM 子系统可存取周边的控制与配置暂存器、时脉及电源管理控制。

结论

虽然标準介面在设计系统的过程中发挥重要的作用,能够达到互通性与低成本,并减少设计时间,但是对于需要达到产品差异化的设计团队而言,实用性较为有限。设计人员也寻求晶片厂商提供各种多重组合的标準介面。对于晶片厂商而言,有助于有效实作介面的高品质软体程式库,是达到差异化的重要因素。提供更高的弹性也相当有助益,只要透过 TI PRU 与 uPP 等可配置介面即可达成。系统设计人员利用工具套件中的这些选项,即可发挥创意,并且维持元件的低成本。

电子发烧友App

电子发烧友App

评论