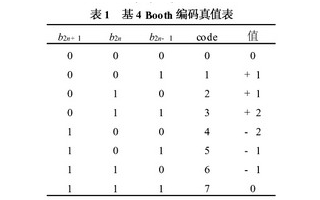

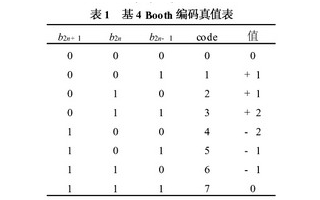

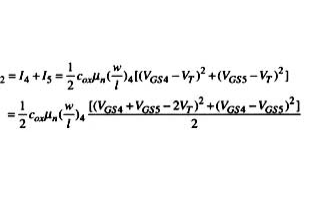

阵列乘法器的设计, 采用了改进的Booth 编码, 和Wallace树结构, 在减少部分积的同时, 使系统具有高速度, 低功耗的特点, 并且结构规则, 易于VLSI的实现。

2020-11-06 12:47:00 1752

1752

本帖最后由 eehome 于 2013-1-5 10:11 编辑

18_18并行流水乘法器芯片设计

2012-08-10 18:06:11

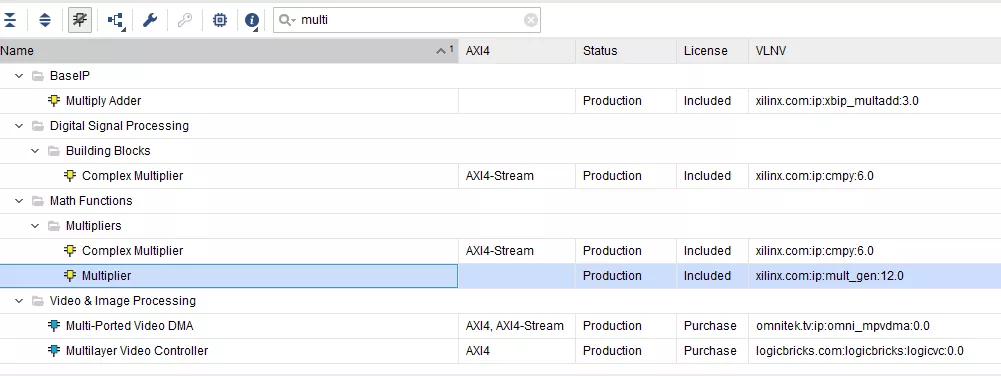

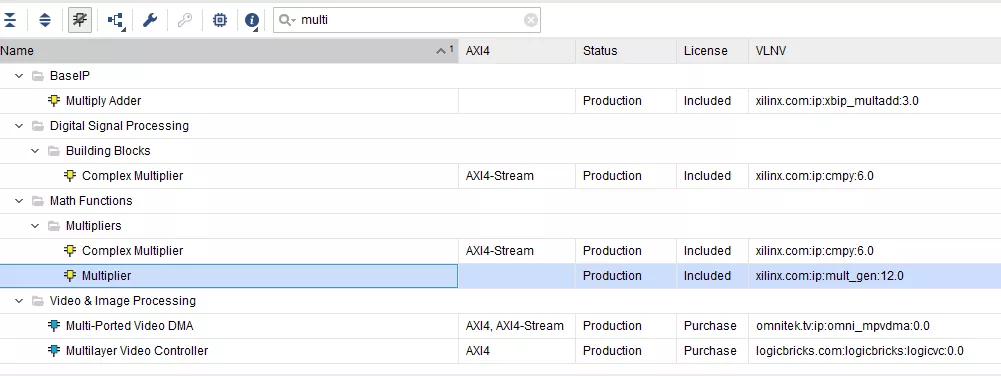

刚接触学习FPGA,懂得verilog HDL的基础语法,有一块带XILINX的ZYNQ xc7z020的开发板,开发软件用的是vivado;现在要设计一个16位的乘法器,功能已经实现。但需要考查

2018-02-25 16:03:46

的乘法器,功能已经实现。但需要考查性能指标:功耗、速度、吞吐量、覆盖率。但对这几个概念没有太大的了解①请问对于一个乘法器而言这几个方面指的是什么?②在Project Summary中有一个

2018-02-25 21:12:01

`流水线设计前言:本文从四部分对流水线设计进行分析,具体如下:第一部分什么是流水线第二部分什么时候用流水线设计第三部分使用流水线的优缺点第四部分流水线加法器举例第一 什么是流水线流水线设计就是将组合

2020-10-26 14:38:12

fpga中定点乘法器设计(中文)目录声明 ………………………………………………………………………………………… 10、 约定

2012-08-12 11:59:01

怎样做一个乘法器电路

2013-01-09 18:26:48

请问TI有没有类似AD835这样的乘法器??

2018-06-21 02:36:06

已经查阅了A53的手册没有找到相关的答案,自己有刚刚接触这方面,老大给的任务,希望有大佬帮忙指点一下,或是有相关资料经验也可以。ARM cortex-A53相关性能:是否支持硬件预取、整型流水线的个数、乘法器的个数及时钟周期、除法器的个数及时钟周期、整形流水线中乘法器的个数。

2020-01-16 20:32:32

什么是ARM流水线流水线(Pipelining)是 RISC(精简指令集)处理器用来执行指令的机制,通过获取指令来加速执行,而其他指令同时被解码和执行。这反过来又允许内存系统和处理器连续工作。每个

2022-04-11 17:23:19

Altera的FPGA内置的乘法器为何是18位的?

2023-10-18 07:01:41

可以解释为什么在使用专用乘法器时提高流水线等级不会提高速度。b)最好的解决方案是让System Generator自己选择阶段数量。这里的问题是我看不到插入了多少个阶段。因此,我无法在适当的时间内延迟

2019-06-13 15:56:35

Verilog中用*实现乘法和用乘法器ip核实现乘法综合结果有哪些不同?

2016-03-18 09:35:13

了触发器,数据的采集需要发生在时钟上升沿),总处理数据的吞吐量增加了。流水线改造实例接下来我们用一个很简单的例子来说明如何对电路进行简单的流水线改造,假设我们现在要实现(4*a+6*b)-10,那么我们

2019-12-05 11:53:37

表明使用了4个MULT18X18SIO中的1个。一旦在FPGA上实现了设计,我就发现了乘法器实际上只使用8x8bit乘法。经过一番阅读后我发现你可以直接控制了MULT18X18SIO具有以下

2019-05-29 06:12:17

如何理解fpga流水线

2015-08-15 11:43:23

前段时间发了个关于fpga的PID实现的帖子,有个人说“整个算法过程说直白点就是公式的硬件实现,用到了altera提供的IP核,整个的设计要注意的时钟的选取,流水线的应用”,本人水平有限,想请教一下其中时钟的选取和流水线的设计应该怎么去做,需要注意些什么,请大家指导一下。

2015-01-11 10:56:59

本帖最后由 eehome 于 2013-1-5 10:07 编辑

fpga中定点乘法器设计(中文)

2012-08-24 00:55:37

/devkits/HW-SPAR3A-SK-UNI-G.htm它有两个模拟输入和fpga,有20个乘法器但是我想要更多的输入和更多的乘法器块,是否能够满足这些功能的任何板?

2019-08-23 07:03:09

在数字化飞速发展的今天,人们对微处理器的性能要求也越来越高。作为衡量微处理器性能的主要标准,主频和乘法器运行一次乘法的周期息息相关。因此,为了进一步提高微处理器性能,开发高速高精度的乘法器势在必行

2019-09-03 08:31:04

现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作(在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上),所以,浮点加法器是现代信号

2019-08-15 08:00:45

本文介绍了32 位浮点阵列乘法器的设计, 采用了改进的Booth 编码, 和Wallace树结构, 在减少部分积的同时, 使系统具有高速度, 低功耗的特点, 并且结构规则, 易于VLSI的实现。

2021-05-08 07:44:31

在数字信号处理中,乘法器是整个硬件电路时序的关键路径。速度和面积的优化是乘法器设计过程的两个主要考虑因素。由于现代可编程逻辑芯片FPGA的集成度越来越高,及其相对于ASIC设计难度较低和产品设计

2019-09-03 07:16:34

求助,有没有大神用verilog写过浮点矩阵乘法器的,我写出浮点乘法器和加法器之后就进行不下去了,急求助!!!只有一个积分~~~

2017-09-18 09:22:03

说明:求fpga乘法器,要求快的,不是一个一个的加,而是像乘法竖式一样的,如:10111000111000 *1011111 =10111000111000*1011111

2012-08-16 14:08:36

基于FPGA的64位流水线加法器的设计基本要求: FPGA 可自行选择可实现64位无符号数的加法运算8级流水线深度

2014-12-18 11:00:42

流水线技术是提高系统吞吐率的一项强大的实现技术,并且不需要大量重复设置硬件。20世界60年代早期的一些高端机器中第一次采用了流水线技术。第一个采用指令流水线的机器是IBM7030(又称

2023-03-01 17:52:21

求浮点数乘除计算程序,求用硬件乘法器计算浮点数的程序

2015-11-03 22:32:47

硬件乘法器是怎么实现的

2023-09-22 06:53:57

一,乘法器硬件乘法器是一个通过内部总线与 CPU 相连的 16 位外围模块。MSP430 单片机可以在部改变 CPU 结构和指令的情况下增加功能,这种结构特别适用于对运算速度要求很严格的情况。硬件

2021-12-09 07:05:15

在ARM中,关于 LDR流水线,分支流水线,中断流水线,其和 PC 之间的关系一直没整明白,求大神详解!!!

2019-04-30 07:45:25

请问一下高速流水线浮点加法器的FPGA怎么实现?

2021-05-07 06:44:26

本文讨论了一种可在FPGA 上实现的FFT 结构。该结构采用基于流水线结构和快速并行乘法器的蝶形处理器。乘法器采用改进的Booth 算法,简化了部分积符号扩展,使用Wallace 树结构和4-2

2009-09-11 15:46:40 16

16 本文在设计实现乘法器时,采用了4-2 和5-2 混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占用率;经Xilinx ISE 和Quartus II 两种集成开发环境下的综合仿真测试,与用Verilog

2009-09-17 11:13:21 27

27 FPGA重要设计思想及工程应用之流水线设

流水线设计是高速电路设计中的一 个常用设计手段。如果某个设计的处理流程分为若干步骤,而且整个数据处理 流程分

2010-02-09 11:02:20 52

52 流水线技术在高速数字电路设计中的应用

2010-07-17 16:37:21 6

6 介绍了补码阵列乘法器的Pezaris 算法。为提高运算速度,利用流水线技术进行改进,设计出流水线结构阵列乘法器,使用VHDL语言建模,在Quartus II集成开发环境下进行仿真和功能验证

2010-08-02 16:38:00 0

0 设计了一个基于FPGA的单精度浮点数乘法器.设计中采用改进的带偏移量的冗余Booth3算法和跳跃式Wallace树型结构,并提出对Wallace树产生的2个伪和采用部分相加的方式,提高了乘法器的运

2010-09-29 16:46:56 44

44 什么是流水线技术

流水线技术

2010-02-04 10:21:39 3702

3702 高速流水线浮点加法器的FPGA实现

0 引言现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操

2010-02-04 10:50:23 2042

2042

流水线中的相关培训教程[4]

下面讨论如何利用编译器技术来减少这种必须的暂停,然后论述如何在流水线中实现数据相关检测和定向。

2010-04-13 16:09:15 4272

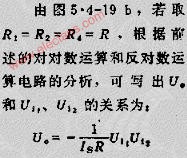

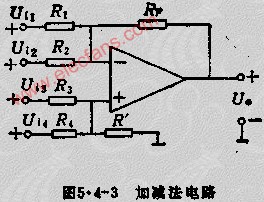

4272 乘法器对数运算电路应用

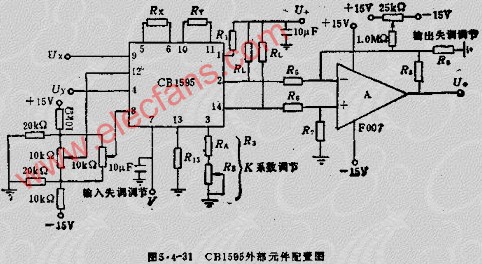

由对数电路实现乘法运算的数学原理是:UO=EXP(INU11+INU12)=U11+U12

图5.4-19示出了满足上式的乘法器的方框

2010-04-24 16:03:19 2273

2273

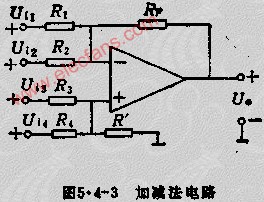

乘法器的基本概念

乘法器是一种完成两个互不相关的模拟信号相乘作用的电子器件。理想乘法器的输出特性方程可由下式表示:

UO

2010-05-18 14:03:59 13355

13355

1/4平方乘法器

这种乘法器是根据数学关系设计而成的,因此称为1/4平方乘法电路,或称1/4平方乘法器。其

2010-05-18 14:08:10 1777

1777

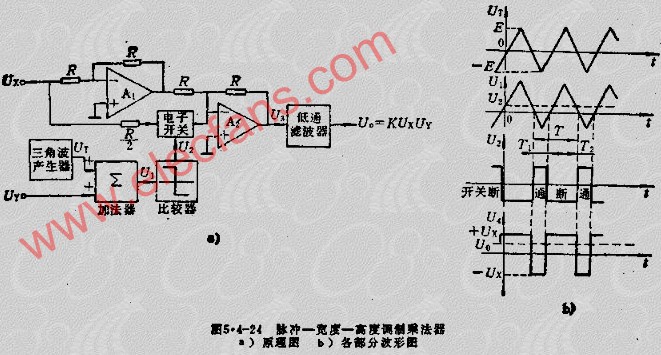

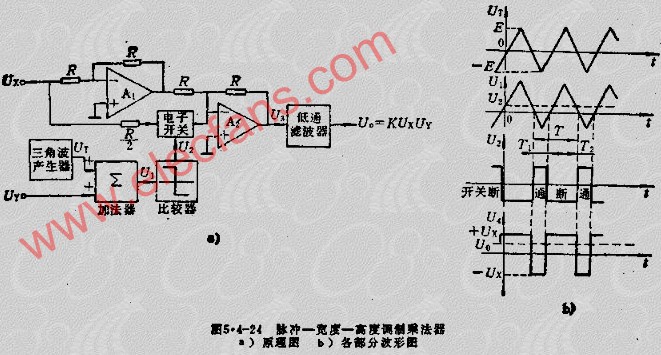

脉冲-宽度-高度调制乘法器

脉冲-宽度-高度调制乘法器双称为时间分割乘法器。这类乘法器电路原理图如图5.4-24A所示。图中,三角波电压UT和模拟输入电压UY

2010-05-18 14:23:53 1782

1782

变跨导乘法器的基本原理

图5.4-25为变跨导乘法器原理图。它利用V1、V2管的跨导GM正比于恒流源电流IO,而IO又受另一个输入电压控制,而实

2010-05-18 14:48:28 2947

2947

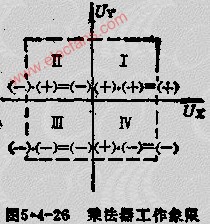

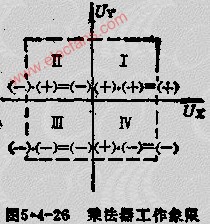

N象限变跨导乘法器

为了克服图5.4-25所示的乘法器的缺点,在基电路的基础上,采用了双重差分放大式结构,设计出如图5.4-27所示的N象限变跨导乘法器。

2010-05-18 15:24:08 1545

1545

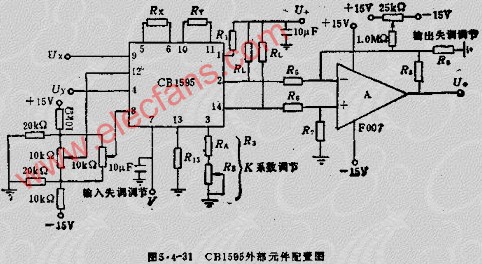

可变跨导乘法器的品种

模拟乘法器就基单片结构的形式来说,基本上分为两大类,即用于处理交流小信号的如图5.4-27所示的基本电路,以及适用于模拟运算

2010-05-18 15:51:40 1736

1736

变跨导乘法器

这种乘法器现在已经成为一种工业上的标准方法,是应用极为广泛的优质乘法器。

2010-05-18 16:00:55 1087

1087 乘法器在通信电路中的应用

普通振幅调制

2010-05-18 17:46:47 1268

1268 实验目的 1、熟悉Xilinx的ISE 软件的使用和设计流程; 2、掌握Modelsim仿真软件的使用方法; 3、用乘法运算符实现一个16*16 乘法器模块; 4、用IP核实现一个16*16 乘法器模块; 5、用例化语

2011-05-20 17:00:14 66

66 AD834具有的800MHz的可用带宽是此前所有 模拟乘法器 所无法相比的。在推出AD834之前,ADI公司已经有了大约20年设计模拟乘法器的历史,也推出过其他的模拟乘法器产品,如:AD734四象限模

2011-07-18 15:33:21 242

242 为了提高快速傅里叶变换( FFT)处理数据的实时性,本文利用现场可编程阵列( FPGA)逻辑资源丰富、运算速度快的特点以及FFT算法的分级特性,实现了高速、高阶FFT的流水线工作方式设计。通

2011-10-01 01:52:51 55

55 为了提高快速傅里叶变换( FFT)处理数据的实时性,本文利用现场可编程阵列( FPGA)逻辑资源丰富、运算速度快的特点以及FFT算法的分级特性,实现了高速、高阶FFT的流水线工作方式设计。通

2011-10-28 17:11:26 32

32 本文着重介绍了一种基于WALLACETREE优化算法的改进型乘法器架构。根据FPGA内部标准独特slice单元,有必要对WALLACE TREE部分单元加以研究优化,从而让在FPGA的乘法器设计中的关键路径时延

2011-11-17 10:50:18 4936

4936

华清远见FPGA代码-FPGA片上硬件乘法器的使用

2016-10-27 18:07:54 10

10 一个自己写的八位数的乘法器

2016-12-01 15:45:23 15

15 高速双域乘法器设计及其应用_郑朝霞

2017-01-07 18:39:17 0

0 流水线状态机20进制,101序列检测,8位加法器流水线的程序

2017-05-24 14:40:47 0

0 模拟乘法器作用及电路

2017-10-23 09:22:40 28

28 乘法器,求模运算部分利用Barrett约减运算,用硬件描述语言进行FPGA设计与实现,避免了除法运算。对于192位的操作数,完成Barrett模乘需要约186个时钟周期,计算速率可以达到269.17 Mb/s。

2017-11-08 15:18:19 32

32 虽然许多有关调制的描述都将其描绘成一种乘法过程,但实际情况更为复杂。 首先,为清晰起见,若信号Acos(t)和未调制的载波cos(t)施加于理想乘法器的两路输入,则我们将得到一个调制器。这是因为两个

2017-11-15 14:45:18 15

15 设计了一种新颖的3232位高速流水线乘法器结构.该结构所采用的新型Radix-16 Booth算法吸取了冗余Booth编码与改进Booth编码的优点,能简单、快速地产生复杂倍数.设计完成的乘法器

2018-03-15 13:34:00 6

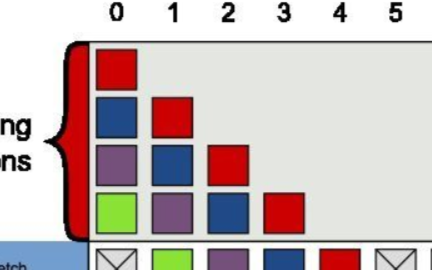

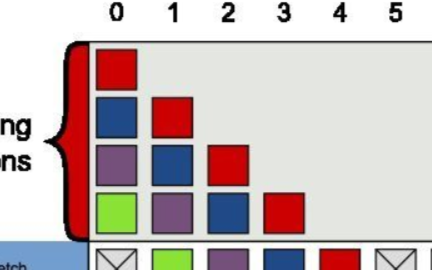

6 颜色表示了不同阶段的可配置性或可编程性:绿色表示该流水线阶段是完全可编程控制的,黄色表示该流水线阶段可以配置但不是可编程的,蓝色表示该流水线阶段是由GPU固定实现的,开发者没有任何控制权。实线表示该shader必须由开发者编程实现,虚线表示该Shader是可选的.

2018-05-04 09:16:00 3613

3613

硬件乘法器是现代计算机中必不可少的一部分,其基础是加法器结构。

2018-05-11 10:52:45 8533

8533 在做项目的过程中,经常遇到乘法计算,乘法器的设计就尤为重要。乘法器决定了最终电路功能能否实现,资源使用量多少以及时序性能优劣等。

2018-07-04 09:41:45 8885

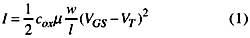

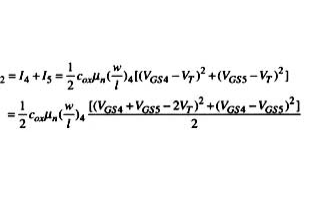

8885 在集成电路系统中,模拟乘法器在信号调制解调、鉴相、频率转换、自动增益控制和功率因数校正控制等许多方面有着非常广泛的应用。实现模拟乘法器的方法有很多,按采用的工艺不同,可以分为三极管乘法器和CMOS乘法器。

2019-05-31 08:20:00 2618

2618

在数字化飞速发展的今天,人们对微处理器的性能要求也越来越高。作为衡量微处理器 性能的主要标准,主频和乘法器运行一次乘法的周期息息相关。因此,为了进一步提高微处理器性能,开发高速高精度的乘法器势在必行。

2018-12-31 07:35:00 2180

2180

第一部分什么是流水线 第二部分什么时候用流水线设计 第三部分使用流水线的优缺点 第四部分流水线加法器举例 一. 什么是流水线 流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器

2018-09-25 17:12:02 4370

4370 本文在设计实现乘法器时,采用了4-2和5-2混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占 用率;经XilinxISE和QuartusII两种集成开发环境下的综合仿真测试

2018-12-19 13:30:25 10461

10461

流水线的工作方式就象工业生产上的装配流水线。在CPU中由5—6个不同功能的电路单元组成一条指令处理流水线,然后将一条X86指令分成5—6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,因此提高CPU的运算速度。

2019-11-29 07:06:00 2251

2251 流水线工作方式可节约工厂生产成本,可一定程度上节约生产工人数量,实现一定程度的自动化生产,前期投入不大,回报 率高。

2019-11-29 07:02:00 1529

1529 乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。

2019-11-28 07:06:00 3062

3062 流水线的平面设计应当保证零件的运输路线最短,生产工人操作方便,辅助服务部门工作便利,最有效地利用生产面积,并考虑流水线安装之间的相互衔接。为满足这些要求,在流水线平面布置时应考虑流水线的形式、流水线安装工作地的排列方法等问题。

2019-11-28 07:07:00 2039

2039 流水线又称为装配线,一种工业上的生产方式,指每一个生产单位只专注处理某一个片段的工作。以提高工作效率及产量;按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。

2019-11-28 07:04:00 3232

3232 作者:猫叔 FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者

2020-09-27 15:12:52 8952

8952

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。乘法器不仅作为

2021-02-18 15:08:01 24395

24395

在集成电路系统中,模拟乘法器在信号调制解调、鉴相、频率转换、自动增益控制和功率因数校正控制等许多方面有着非常广泛的应用。实现模拟乘法器的方法有很多,按采用的工艺不同,可以分为三极管乘法器和CMOS乘法器。

2021-03-23 09:40:19 3930

3930

乘法器,采用近似加法实现部分累加运算,从而减少近似乘法器的资源消耗,同时通过流水线结构增加系统的时钟频率,进而提高数据吞吐率。统计结果表明,与精确乘法器相比,该设计可节省32.2%的查找表资源。在图像处理应用中,

2021-05-19 14:10:44 7

7 的以时序逻辑方式设计的16位乘法器,乘法通过逐向移位加原理来实现,从被乘数的最低位开始,若为1,则乘数左移与上一次和相加;若为0,左移后以全零相加,直至被乘数的最高位。从而实现乘法的移位运算。

2021-06-01 09:43:56 26

26 按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。

2021-07-05 11:12:18 6087

6087

流水线一、定义流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理是针对不同指令而言的,他们可同时为多条指令的不同部分进行工作。• 把一个重复的过程分解为若干个子过程

2021-10-20 20:51:14 6

6 本文解释了流水线及其对 FPGA 的影响,即延迟、吞吐量、工作频率的变化和资源利用率。

2022-05-07 16:51:10 4734

4734

随着3G技术的发展,关于图像、语音、加密等数字信号处理技术随处可见,而且信号处理的实时性也要求越高。实时性即是要求对信号处理的速度要快,而乘法器是数字信号处理中重要的基本运算,在很大程度上影响着系统的性能。人们开始开发高速的乘法器。

2022-07-03 11:14:20 4066

4066 jenkins 有 2 种流水线分为声明式流水线与脚本化流水线,脚本化流水线是 jenkins 旧版本使用的流水线脚本,新版本 Jenkins 推荐使用声明式流水线。文档只介绍声明流水线。

2023-05-17 16:57:31 613

613

正在加载...

电子发烧友App

电子发烧友App

评论