您的位置:电子发烧友网 > 电子技术应用 > 嵌入式技术 > FPGA/ASIC技术 >

PLD设计速成(2)-采用原理图设计三人表决器

2012年05月18日 15:46 来源:本站整理 作者:秩名 我要评论(0)

我们根据三人表决器的直值表,可以通过卡诺图化简可以得到:

L2=SW1SW2 SW1SW3 SW2SW3

L1=_L2

那么我们可以在MAX plusII中用原理图实现上面的三人表决器

下面仅把和VHDL不同的详细写下,相同或基本相同的就一带而过:

(1)打开MAX plusII

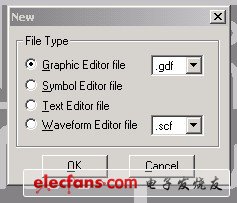

(2)新建一个图形文件:File菜单>new

新建文件时选择Graphic Editor file

点OK

(3)输入设计文件

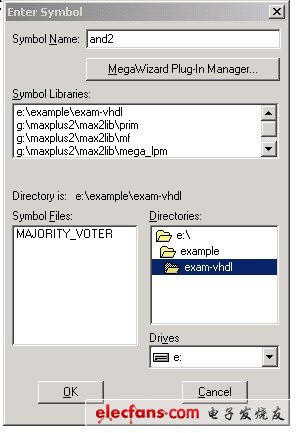

我们现在在图形文件中输入电路,我们这个电路需要AND2、OR3、NOT三个逻辑门电路和输入输出端,你可以

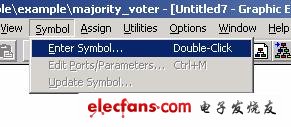

Symbol ->Enter Symbol(或者双击空白处)

弹出窗口:

在Symbol Name中输入and2,点OK

同样可以加入or3、input、output、not

对input、output,鼠标左键双击PIN_NAME,那么PIN_NAME被选中,并且变黑,然后输入你要改的名字,如SW1

把元件拖动到合适位置,将光标放到元件的引线出,可以发现光标变为十字星,此时摁住左键就可以进行连线。

本文导航

- 第 1 页:PLD设计速成(2)-采用原理图设计三人表决器(1)

- 第 2 页:最后的电路

标签: