基于FPGA的可扩展高速FFT处理器的设计与实现

2012年05月25日 10:18 来源:互联网 作者:秩名 我要评论(0)

一、引言

DFT(离散傅里叶变换)作为将信号从时域转换到频域的基本运算,在各种数字信号处理中起着核心作用,其快速算法FFT(快速傅里叶变换)在无线通信、语音识别、图像处理和频谱分析等领域有着广泛的应用。用大规模集成电路FPGA(现场可编程门阵列)来实现FFT算法时,需要重点考虑的不再是算法运算量,而是算法的复杂性、规整性和模块化,因为算法的简单性和规整性将更适合大规模集成,更方便于版图设计,而算法的模块化更有利于FFT处理器的灵活扩展。组合数FFT算法和CORDIC(坐标旋转数字计算机)算法结合起来,在计算长点数、可扩展FFT时具有较大的优越性[1,2]。而面向高速、大容量数据流的FFT的实时处理,可以通过VLSI(超大规模集成电路)器件的并行处理或多级流水线处理等来达到。特别是多级流水线处理的FFT结构使得基于FPGA器件的FFT处理器完成不同点数的FFT计算时可以通过增减模块级数很容易地实现。

二、组合数N=r1r2点混合基FFT原理

计算N点DFT:

![]()

式中k=0,1,…,N-1。

若N=r1r2的组合数,可将n(n<N)表示为

式(2)的意

义在于,计算组合数N=r1r2点DFT,等价于先求出r?2组r?1点的DFT,其结果经过对应旋转因子的相位旋转后,再计算r1组r2点的DFT。实际应用中,DFT往往用它的快速算法FFT实现,因而式(2)中的r1点DFT和r2点DFT都用r1点FFT和r2点FFT实现。

三、可扩展FFT处理器实现结构

根据式(2)的FFT算法原理设计FFT处理器的可扩展结构如图1所示。

采用流水线模块化级联结构,把FFT处理器划分成短点数FFT、级间混序RAM和相位旋转等功能模块,设计的各功能模块可以重复利用,通过复用或增减各功能模块可以灵活改变FFT处理器的计算规模,而且不增加设计量。在图1结构中,当Li=1时,就演变成了基2 FFT;当Li=2时,就演变成了基4 FFT;同理,当Li≠Lj时,就演变成了高组合数的混合基FFT。

1.短点数FFT阵列结构

-Tukey算法结构实现时,有大量的复数乘法实际上转化为加减运算,所以用阵列结构实现不但具有速度快的优点,而且所用器件资源也减少很多,通过对阵列结构短点数FFT进行时分复用,可以提高运算单元的使用效率。

2.相位旋转运算单元

实现短点数FFT级间相位旋转,采用ROM存储旋转因子与数据复乘的传统方法,不仅涉及乘法运算,而且会消耗大量存储器资源。

利用CORDIC算法实现组合数FFT级间数据的相位旋转,把乘法转化成加减法运算,适合FPGA的大规模集成。可以设计出统一结构的CORDIC处理器模块,重复利用于不同级间实现相位旋转,而且其控制逻辑非常简单。

(1)CORDIC算法原理

如果旋转角度θ可以分解成n个小角度φi之和,即:

公式:

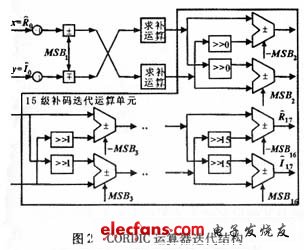

(2)CORDIC处理器结构设计

本文提出了一种流水线CORDIC处理器结构的解决方案。实现式子(4)的迭代运算时采用补码移位和补码加减运算,可以减少大量求补运算,其迭代结构如图2所示。

前者在于左移补零的位数的不同,这样,只需要改变n0k0的放大倍数(改变左移低位补零的位数),就可以把同一方向向量功能模块级联到图1 FFT处理器的不同级间来计算CORDIC处理器的MSBi,这就大大地减小了重复设计,其迭代结构如图3所示。

上周热点文章排行榜

上周资料下载排行榜

论坛热帖

热门博文

创新实用技术专题

热评

- LM3S9B96开发板手册及原理图

- STM32F103ZET6红牛电路图

- 高通发布全新设计DragonBoard板

- NI推出Single-Board RIO嵌入式介面

- protel99se正式汉化版免费下载

- hi3515海思原版原理图

- matlab 7.0软件下载(免费破解版)

- TX-1C型单片机开发板原理图

- 三菱A500变频器原理图

- 三相IGBT全桥隔离驱动电源设计

博文

- 问什么邮箱激活不了

- 八成大学生认同先就业后择业

- 我的心路

- 为什么邮箱激活不了

- 你是否曾这样伤害过一个人?

- 2012.5.12 第一个DS18B20程序

- 到底有多少人在校园里浪费青春

- 到底有多少人在校园里浪费青春

- 蓝牙技术越来越鸡肋

- 【博客分享季】 我的单片机入门

用户评论

查看全部 条评论

查看全部 条评论>>