您的位置:电子发烧友网 > 电子技术应用 > 嵌入式技术 > FPGA/ASIC技术 >

稳压器和SoC之间的走线阻抗问题 - 传授压箱绝技:从SoC设计人员那都了解不到的功耗管理问题

2012年09月04日 17:16 来源:Altera公司 作者:Ron Wilson 我要评论(0)

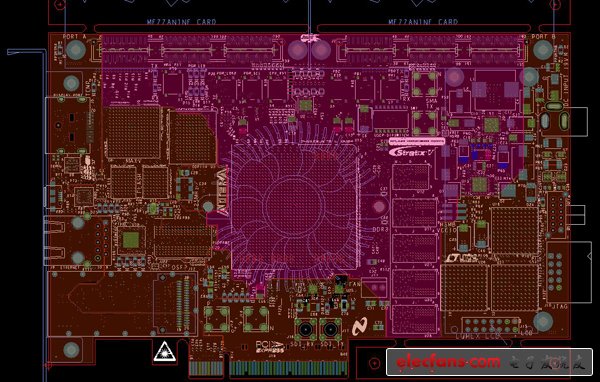

稳压器和SoC之间的走线阻抗等问题有可能成为很难解决的问题。如果SoC的电源管理设计产生较大的负载瞬变,可能会导致非常复杂的布板,或者昂贵的其他电路板层,如图2所示,对于电源系统设计人员,稳压器会处理瞬变。

除了稳压,还有信号完整性问题。供电电源线出现快速大电流瞬变,可能会成为耦合噪声的主要来源,这些噪声会影响电路板上的其他电源线,以及信号线。IC物理设计人员比较熟悉这类信号完整性分析,但是,对于大部分电路板设计人员而言,设计起来会有一定的难度。

图2.Stratix V开发板的第13层,显示了设计人员选择分配整个板层,将稳压器(右下侧)连接至VCC。很难有更好的解决方案来处理大电流瞬变

Odabaee强调说:“参考设计非常重要。我们这样的供应商通过查看设计来提供帮助。但是,设计一个50-Amp、0.9-V系统仍然需要很高的技巧。”Linear Technology公司合作伙伴解决方案经理Gerard Velcelean也同意这一观点:“老板让内部员工来处理这些问题。而小组人员如果不借助参考设计,很有可能会遇到问题。”

结论

现代SoC——无论是ASIC、ASSP还是FPGA,其隐含的一些技巧能够有效的降低能耗。但是,这些技巧越隐含,出现不良结果的风险就越大,这些结果可能会与系统使用模型冲突,使得电源设计更加复杂,或者不可预测的失效模式等。当然,SoC供应商会提供帮助。TI的Bittlestone说:“我们用了很多的逻辑门来实现电源管理系统的接口,以方便系统设计人员的使用。”但即使如此,更重要的是,SoC用户应采用参考设计,或者深入理解他们所遇到的问题。

本文导航

- 第 1 页:传授压箱绝技:从SoC设计人员那都了解不到的功耗管理问题

- 第 2 页:SoC设计实例分析

- 第 3 页:电源线的问题

- 第 4 页:稳压器和SoC之间的走线阻抗问题

标签: