ISE12.2设计套件强化了其部分可重配置技术设计流程,并通过智能时钟门控技术降低24% 的 BRAM 功耗。赛灵思部分可重配置技术,是目前唯一经行业验证的可重配置FPGA

2010-07-31 12:39:03 439

439 和软件设计两个方面对多重配置进行分析,给出了多重配置实现的具体步骤,对实现复杂硬件设计工程有一定的参考价值。##本文通过硬件电路和软件设计两个方面对FPGA的多重配置方法进行了详细介绍,本文所介绍的多重配置方法灵活方便、易于操作、电路简单,在工程中有很高的应用价值,同时关于bit流压缩的方法也值得参考。

2014-01-24 14:17:22 13670

13670

随着FPGA 成为系统级解决方案的核心,大型、复杂设备常需要多片大规模的 FPGA。如果使用 PROM 进行配置,需要很大的 PCB 面积和高昂的成本.

2015-02-04 11:42:27 7817

7817 上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

AS安全模式建立完毕后,UE和gNB之间会触发RRC重配置流程。

重配置信令流程如图所示:

那么触发重配置流程的目的以及重配置消息中有哪些关键字段呢?

1 RRC重配置流程的目的

2023-05-10 15:44:58

直接把所有电路做在一个工程中,这样使用的FPGA芯片容量太庞大,非常昂贵,而且电路胶合控制太复杂,这时候我们可以对每种FPGA模型进行分别生成配置文件,当根据实时状态现场更新FPGA电路。这样就可以采用

2012-04-26 14:27:03

使用的是SPARTAN-3E的开发板,在fpga配置文件时,.bit文件的下载时,程序可以在线正常运行。但使用.mcs文件配置时,ISE上显示program success,但板子上的FPGA并没有

2015-03-16 17:05:25

引言针对需要切换多个FPGA配置码流的场合,Xilinx公司提出了一种名为System ACE的解决方案,它利用CF(Compact Flash)存储卡来替代配置用PROM,用专门的ACE控制芯片

2019-06-10 05:00:08

进行编程。用户可以根据不同的配置模式,采用不同的编程方式。FPGA 的使用非常灵活。目前,大部分的 FPGA 在使用时都需要外接一个 EPROM 保存其程序,加电时,FPGA 芯片将 EPROM 中

2018-09-06 09:11:58

FPGA都可实现静态重构。后者则是指在系统实时运行中对FPGA芯片进行动态配置(即在改变电路功能的同时仍然保持电路的工作状态),使其全部或部分逻辑资源实现在系统的高速的功能变换和时分复用。动态重构技术

2011-05-27 10:22:59

芯片实物图

FPGA 发展历程在 PLD 未发明之前,工程师使用包含若干个逻辑门的离散逻辑芯片进行电路系统的搭建,复杂的逻辑功能实现起来较为困难。

为了解决这一问题,20 世纪 70 年代

2023-05-30 20:40:25

Cyclone® IV GX 收发器支持对收发器的不同部分进行动态重配置,而无需对器件的任何部分断电。本章节提供并讲解了用于动态重配置各种模式的实例。您可以使用 ALTGX_RECONFIG

2017-11-14 10:53:11

`Xilinx FPGA入门连载17:PWM蜂鸣器驱动之复位与FPGA重配置功能特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1 复位

2015-10-26 12:05:15

,FPGA进行主串模式。可是断电之后 重启 FPGA并没有从PROM中自动加载程序,这是为什么?请大家多指教哈 这问题纠结小弟两天了........

2014-10-11 11:16:08

Xilinx PlanAhead工具资料说可以用来部分动态重配置,我现在想对芯片的每一帧中每一位进行逐位翻转的动态重配置,使用PlanAhead能够实现么?应该怎么理解Planahead的部分重配置,如何应用?希望知道的朋友告诉下,对这个有点迷茫。

2015-06-01 10:11:33

重配置硬件的关键特性,比如并行性、可定制性、灵活性、冗余性和多功能性进行了充分的探索。在概念设计完成后,我们希望在原型中实现设计。为此,赛灵思 Zynq™-7000 可扩展处理平台成为了理想选择。该款

2019-07-05 08:34:21

产生不同的电路功能。因此,FPGA的使用非常灵活。 FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程

2016-12-13 15:22:16

产生不同的电路功能。因此,FPGA的使用非常灵活。 FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程

2016-12-13 18:12:57

的USB电缆对闪存PROM进行了编程,但之后没有配置fpga。我错过了什么?下一个命令用于生成文件: bitgen -w -g StartupClk:CCLK -g Binary:yes -g

2019-05-29 12:42:35

FPGA的配置,这里不得不提一下他们和CPLD内部存储介质的不同。CPLD由于大都是基于PROM或Flash来实现可编程特性,因此对他们进行在线编程时就已将配置数据流固化好了,重新上电后还能够运行固有

2016-07-27 16:45:59

我用的是Spartan-3E系列的芯片。我想有两种下载方式,方式一是通过JTAG直接给FPGA下载程序,方便调试。方式二是将程序烧到PROM里面,在上电时FPGA自动从PROM进行配置。现在的问题是

2013-10-18 10:06:47

LabVIEW,LabVIEW Real-TIme模块和LabVIEW FPGA模块以及PXI-7931R可重配置I/O板卡完成实时仿真,并对I/O信号实现精确、灵活的定时与同步。HIL仿真要求作为工业

2019-05-31 09:05:07

相当部分的 STM32芯片都带USB模块,有时我们会考虑利用STM32芯片的USB模块进行程序代码的下载或升级。USB协议中有专门针对设备固件升级的类协议,即可以通过DFU类协议进行产品固件的加载或更新。关于STM32产品的DFU程序下载和升级,ST官方有相关的资料文档。

2021-08-05 06:45:49

,以便为Microblaze实现不同的periferal。我已经读过Spartan3 FPGA支持部分重配置,但我不知道它是否支持动态重配置,而Microblaze仍在使用中。有帮助吗?提前致谢缺口

2019-05-14 06:28:56

你好。我在我的设计中使用了两个FPGA(Spartan 3)。在这种情况下,我可以使用单个Config PROM将我的位文件加载到FPGA。如果是,我应该如何连接FPGA和PROM,以便相应的配置

2018-09-28 11:36:13

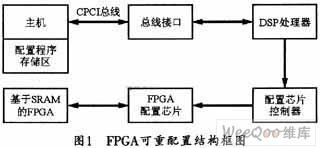

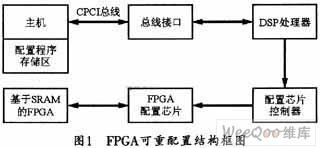

本文介绍的基于FPGA的可重配置系统可以在设计后期甚至量产阶段通过重新编程以适应标准和协议的改变。

2021-05-13 06:35:49

的灵活性和更高的性能,它正迅速成为军事、公共安全和商业无线领域的事实标准。 SDR在商业领域日益流行的一个关键原因是它既能对多种波形执行基带处理,又能进行数字中频(IF)处理。中频处理将DSP的应用范围

2019-07-29 07:21:01

大家好,我已经阅读了很多关于如何从PROM闪存和SPI闪存配置FPGA的PDF文件,但我需要知道如何使用mcs文件配置闪存本身(我知道它可以通过IMPACT完成,我知道所有步骤,但是我需要知道这些

2019-07-10 07:36:39

如何利用ST官方软件工具DfuSe进行相关编程操作?如何利用STM32芯片的USB模块进行程序代码的下载或升级呢?

2021-11-02 06:25:28

或系统重构。结合对FPGA重配置方案的软硬件设计,本文通过PC机并通过总线(如PCI总线)将配置数据流下载到硬件功能模块的有关配置芯片,从而完成配置FPGA的全过程。有谁知道,具体该怎么做吗?

2019-08-07 06:17:30

后即可进入bootloader。可是在某些应用需求中,特别是成熟的产品中,往往不方便拆开外壳来修改Boot引脚。如何在不修改boot引脚的情况下进入DFU模式来进行程序升级?成为了产品的新需求。一、ST芯片的启动模式ST芯片的启动模式有三种。Main Flash Memory 称为主Flas.

2021-08-10 07:02:27

你好:我正在使用三个XCF32P PROM来使用iMPACT配置XC5VLX330 FPGA。 FPGA和XCF32P PROM可以通过JTAG配置。* .mcs文件可以写入XCF32P。但是再次上

2020-05-28 06:24:43

我试图找出部分重配置的配置架构。从我之前使用Virtex-5 FPGA的工作开始,帧将跨越时钟区域的垂直切片。但是,我找不到任何类似的Virtex-7文档。我找到的只是configuraiton指南

2020-05-29 08:54:01

随着大规模集成电路的快速发展,系统设计已从传统的追求大规模、高密度逐渐转向提高资源利用率,使有限的资源可以实现更大规模的逻辑设计。利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储

2019-08-06 07:05:37

你好我打算用xc5vlx20t。我应该如何连接PROM,以便花费最少的时间配置FPGA?我想更改PROM中的配置文件并重新配置电源开启时fpga怎么样SHOULDI呢?谢谢大卫

2020-06-02 13:31:37

你好,我正在尝试用.mcs文件编程我的PROM。它实际上对PROM进行编程,但是当我关闭电路板并按下prog引脚时,没有任何反应。以下是详细信息:1.董事会是定制董事会,2.

2019-10-31 08:59:41

嗨,我们计划在我们的新设计中使用两个来自Spartan-6 famliy的FPGA(特别是XC6SLX100-3FGGI。)。我们设计的设备需要在现场进行远程sw和fw升级,并采用故障安全操作

2019-05-30 10:05:15

单片机连接外部硬件看门狗后,程序下载不了,拆除硬件看门狗后,程序就可以下载了。应该是程序下载过程中外狗一直复位单片机,导致程序下载不了。有什么方法能使连接外部看门狗还能进行程序的升级

2019-09-16 13:48:40

你好,我想使用两个PROM(XCF32P)来配置我的XC4VLX200。我知道我可以使用M [2:0]引脚确定FPGA配置模式。但我不知道PROM如何从FPGA获得当前的配置模式。你能告诉我哪些引脚用于通知PROM当前的配置模式吗?谢谢。

2020-05-27 10:13:34

如何用ISP功能对Nuvoton8051单片机系列进行ISP升级?

2020-12-21 06:36:14

TI工程师:你们好!现在由于工程项目上需要,计划通过F28M36的以太网功能进行程序升级,以前做过28335的CAN程序升级,是在28335的flashAPI上进行修改编写Bootloader

2018-09-20 11:50:12

本文提出了一种全新的总线可重配置的多处理器架构。该架构结合了多核与可重配置处理器的优势,具有并行性高、计算能力强、结构复杂度低并且应用领域广泛灵活的特点。对

2009-06-13 14:11:04 11

11 介绍了基于ARM和FPGA的端到端重配置终端的硬件平台设计方法。给出了系统设计的硬件结构和重要接口, 提出了由ARM微处理器通过JTAG在系统配置FPGA的方法, 以满足重配置系统中软件

2010-09-14 16:40:09 21

21 本文档主要是以Altera公司的Stratix II系列的FPGA器件为例,介绍了其内嵌的增强型可重配置PLL在不同的输入时钟频率之间的动态适应,其目的是通过提供PLL的重配置功能,使得不需要对

2010-11-02 15:17:24 27

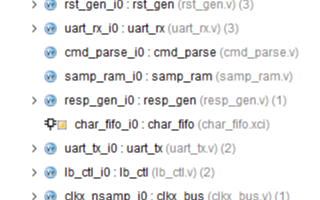

27 实现了一种用于上位机和FPGA处理板之间通信的可重配置接口,详细介绍了该接口的包格式设计和FPGA逻辑设计。仿真结果表明,该可重配置接口能根据信令,实现准实时在线参数配置

2010-11-22 15:15:28 12

12 FPGA的全局动态可重配置技术主要是指对运行中的FPGA器件的全部逻辑资源实现在系统的功能变换,从而实现硬件的时分复用。提出了一种基于System ACE的全局动态可重配置设计方法,

2011-01-04 17:06:01 54

54 摘要: 一种基于嵌入式系统和Inlternet的FPGA动态配置方案。详细介绍了该方案的设计思想,并给出了设计实例。与传统的FPGA配置方案相比,该方案具有灵活

2009-06-20 10:37:59 355

355

基于SRAM的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存字的配置数据决

2009-06-20 11:05:37 845

845

采用VC++程序的FPGA重配置设计方案利用现场可编程逻辑器件FPGA的多次可编程配置特点,通过重新下载存储于存储器的不同系统数据

2010-04-14 15:14:57 580

580

本文介绍了通过处理机用CPLD和Flash实现FPGA配置文件下载更新的方法。与传统的JTAG或PROM串行下载配置方法相比,此方法具有更新配置文件灵活方便、易于操作、适用于大容量FPGA下载的特点

2018-10-25 05:51:00 8194

8194

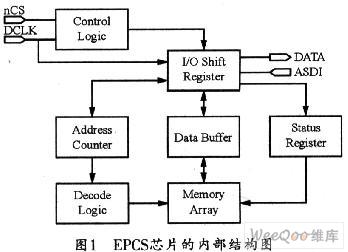

基于查找表技术的FPGA在应用时需要外置一个非易失性存储器来存储配置数据。如何方便灵活地对一个系统中多片FPGA的配置数据进行升级是本文讨论的问题

2011-06-22 09:39:38 2037

2037

为了满足对分数阶 信号变换 进行实时计算的要求,提出一种基于Altera St ratix II FPGA 平台的可重配置分数阶信号变换处理器的硬件实现方案. 根据角度分解的算法,设计了一种通用的硬件框

2011-07-04 15:13:03 33

33 利用赛灵思 FPGA 的动态重配置功能,同构多线程执行模型可同时兼得软件灵活性和硬件性能。

2011-09-01 09:27:26 584

584

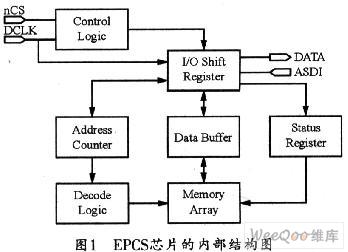

FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理

2011-09-08 17:50:27 1734

1734 基于 FPGA 的 RCS 有几项值得注意的设计事项与优势。其核心部分是我们连接在一起以构成单个计算系统的数个FPGA。在我们的可重配置系统中,我们使用了正交通信系统,将 FPGA 布置在矩

2011-09-20 08:57:32 27

27 本文着重介绍了 Xilinx Platform Flash PROM 如何帮助系统和电路板设计人员简化 FPGA 配置设计。用于配置 FPGA 的可选解决方案有很多,但它们通常都需要大量的前期设计工作和时间。Platform

2012-01-17 17:33:20 36

36 一些应用利用 Xilinx FPGA 在每次启动时可改变配置的能力,根据所需来改变 FPGA 的功能。Xilinx Platform Flash XCFxxP PROM 的设计修订 (Design Revisioning) 功能,允许用户在单个PROM 中将多种配置存

2012-01-17 17:40:34 43

43 WP374 Xilinx FPGA的部分重配置

2012-03-07 14:34:39 34

34 在过去,静态决策最坏情况分配曾为严格的实时约束提供了解决方案,而现在灵活性也成为一项要求。法国某研究项目建议使用的解决方案是一种分布在 FPGA 资源上,对软硬件线程进行

2012-05-09 10:40:11 1675

1675

本文介绍了XiLinx FPGA中DCM的结构和相关特性,提出了一种基于XiLinx FPGA的DCM动态重配置的原理方法,并给出了一个具体的实现系统。系统仅通过外部和......

2012-05-25 13:42:50 39

39 本文着重介绍了 Xilinx Platform Flash PROM 如何帮助系统和电路板设计人员简化 FPGA 配置设计。用于配置 FPGA 的可选解决方案有很多,但它们通常都需要大量的前期设计工作和时间。Platform

2013-03-14 15:18:22 64

64 对MSP430系列单片机进行编程的方式有以下3种:利用JTAG接口,利用BSL固件和利用用户自定义的升级固件。由于利用自定义升级固件进行程序升级的方式比较灵活,且用途广泛,因此本文将对其作重点介绍。

2016-05-31 13:48:51 3618

3618

们快速开发和部署加速平台。专门针对云级应用而设计的基于FPGA的赛灵思可重配置加速堆栈,包括库、框架集成、开发板并支持OpenStack。通过赛灵思FPGA,该可重配置加速堆栈方案提供了业界最高的计算效率:比x86服务器CPU高出40倍;比竞争型FPGA方案高出6倍。

2016-11-16 16:42:23 648

648 一种基于忆阻器的可重配置逻辑电路_张波

2017-01-08 10:18:57 4

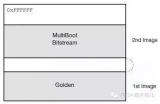

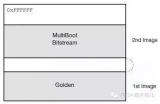

4 地址0处,FPGA默认加载的配置程序。功能:用于引导FPGA跳到第二个配置程序所在的位置,进行重配置,即multiboot功能 用于烧写(更新)第二个配置程序(位于flash的xx偏移位置,偏移位置可由用户设定) 第二个配置程序,叫用户程序(位于flash的xx偏移位置,偏移位置可由用户设定

2017-02-08 10:13:11 906

906

一旦你开始使用一个系统,你可能更愿意它永远不需要升级。但是,通常情况下,这是不现实的。在现在的系统中,更新、升级、打补丁,这些都是司空见惯的。如果你对基于FPGA的系统非常熟悉,那么你可能对通过JTAG对PROM进行编程、Xilinx iMPACT配置和编程工具也比较熟悉。

2018-07-14 05:24:00 3150

3150 这里提到的局部重配置技术(Partial Reconfiguration) 是现场可编程门阵列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分还在正常运行的情况下对其局部进行的重新配置。

2017-02-11 16:32:11 2622

2622 工作效率。通过FPGA 的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA 器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPIFLASH为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多

2017-10-12 17:57:08 15

15 。 在现代的工业自控当中对大型工业流程的分散处理、统一管理成本较高,而且设备的工业级实时监测系统和视频监控系统都需要进行大量的处理,使得成本高,但集中调控性不强,而本系统通过对 FPGA 的区域配置,将上述功能集于一身;不仅成本低廉,体积较小,并且工业级效率也会

2017-10-18 16:38:59 4

4 视频、影像和电信市场的标准推动了异构可重配置DSP硬件平台的使用。在本文中这些平台包括DSP处理器和FPGA,它们提供的现成硬件解决方案可以解决视频、影像和电信设计中的重大难题,同时又不失差异化

2017-11-06 13:59:42 2

2 ,LabVIEW Real-Time模块和LabVIEW FPGA模块以及PXI-7931R可重配置I/O板卡完成实时仿真,并对I/O信号实现精确、灵活的定时与同步。

2017-11-18 18:24:14 1623

1623 对视频等时序关键型应用,采用纯硬件解决方案可提升赛灵思 FPGA 的运行能力。我们采一款基于小型状态机的纯硬件解决方案,并采用内部配置访问端口 (ICAP)接口加载比特流。这种方法具有多种优势

2017-11-22 17:08:56 1492

1492 的应用。在主流的FPGA中,绝大多数都采用了SRAM来存放配置数据,称为SRAM FPGA。这种FPGA的突出优点是可以进行多次配置。通过给FPGA加载不同的配置数据,即可令其实现不同的逻辑功能.FPGA这种可重配置的能力将给数字系统的设计带来很大的方便。

2018-07-18 12:50:00 2407

2407

云级应用而设计的基于FPGA的赛灵思可重配置加速堆栈,包括库、框架集成、开发板并支持OpenStack。通过赛灵思FPGA,该可重配置加速堆栈方案提供了业界最高的计算效率:比x86服务器CPU高出40倍;比竞争型FPGA方案高出6倍。

2018-07-31 09:08:00 731

731 Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允许用户在不掉电重启的情况下,根据不同时刻的需求,可以从FLASH 中贮存的多个比特文件选择加载其中的一个,实现系统功能的变换。

2018-12-04 08:37:00 4654

4654

可重构体系结构已经成为FPGA系统开发的研究热点,并已有许多令人瞩目的研究成果及产品应用。FPGA可重构的应用为用户提供了方便的系统升级模式,同时也实现了基于相同硬件系统的不同工作模式功能。在当

2018-12-30 11:09:00 5670

5670

结合对FPGA重配置方案的软硬件设计,本文通过PC机并通过总线(如PCI总线)将配置数据流下载到硬件功能模块的有关配置芯片,从而完成配置FPGA的全过程。该方法的软件部分基于Visual C++的开发环境,并用C++语言开发动态连接库,以用于软件设计应用程序部分的调用。

2018-12-30 09:26:00 2425

2425

FPGA可重配置带来了很高的灵活性,所以基于FPGA的设计/产品往往也会有后期更新/升级的需求。同时,需要更新/升级的FPGA板卡由于物理条件的限制,可能无法现场升级。

2018-09-15 09:30:47 3556

3556 主设备可以为控制器,CPLD等等。当然FPGA也支持通过JTAG的方式进行程序下载,同时也可以通过JTAG进行FPGA时序抓取。 FPGA的配置过程包括以下几方面:复位,程序加载,初始化,最后进入用户

2018-11-18 18:05:01 481

481 本视频介绍了UltraScale +芯片的部分重配置功能,展示了Vivado Design Suite中部分重配置的新功能,并介绍了对部分重配置的更广泛的访问权限

2018-11-20 06:25:00 3831

3831 关键词:PLD , SRAM , 可重配置电路 由于SRAM的可重配置PLD(可编程逻辑器件)的出现,为系统设计者动态改变运行电路中PLD的逻辑功能创造了条件。PLD使用SRAM单元来保存字的配置

2019-02-23 14:30:01 675

675

本文档的主要内容详细介绍的是程序的扩展性如何进行程序的扩展。

2019-04-26 18:26:00 0

0 Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。

2021-07-05 15:28:24 3140

3140

使用CH340串口模块对STM32进行程序下载一、接线二、利用FlyMcu进行STM32程序下载1、STM32配置2、FlyMcu配置一、接线

2021-12-20 19:37:32 21

21 西门子S7-1200系列PLC可以通过存储卡进行程序的更新,固件版本的升级以及程序数据的存储多项功能。本例进行程序更新的操作。

2023-03-07 10:34:16 2603

2603 一般情况下,要重新配置一个FPGA需要使其处于复位状态,并通过外部控制器重新加载一个新设计到器件中。而局部重配置技术允许在FPGA内部或外部的控制器在加载一个局部设计到一个可重配置模块中时

2023-03-17 14:03:39 1508

1508 除通过外部多功能IO来选择之外,易灵思通过内部重配置实现远程更新操作也非常简单。

2023-05-30 09:24:32 712

712

电子发烧友App

电子发烧友App

评论