与EVAL-AD7960FMCZ评估板及其控制器板SDP-H1上的任何信号频率都不相关。找出杂散源的另一种方法是清理测试台,也许是测试台上的某些物体产生了外部干扰。当关掉台架上的日光灯后,杂散消失。此外还发

2019-02-14 14:18:45

杂散测试线损问题? 有的时候测得是一个范围,怎么确定线损呢?

2016-09-11 23:41:06

达到高鉴相频率,低相噪的目的,甚至会超过小数分频的锁相环。另外也需要考虑由于采用了杂散补偿电路,所以该电路会增加环内的相位噪声。 从杂散性能上看,在较小的信道间隔(1MHz)上,小数分频的锁相环的杂散

2019-01-16 12:27:07

考虑由于采用了杂散补偿电路,所以该电路会增加环内的相位噪声。从杂散性能上看,在较小的信道间隔(1MHz)上,小数分频的锁相环的杂散性能也会比整数分频的锁相环好。在中等的信道间隔(10kHz,1MHz)上

2017-04-27 15:58:16

出现一个与基带信号相关的杂散点幅度-50dBm左右,影响了射频输出的Sfdr。具体现象:

输出2.2ghz点频时,杂散点在2.6GHz

输出2.3ghz点频时,杂散在2.5ghz

输出2.4ghz点频

2023-12-04 07:39:16

用AD9288做GPS中频采样,当输入一个中频15MHz -10dBm的电频干扰时,62MHz采样时钟,对62000采样数据做FFT处理,发现幅度谱在干扰频率附近有很多杂散,如何解决? 求大神帮忙!用AD9218效果一样

2023-12-12 08:21:06

用AD9288做GPS中频采样,当输入一个中频15MHz -10dBm的电频干扰时,62MHz采样时钟,对62000采样数据做FFT处理,发现幅度谱在干扰频率附近有很多杂散,如何解决? 求大神帮忙!用AD9218效果一样

2019-01-21 16:03:00

我们准备把AD9361用于TDD系统,但由于时延等问题,想把9361配置成FDD模式,通过外部的开关实现TDD切换;需要了解一下FDD模式下TX通道的杂散/噪底等情况,以便设计开关的收发隔离;1

2018-12-27 09:24:47

各位大牛,请教一下。我现在用AD9467-250,采样时钟用AD9517-3出的200MHz,采集70M、0dBm单音信号。频谱上出现较多的杂散。ADC前端电路按照AD9467手册推荐的设计。ADC

2019-01-25 08:21:14

各位大牛,请教一下。我现在用AD9467-250,采样时钟用AD9517-3出的200MHz,采集70M、0dBm单音信号。频谱上出现较多的杂散。ADC前端电路按照AD9467手册推荐的设计。ADC

2023-12-08 06:52:03

请教下各位,我使用FPGA出频率为30MHz的数字信号,数据速率为61.44MHz,给AD9779当输入,AD9779内部做122.88MHz的上变频,则有用信号会在152.88MHz处,但同时会在154.32MHz处有一幅度相差50dbc左右的杂散信号,请问下这有可能是哪里引起的,谢谢了!

2018-11-19 08:57:37

请教下各位,我使用FPGA出频率为30MHz的数字信号,数据速率为61.44MHz,给AD9779当输入,AD9779内部做122.88MHz的上变频,则有用信号会在152.88MHz处,但同时会在154.32MHz处有一幅度相差50dbc左右的杂散信号,请问下这有可能是哪里引起的,谢谢了!

2023-12-25 06:07:25

1GHz分频为500MHz;该500MHz与单音输出频率(比如230MHz)混频后产生了较大杂散(混出270MHz)。 请问:如何才能能降低该杂散?有没有方法让AD9912内部不产生sysclk的2分频信号或降低该分频信号带来的干扰?

2019-03-08 15:14:23

参考输入为245.76MHz/0dBm,输出61.44MHz附近给锁相环做参考,可是输出一直有杂散。我改用信号源直接给锁相环提供参考就没有杂散了,所以推断出是AD9912引入的杂散。我同事他也用

2018-12-25 11:41:21

前段时间做了一个关于AD9958的板子,输出频率在14MHz到22MHz,从其PDF资料上的相位噪声曲线看,15MHz在10KHz以内的杂散非常好,而实际上做出来近端几百Hz的杂散最差的只有80左右

2019-02-22 08:27:59

我使用ADF4351,其输出在中心频率偏移184k附近有杂散输出,通过减小环路带宽,减小充电电流等,杂散有一定的降低, 此时带来靠近中心频率出的噪声升高,通过对比不同的板卡,都存在类似的现象,环路

2018-10-12 09:24:23

最近在用adf4355,输出频率3915MHz,参考频率100MHz,PDF频率50MHz,其余配置为adi软件导出的默认配置,结果近端出现如图所示杂散,频率大约在28kHz和66kHz两处比较明显。已经排除电源影响,且修改环路滤波器和降低cp电流均没有什么变化。请教各位大神还有什么原因是没有考虑到的

2022-01-21 16:49:31

,小数模式],其寄生的鉴相杂散非常大,而且从低频到高频段一直存在,幅度也相差无几!最终导致在ADF4355输出的频谱中就存在第一中频信号 3.8GHz或和我需要的射频信号。比如,我需要接收2.55GHz

2018-09-07 10:43:06

我用cc1120实现频分复用,现在发现存在杂散现象,尤其是2个以上不同信道一起发射时,他们的杂散叠加导致其他信道被污染,请问这种情况有解决方法么

2018-06-24 03:14:54

DC/DC开关电源的开关频率杂散有什么有效的解决方法没有?在其后加多级LDO都不能很好的解决。寻找一种能够通过电感或电容的解决方案。开关频率在几百KHz左右的。

2024-01-08 07:25:39

IOUPDATE来更新。写法如下:第一个脉冲写16384,第二个写32768,第三个为49152,第四个为0,即进行周期性相位累加。这样的操作会导致频谱整体偏移,偏移量为1/4脉冲频率,即25K,因为每次步进的相位

2018-08-30 11:49:24

在使用HMC704中遇到非整数边界杂散问题,麻烦各位看看: REFin:100MHz, N=2, 鉴相频率50MHz输出分别为10025MHz,10050MHz和10075MHz环路滤波器带宽:1

2019-02-21 14:05:56

70MHz的时候,只改变AD9912的输出,HMC833寄存器不改变。 现在遇到的问题如下: 1.在低频段(1.5GHz内)有一大片鉴相频率整数倍的杂散信号存在,杂散信号与主信号间的差距大概在

2019-02-22 12:27:30

,还望详述)来达到尽量减小此杂散的作用,最好能到-50dBc以下。因为我最终是想将此款芯片用在宽频带输出上,所以对于某个特定频点通过改变鉴相频率来达到远离Fpfd整数倍的目的之法并不适用,如本例中若取

2018-09-04 11:35:47

每隔3KHz存在杂散,无法通过降低信号功率,改变时钟数据相位来改善

更改参考时钟为60MHz,杂散间隔变为15K

更改参考时钟为20MHz是,杂散消失

请问各位大神这个问题应该怎么考虑,谢谢

另外当去掉DAC输出辅助之后用示波器测试波形如下,这种现象是信号发生反射了吗?

2023-12-07 07:09:55

锁相环 (PLL) 和压控振荡器 (VCO) 输出特定频率的RF信号,理想情况下此信号应当是输出中的唯一信号。但事实上,输出中存在干扰杂散信号和相位噪声。本文讨论最麻烦的杂散信号之一——整数边界杂散

2019-10-11 08:30:00

于相位噪声、锁定时间或杂散却并非如此。表1给出了环路带宽对这些性能指标的影响的大致参考。 性能指标最优带宽备注抖动BWJIT最优值一般为BWJIT。在低集成限制更高的一些情况下,有时较窄的环路带宽实际上效果更好。锁定时间无限VCO锁定时间随着环路带宽的增加而提高,但有时会受到VCO校准时间…

2022-11-16 07:56:45

一种准确地预测由泄漏电流引起的 PLL 基准杂散噪声之简单方法

2019-05-27 15:55:17

频率即可,这与系统运营商的关注点是吻合的,因为他们更关心的是与系统正常运营密切相关的带内指标。显然,不会存谁为了考虑到全频段(9kHz`12.75GHz)的杂散测量而在基站的输出端设置—个宽带定向耦合器

2017-11-15 10:35:09

正弦波信号从信号发生器注入电源引脚。调制到RF载波的正弦波产生边带杂散,其偏移频率等于正弦波频率。杂散水平受正弦波幅度和器件灵敏度的影响。简化的PSMR测试设置与PSRR的相同,如图5所示,但输出主要

2021-11-20 07:00:00

整数边界杂散不受欢迎的原因有哪些?如何改变PFD频率?怎样将ADIsimFrequencyPlanner应用到宽带VCO里?

2021-04-12 06:28:29

小数分频器整数边界杂散问题的提出小数分频器整数边界杂散的优化设计

2021-04-19 08:32:15

DDS的工作原理是什么?如何抑制DDS输出信号中杂散问题?

2021-05-26 07:15:37

什么是杂散信号呢?有用频率以外的无用信号就是杂散信号,或者说是有用频率以外新产生的功率(一般为负几十dBm吧)。杂散信号是怎么产生的呢?一般无源器件像滤波器(Filter)、衰减器

2019-11-14 10:59:39

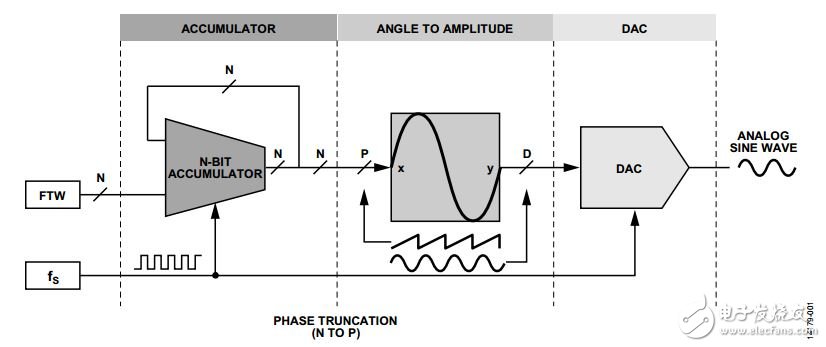

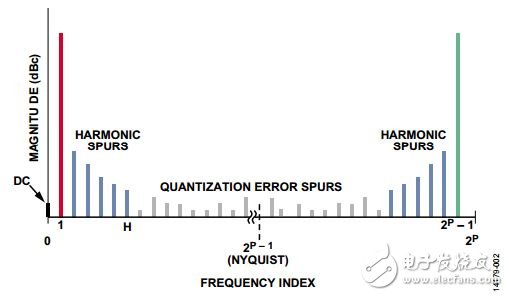

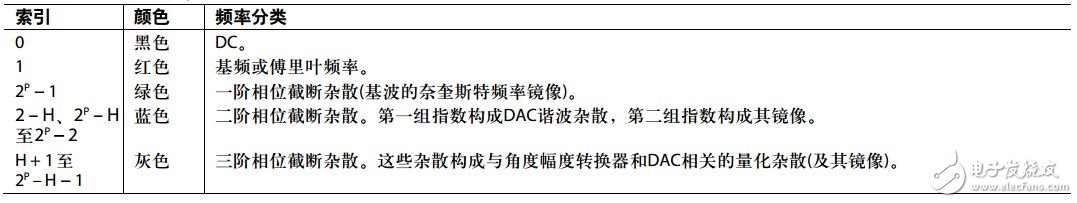

直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程相关的杂散等。此类杂散是实际

2023-12-15 07:38:37

。在这种情况下,由镜像、LO泄漏和三次谐波产生的杂散信号都处于相同的频率。图5所示为通过频谱分析仪测得的各发射输出。图6所示为组合输出。在这个特定的测试中,相对于载波以dBc为单位测量的镜像杂散和LO

2021-05-08 07:30:00

假设您已经通过迭代信息传递相位边限和回路带宽在锁相环(PLL)上花费了一些时间。但遗憾地是,还是无法在相位噪声、杂散和锁定时间之间达成良好的平衡。感到泄气?想要放弃?等一下!你是否试过伽马优化参数?

2019-07-31 07:26:15

David Brandon简介直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换

2018-11-01 11:24:06

消除它们。但这种方法可减少整数边界杂散及其产生的其它杂散。 图3中的“杂散消失”路径展示了使用该可编程倍频器的效果。100kHz频率下的整数边界杂散大约减少了9dB,同时还大大减少了50kHz和10kHz

2018-09-06 15:11:00

经常容易搞错AM,FM或PM,他们很难区分呢?时钟相位噪声图中的杂散信号为什么会影响时钟的总抖动?

2021-03-05 08:06:14

传导和辐射杂散的FCC限值是什么情况,没看懂,求指点。另外,2G和3G的杂散测试,除了测试频率范围不同外,还有哪些不同,提前谢谢大神!!!!!!!

2013-03-10 21:38:03

小弟正在调试一款X波段(9.6-10.8GHz)的锁相环,采用的是内部集成VCO的HMC778LP6CE芯片。在调试中,我发现在距中心频率50Hz整数倍的频率处有很多杂散,请问各位大神这些杂散

2014-07-21 15:47:54

要求的不同,有多种处理此类问题信号的方法。谨慎的频率规划和滤波虽然能够有助于大幅度减少杂散脉冲的数量,但是它们总是会有。因此,系统设计师必需在混频器输出端上准确地测量杂散电平,以确定怎样用最佳的方式应对它们,这一点是很重要。

2019-07-23 08:17:34

)也是一种DAC,可以生成数字正弦信号,并将其馈入DAC来产生相应的模拟信号。本文将重点介绍新近出现的一项技术突破,它借助DDS技术大幅提升了DAC的无杂散动态范围(SFDR)性能。

2019-06-27 06:29:11

值、管地电位波动、管道附近的土壤电位梯度和管道中的电流值四种方法判断是否存在杂散电流干扰。表1 我国直流干扰程度判断标准 管地电位正向偏移值(mV) 直流干扰程度

2020-12-01 16:22:35

直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程相关的杂散等。此类杂散是实际

2018-08-27 11:34:36

两个增益和相位图像杂散及一个失调杂散(图5)。可在2/3 × 奈奎斯特频率时看到失调杂散,但在这种情况下,失调杂散并非SFDR的主要贡献因素。SFDR限制增益和相位杂散可在(2/3 × 奈奎斯特频率

2018-11-01 11:31:37

100M晶振50M鉴相,环路带宽120K,全频带测试,频率在4150M以下1M步进杂散非常高,但是这个频率以上就没有,请问这是啥问题导致的,减小cp电流几乎无改善,100K,10K,1K就更差了

2018-08-01 07:04:21

贵公司的专家们好,我最近在做的项目使用的AD9914芯片,芯片使用3.2GHz参考时钟,DDS输出950MHz信号时150MHz,200MHz,处有-65dBc左右的杂散,300MHz处有

2018-11-13 09:35:04

ADF4351输出,相噪远不及器件参考值理想。而且在离中心频率最近处的杂散出现在偏离中心频率5KHz的地方。从频谱来分析,我估计如果能减小或者消除该杂散,则相噪应该可以明显变好。电源我采用了两颗

2018-09-29 15:40:47

ADF4355,采用100MHz OCXO作为参考,输出2280MHz,鉴相频率100MHz,近端出现70Hz左右(及其倍数)的杂散,抑制度在47dBc左右,CP电流设置0.3mA,调整Bleed

2018-08-22 10:40:08

您好,请问我在做ADF4356锁相环时发现在PFD谐波处有较强杂散,高达-75dBc,可以看成就是整数边界杂散,但是杂散距离中心频率已经有了15M左右,环路带宽40KHz,请问一下这是什么原因导致

2019-02-15 13:26:51

DC/DC开关电源的开关频率杂散有什么有效的解决方法没有?在其后加多级LDO都不能很好的解决。寻找一种能够通过电感或电容的解决方案。开关频率在几百KHz左右的。

2019-02-15 14:38:57

如图,这是数据手册上说的HMC833参考为50MHz输出为5900.8Mhz时的杂散情况。图上频偏频偏为400KHz和800Khz的地方都有杂散。根据数据手册上的理论,我能理解800Khz处的杂散是整数边界杂散,但我没弄懂400Khz处的杂散缘由?哪位明白的,可以解释一下?谢谢

2018-10-09 17:57:58

HMC833低杂散(1)HMC833是否有低杂散模式。(2)改变seed in fraction是否有作用?

2019-01-15 08:42:05

,参考源用50M,如果发送频率是50M的整数倍,如3.9G时,杂散指标很好,可达60dB以上,而发送频率为3.9001G时,就会在100K或200K或300K处出现杂散,有时只有40dBc不到,当频率偏移50M整数倍更多,超出环路滤波器带宽时,又会变小。请问这是AD9361的指标水平吗?

2018-08-23 07:15:55

各位好我在看模拟对话的时候,看到边带杂散和开关杂散不太明白,请问大家这其中的含义以及它将导致什么后果?谢谢大家了!!!

2019-01-09 09:29:01

此范围会有利于锁定时间和10kHz相位噪声,但是会降低杂散和1MHz偏移的相位噪声。因此,选择环路带宽的一种较好的方法是先选择最优抖动带宽(BWJIT),然后增加带宽提高锁定时间或低频偏相位噪声,或者降低带宽提高高频偏相位噪声或杂散。

2018-08-29 16:02:55

了,最好能抑制再高些。 常用的抑制鉴相频率杂散的方法是环路滤波器的多级设计,如3级。在鉴相频率固定、3级环路滤波器固定且滤波器带宽已经10KHz不能再低的条件下,还有哪些方法可以改善上面提到的这些杂散呢

2018-11-07 09:03:01

最近调试遇到个问题,40W功放输出功率时在225K左右会有杂散,抑制在-50dB左右,初步认为是由于风扇引起的,如过是风扇引起的话,该如何解决

2014-03-28 09:58:41

EVAL-AD4003FMCZ。结论针对系统应用中高分辨率、精密ADC的杂散问题,本文探讨了判断其根本原因的方法。文中介绍了在五种不同应用情况下消除或降低杂散的特定设计解决方案。本文还探讨了相关的杂散计算方法

2018-10-19 10:38:17

直接数字频率合成器(DDS) 相位截断误差序列是DDS 输出信号误差的主要来源,很有必要对DDS 相位截断误差序列的谱进行研究。文献[1 ]提出了DDS 相位截断杂散谱的精确分析方法,该文对DDS

2011-08-29 16:41:52 21

21 为了能既方便又明白地表示一个信号在不同频率下的幅值和相位,可以采用成为频谱图的表示方法。在傅里叶分析中,把各个分量的幅度|Fn|或 Cn 随着频率nω1的变化称为信号的幅度谱。而把各个分量的相位 φn 随角频率 nω1 变化称为信号的相位谱。

2016-09-18 18:17:58 163538

163538

AN-1396: 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度

2021-03-21 00:44:05 2

2 电子发烧友网站提供《用于计算特定相位截断杂散的频率和幅度的方法.pdf》资料免费下载

2023-11-28 11:32:12 0

0

电子发烧友App

电子发烧友App

评论