摘 要: 机载显示器分辨率越来越高,显示内容越来越复杂,这对图形生成电路提出了更高的要求。提出了一种基于双处理器系统的图形生成电路实现方法,以两片DSP处理器作为绘图核心,配合FPGA和SDRAM帧存构建硬件平台,由主DSP进行绘图任务分配,并将任务分配结果通过Linkport口传递给从DSP,主从DSP根据任务分配结果并行完成图形生成算法运算,从DSP通过Linkport口向主DSP发送图形数据,主DSP将图形数据写入SDRAM帧存中,配合FPGA对SDRAM进行乒乓操作完成图形数据的实时生成与显示。实验结果表明,该方法与单处理器方案相比,在功耗仅增加15%的情况下图形生成效率可提高53%以上,生成一幅1024×768的EFIS电子飞行显示系统画面帧率可达86 f/s。

0 引言

现代飞机座舱显示系统向驾驶员提供飞行器、发动机和其他系统所测试的参数,包括从起飞、导航、着陆等全过程所需要的各种信息[1]。随着电子技术的不断发展,座舱显示系统需要处理的实时信息量不断增加,对机载显示处理系统的实时性、有效性和快速图形处理能力提出了更高的要求[2],主显示器尺寸不断加大,分辨率不断提高,并日益朝着大屏幕化、综合化、信息化和智能化方向发展,向飞行员传递的飞机参数越来越依赖于图形显示[3-5]。

图形生成电路是座舱显示系统的核心部分,其主要功能是根据飞机任务、飞机状态和周边态势等信息生成相应的显示画面,以供飞行员进行观察。军用飞机在做战术动作时,画面变换速度快,要求图形的更新速度也必须很快,至少要比帧或场的刷新速度快,才可以避免画面的断续[6-7]。目前,在役各型飞机的机载显示器一般采用单个DSP+FPGA的架构完成图形生成功能。其中DSP负责图形生成指令的发起和图形生成算法的实现,FPGA负责将DSP图形生成的结果输出显示。由于某些字符图形显示内容(天地球、全罗盘等)生成步骤复杂,且对生成图形质量要求很高(要求反走样等),导致在生成一帧显示图形时单个DSP的计算量过大,造成机载显示器字符图形生成周期过长,数据刷新的实时性不能得到保证;或者在面临较高分辨率的字符图形生成任务时,在要求的数据刷新周期(例如25 ms)内无法完成指定分辨率字符图形的生成计算。由于上述因素的制约,使用单DSP进行字符图形生成的传统方法已不能满足未来机载显示器字符图形的生成需求,研制出一种具有更高性能的机载显示器图形生成装置势在必行。

本文提出一种基于双DSP处理器+FPGA架构的图形生成电路实现方法,利用双DSP协同进行图形生成运算处理,可以显著提高图形生成效率和系统能效比,满足机载显示器高分辨率图形实时生成与显示需求。

1 系统原理

1.1 硬件构成

本系统硬件原理框图如图1所示。

系统主要由主从双片DSP、FPGA、SDRAM、Flash、EPROM等模块组成,其中,主从双片DSP负责绘图运算,通过Linkport通信接口完成数据交互。SDRAM是系统帧存部件,用于存放绘图运算结果数据。FPGA是系统数据的交互和控制中心,配合主DSP对SDRAM帧存以乒乓操作的方式完成绘图数据的读写处理。Flash用于存储画面显示软件,EPROM用于存储FPGA程序。

1.2 显示软件

系统作图时,根据画面内容要求,主DSP(DSP1)将作图任务划分成若干个基本作图单元,并根据各任务计算量和通信时间等因素的约束,将部分任务分配给从DSP(DSP2)计算。这时DSP1向DSP2发送任务编号或者根据任务预先分配结果发送开始作图标志,DSP2收到相应内容后,启动作图任务,并将作图结果保存下来,待任务完成后DSP2将计算结果通过Linkport端口发送至DSP1进行同步显示。双DSP软件的接口关系如图2所示。

双DSP图形画面显示软件由主DSP(DSP1)和从DSP(DSP2)的两部分软件组成。其功能模块框图如图3所示。DSP1画面显示软件主要包括初始化模块和主模块,初始化模块完成DSP系统寄存器、SDRAM、Linkport接口、调色板等初始化功能,主模块由Linkport通信与数据传输模块和画面显示模块组成,其中通信与数据传输模块完成与从DSP的LinkPort通信、任务分配与同步等功能,画面显示模块完成DSP1的作图计算与显示等功能。从DSP由初始化模块及主模块组成,初始化模块主要完成DSP系统寄存器和LinkPort接口等初始化任务,主模块由通信与数据传输模块和作图计算模块等组成,通信与数据传输模块完成接收主DSP的控制命令和将作图计算结果发送给主DSP等两项功能;作图处理模块完成分配的作图任务,并将相应的计算结果(对应像素点信息)保存下来。

2 Linkport通信端口

本文采用的DSP芯片为ADI公司的ADSP-TS201,TS201专门为高速通信设计了基于LVDS技术的Linkport,解决了DSP之间的通信瓶颈问题[8]。TS201带有4路Linkport口,信号通过LVDS形式以DDR数据格式传输,时钟上升沿和下降沿均有数据。每一路都可以同时进行发送和接收操作。通过Linkport口,系统内多片DSP之间可以实现点对点通信[9]。每个链路口的最高单向传输速率是500 MB/s,可以非常方便并行系统中处理器之间的通信[10]。

2.1 Linkport通信协议

Linkport口可以配置为4位模式(对应于4路Linkport口)和1位模式(对应于1路Linkport口),模型如图4和图5所示,Linkport口结构如图6所示。

图6中Tx buffer为发送缓冲,Tx SHIFT register为发送端移位寄存器,Rx buffer为接收缓冲,Rx temporary buffer为接收端临时缓冲,Rx SHIFT register为接收端移位寄存器。

Linkport口通信协议如下:

(1)Linkport口数据以突发方式传输,每发起一次传输最小传输数据量为128 bit。

(2)传输的第一个数据(1 bit或4 bit)在Link口时钟的上升沿传输。

(3)传输的最后一个数据(1 bit或4 bit)在Link口时钟的下降沿传输。

(4)Link口处于空闲状态时时钟一直为低电平,也即有数据传输时才有时钟信号,时钟信号是不连续的。

2.2 DSP间Linkport通信

ADSP-TS201之间进行Linkport通信时,除了直接采用Linkport内核通信方式外,还支持Linkport采用DMA方式进行通信。

双DSP之间的Linkport通信采用了单向循环通讯方式进行测试。DSP1完成Linkport的控制寄存器配置后首先启动发送,发送完成后进入接收等待状态,等待DSP2将数据返回。DSP2在寄存器配置后首先进入接收等待状态,等待DSP1发出的数据。在接收到DSP1的数据后,再将数据发回至DSP1。然后DSP1再启动下一组数据的发送,如此循环,通信流程图如图7所示。

2.3 双DSP之间的LinkDMA内核通信

LinkDMA传输需要配置的寄存器是128 bit的传输控制块寄存器(TCB),TCB包含了4个32 bit寄存器:DMA地址索引寄存器DI、DX寄存器、DY寄存器、DP寄存器。其中DI指明了DMA传输的源或者目的起始地址,DX寄存器的高16 bit用于指定DMA传输的字数,低16 bit用于指定地址的修改量,DY寄存器用于二维DMA传输,DP寄存器包含了DMA传输时所有的控制信息。

对于LinkDMA传输方式,DI设定为传输缓冲区的地址,发送时为源缓冲地址,接收时为目的缓冲区地址。DX中传输字数可以根据传输数据大小决定,地址修改量必须为4。DY必须为0。DP中需要配置操作数据长度为4字方式,指定DMA设备种类(内存、外存等),还需要确定是否需要DMA中断。

DSP1和DSP2在完成LinkPort控制寄存器配置后,DMA通信方式还需要配置LinkPort端口的DMA发送通道DC7与DMA接收通道DC11。选定DC7通道TCB的源地址为内存数据起始地址,地址修改量为4,数据长度为4字模式,设备类型为INTMEM(内部存储器),并使能DMA7的中断。DC11的配置处将数据地址改为内存中接收缓冲首地址外,其他配置与DC7相同。然后还需要在IMASK寄存器中将DMA7和DMA11的中断控制位使能。

3 双DSP并行处理和同步显示技术

未来日益提高的显示器画面分辨率和显示实时性的需求,使得单个DSP在进行高分辨率的画面图形绘制时难以满足要求。因此,采用双DSP或者多个DSP进行作图任务分工,协同并行处理是满足这一需求的有效途径。

双DSP的作图画面选择典型的EFIS画面,包括天地球和全罗盘显示内容。为了实现双DSP并行作图计算和同步显示,需实现基于Linkport通信的任务分配和任务同步的策略。双DSP之间任务分配的合理程度直接影响着双DSP共同作图的总的计算时间,而双DSP计算结果的最终合成以及同步显示则直接影响着显示器画面的显示效果。

3.1 任务分配策略

双DSP任务分配是以对所绘制画面的合理功能模块划分为基础的。根据典型画面软件模块组成,在进行双DSP的任务分配时,首先将典型画面分割成如下若干个绘图模块单元,如图8所示。

根据以上绘图单元的划分方式,在进行双DSP绘图时,分别采用了以下几种任务分配方法:

(1)DSP1(主DSP)绘制全部画面,DSP2(从DSP)空闲;

(2)DSP2(从DSP)绘制画面单元2(全罗盘),DSP1(主DSP)绘制其余全部画面;

(3)DSP2(从DSP)绘制画面单元2(全罗盘)和画面单元6(气压高度),DSP1(主DSP)绘制其余全部画面;

(4)DSP2(从DSP)绘制画面单元2(全罗盘)和画面单元3(静态背景画面),DSP1(主DSP)绘制其余全部画面;

(5)DSP2(从DSP)绘制画面单元2(全罗盘)和画面单元5(信息框文字),DSP1(主DSP)绘制其余全部画面;

(6)DSP2(从DSP)绘制画面单元2(全罗盘)、画面单元5(信息框文字)、画面单元4(顶部文字菜单),DSP1(主DSP)绘制其余全部画面;

(7)DSP2(从DSP)绘制画面单元2(全罗盘)、画面单元6(气压高度)、画面单元5(信息框文字)、画面单元4(顶部文字菜单),DSP1(主DSP)绘制其余全部画面。

3.2 系统同步策略

每帧画面计算显示之初,主DSP(DSP1)首先将画图任务分配结果发送给从DSP(DSP2),然后二者同时进行作图计算,DSP1的作图结果直接写入显存SDRAM,DSP2的作图计算结果暂时保存在内存缓冲区中,待作图完成后,通过LinkPort端口采用DMA方式发送给DSP1。DSP1收到DSP2的作图计算结果后,将计算结果写入SDRAM,然后通过改变通用输入输出引脚FLAG0的输出状态通知FPGA进行显存的刷新。

为了保证两个DSP的作图结果可以同步显示,主DSP在完成作图任务并将结果写入SDRAM后,必须等待接收从DSP的作图结果,确认收到后,才翻转FLAG0的状态开始启动画面显示,这样就可以保证DSP1和DSP2的画面可以同步显示。

3.3 软件设计流程

DSP1作为系统主DSP,首先需要通过判读通用输入输出引脚FLAG1的输入状态来确认FPGA已经完成SDRAM显存的刷新,然后才启动LinkDMA将预先分配好的任务发送给DSP2。DSP1发送完成后开始作图,DSP2接收到任务后也同时开始作图。待DSP1作图完成后,如果DSP2也已经作图完成并且已经将作图结果发回,则DSP1直接将数据写入显存,写完后将FLAG0的输出状态翻转使FPGA进入操作状态。双DSP并行图形处理与同步显示软件的流程图如图9所示。

图10为DSP1和DSP2在任务执行时时间分配的示意图。在软件执行过程中,DSP2任务分配的多少将会影响整幅画面的处理时间。如果DSP2的任务分配过少,主要的处理工作都由主DSP1完成,则系统总的处理时间减少并不明显;但如果DSP2任务分配过多,在DSP1完成作图任务后DSP2仍未完成,则DSP1的等待时间也会拉长画面整个处理时间。合理的任务分配应该使得DSP2在完成作图计算并将计算结果发回后,DSP1也正好画面处理结束,这时整幅画面的作图处理时间最短,作图效率最高。

实际应用时由于受到作图任务的限制,两个DSP的任务分配难以达到理想状态,但应该尽量保证二者时间上的并发性,以减少总的作图时间。

4 能效测算

在绘制1 024×768分辨率的典型画面时,两个DSP的系统输入时钟为125 MHz,内核时钟均为500 MHz。链路口时钟、SDRAM输入时钟均为125 MHz。

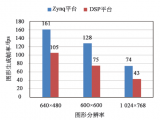

对3.1中所述的几种任务分配模式下双DSP的作图时间、帧率和系统功耗进行测试,结果如表1所示。

经过对比可以看出,在采用双DSP共同作图计算时,不同的任务分配情况,画面总的作图时间和系统功耗也有所不同。在分配的时间相对均匀条件下,双DSP并行处理比单个DSP单独处理效率提升53.6%,而功耗仅上升15.1%。

5 结论

本文针对传统的单DSP作图性能不足的问题,提出了一种双DSP并行作图解决方案,利用DSP间的Linkport端口传递作图参数和数据,并完成作图数据同步显示,结果显示,在采取有效的任务分配策略后,可以大幅地提高作图效率,减少系统绘图时间,而系统功耗增加并不明显。

电子发烧友App

电子发烧友App

评论