摘 要: 采用软件控制方式的道路交通信号机在死机时往往失去其绿冲突保护功能。根据“绿冲突矩阵”的检测原理,本文提出一种道路交通信号控制机的信号冲突检测方案,采用自顶向下的设计方法,通过FPGA实现系统的各个功能模块。该系统可以独立地检测绿灯信号冲突这种道路交通的异常情况,并能立即做出处理。仿真及实际测试结果表明,该系统时序分配与程序设计合理,工作稳定可靠,并能够提高信号机嵌入式系统的实时性。

0 引言

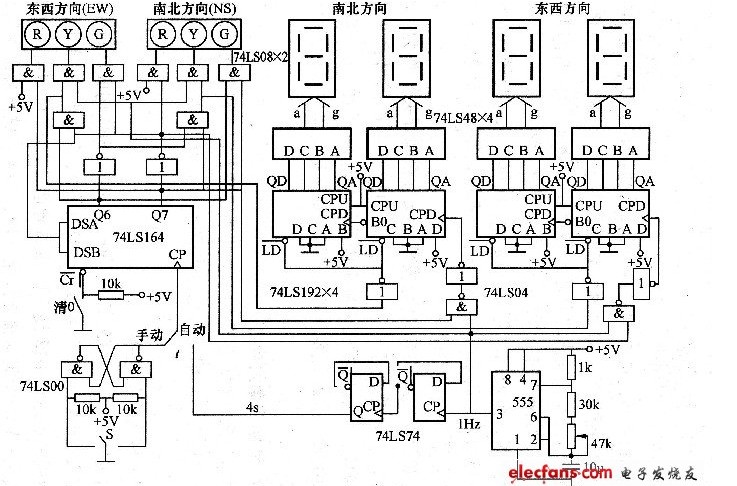

随着各国城市化进程的不断发展,智能交通系统在城市道路交通控制中得到了广泛的应用。智能道路交通信号机是智能交通系统的重要组成部分,也是解决城市交通问题的关键设备。信号机中的绿冲突检测可以提高智能交通系统的安全性和可靠性。由于过去的绿冲突保护控制方式相对简单,通常是用简单的继电器互锁或者信号灯的接线实现[1],随着多相位、多时段控制方式和线控、面控方式的发展,目前的绿冲突检测多通过信号机的控制软件实现。然而,当这类信号机出现死机导致信号冲突时,其保护功能就失效。因此研究一种新的绿冲突检测电路在智能交通控制中具有十分重要的现实意义。

本文研究的绿冲突检测电路采用FPGA实现。FPGA适合于组合逻辑和时序逻辑电路设计,并且具有并发执行的功能,相对于微控制器的程序设计更加稳定可靠[2]。同时,基于FPGA的绿冲突检测电路实现信号机的绿冲突检测功能,可以减轻信号机CPU的负担,提高系统的实时性。

1 绿冲突

绿冲突是指规定不允许同时放行的信号灯组中的绿色信号灯同时点亮[3]。就目前的交通信号控制机来说,产生绿冲突的原因大概有以下几类:

(1)系统软故障

此类绿冲突通常是由于交通信号机里面的控制系统出现死机或者是一些数据处理错误等软故障造成的。不仅如此,如果交通信号机在较为恶劣的电磁环境下工作,也会受到电磁干扰而出现短暂的绿冲突现象。

(2)硬件故障

由于信号机的硬件变质、损坏或者温度变化、受潮等原因造成的绿冲突。这种情况如果发生,就可能长时间持续下去,只能对信号机进行维修或者更换里面的部件[4-5]。

2 基于绿冲突矩阵的校验原理

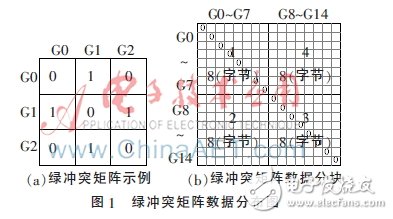

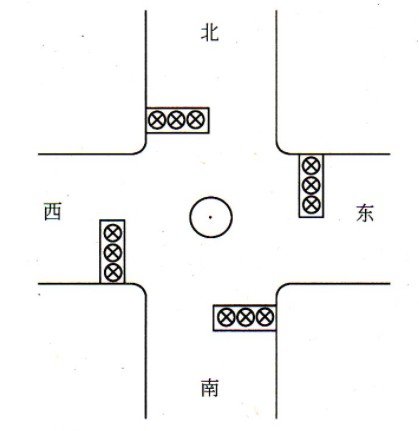

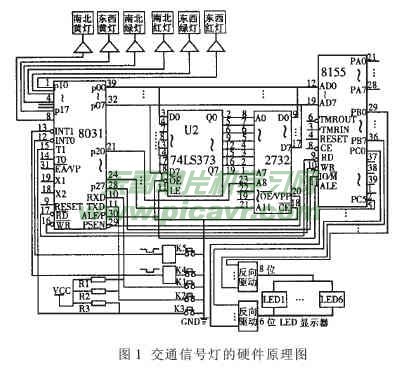

本文设计的绿冲突检测是基于绿冲突矩阵的检测原理,冲突矩阵的行和列分别对应一个信号灯组,为一对称矩阵,如图1所示。

在图1(a)中假设有G0、G1、G2三个绿灯信号,设G0和G1同时点亮视为冲突,G1和G2同时点亮视为冲突,则图中对应冲突的位置填入1,G0和G2同时点亮不视为冲突的位置填0,如图所示,本文称之为绿冲突矩阵数据,因此,绿冲突矩阵数据中的位信息1就是某绿灯对子不允许同时点亮的定义。校验过程如下:

当输入的信号为G0G1G2=010时(1表示绿灯亮,0表示绿灯灭):

(1)G0为0,不与G0所在的行校验,转下一行;

(2)G1为1,进行校验,将输入信号“010”与G1所在的行“101”相与,即010&101=0,数据正确;

(3)G2为0,同理不需要校验。

当G0G1G2=110,即G0和G1同时亮时,与G0所在行相与后结果非0,说明G0和G1信号冲突,此时,信号机应立即切断所有绿灯信号,转而执行黄闪信号。

本文设计的绿冲突检测电路对应15路绿灯信号G0~G14,如东西方向的直行绿灯、左转绿灯、右转绿灯、掉头绿灯、行人绿灯等。在本文中绿冲突矩阵数据是以字节为单位的,所以15路信号对应的绿冲突矩阵数据分成4块,每一块有8字节,按照图1(b)的编号顺序通过FPGA串口写进FPGA的ROM中。其中第一块数据用于校验G0~G7绿信号之间的冲突,第二块数据用于校验G8~G14与G0~G7绿信号之间的冲突,第三块数据用于校验G8~G14绿信号之间的冲突。第四块数据也是用于校验G8~G14与G0~G7绿信号之间的冲突,因此不需要写进ROM。在校验的过程中还应排除Gx与Gx自身的比对,如图1(b)中斜方向所示。

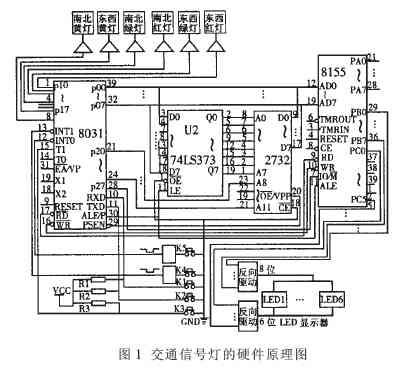

3 总体方案

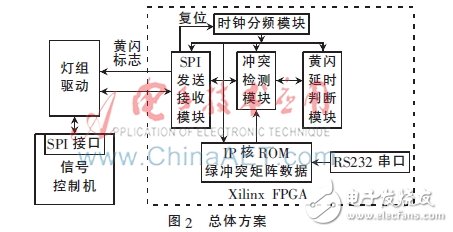

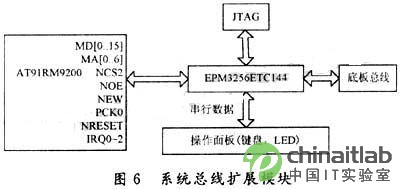

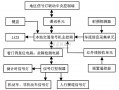

根据绿冲突矩阵的检测原理,采用自顶向下的设计方法将检测电路分为以下几个模块:(1)信号灯的灯组驱动电路,通过SPI方式在正常状态下接收信号控制机的灯组数据,在黄闪状态下接收冲突检测电路发送的信号灯黄闪数据。(2)冲突检测电路采用Xilinx的FPGA芯片XC3S50,通过SPI模块接收信号灯的状态数据。(3)数据接收结束后复位时钟分频模块,时钟分频模块产生其他模块所需时钟,所有模块都是在统一的时钟线上运行,以免发生时序混乱。(4)冲突检测模块,在检测时序期间对SPI接收的数据即信号灯的状态数据进行绿冲突校验,校验是根据上文所说的绿冲突矩阵比对各绿灯信号状态,该绿冲突矩阵数据存放在FPGA的IP核所生成的ROM里面。(5)黄闪延时判断模块,冲突检测模块的检测结果经过黄闪延时判断模块进行延时检测并确认是否有冲突。如果没有冲突,则灯组驱动继续接收信号控制机的灯组数据;如果有冲突,则黄闪标志置位,切断MCU的SPI通道,冲突检测电路通过SPI开始发送黄闪数据至灯组驱动,从而让灯组驱动切换至黄闪状态。总体方案如图2所示。

4 各模块设计

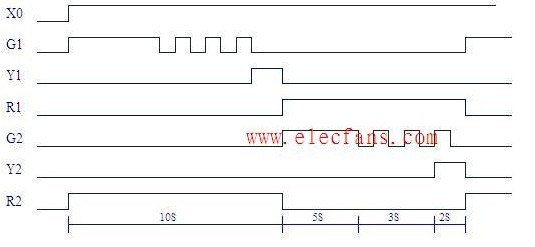

4.1 SPI模块

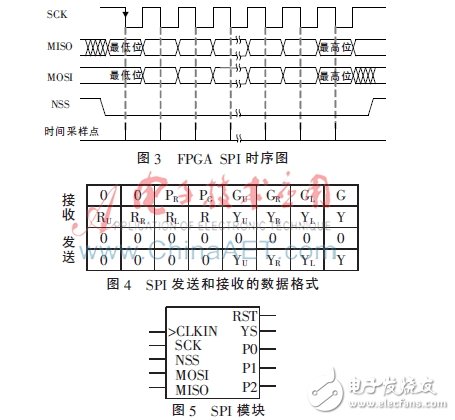

SPI协议(Serial Peripheral Interface),即串行外围设备接口,是一种高速全双工的通信总线。SPI总线包含4条总线,分别为NSS、SCK、MOSI、MISO,FPGA SPI时序如图3所示。从图中可以看出,FPGA在时钟的下降沿采集灯组的数据,在上升沿发送数据。数据的传输是从低位开始,接收的灯组信号存到三组16位寄存器P0、P1、P2。P0、P1、P2的数据格式一样,如图4所示,分别表示不同的道路方向。G是绿灯信号,Y是黄灯信号,R是红灯信号,下标表示不同的形式,如左转、右转等。另有一组4位的寄存器YS用于存放黄闪数据,当处于黄闪状态时,YS寄存器的值以时钟分频模块控制的时钟频率进行0/1交替改变,并通过SPI发送至灯组驱动,从而控制灯组驱动进入黄闪状态,SPI模块如图5所示。

4.2 时钟分频模块

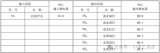

时钟分频模块相当于整个电路的驱动模块,所有冲突检测模块都是在时钟分频模块提供的时钟下工作。如图6所示,输入的系统时钟CLKIN被分频为BUSY、CHCK、ADR3、ADR2、ADR1、ADR0,频率为62.5 Hz~2 kHz。分频器是通过计数器实现的,计数的方式如式(1)所示[6],当计数到波形翻转时间点时将波形输出取反。BUSY和CHCK的功能如表1所示,当BUSY为1时,冲突检测电路通过SPI开始接收灯组状态数据,如果处于黄闪状态,则同时发送黄闪数据。ADR3~ADR0是ROM校验表的地址,可以寻址16个16位绿冲突矩阵数据。CLK4HZ是黄灯闪烁的频率,RD信号是ROM的读数据信号,频率是4 kHz。由于RD读信号和ADR地址信号不能同时跳变,否则数据将会不稳定,从而读不到正确的数据,因此需要将RD信号与ADR0的地址错开,如图7所示,程序设计是通过16 kHz时钟分频得到4 kHz,但是在复位时计数器从1开始计数,最后将4 kHz取反后输出到RD信号。

4.3 冲突检测模块

绿冲突检测模块是本文设计的核心模块,其检测周期定为4 ms。在检测周期开始时,先将P0、P1、P2三灯组中的15路绿灯信号读入8位寄存器G_SIG0、G_SIG1,其位置排列如图8所示。绿冲突检测就是寻找绿冲突矩阵数据中定义的同时点亮的绿灯对子,如果找到一个或一个以上的对子就判定发生了绿冲突。因此,寻找过程就是一个循环处理过程。首先判断G_SIG0或G_SIG1中的i位是否为1(i为0~14),如果i为1,说明i位的绿灯亮;其次,把G_SIG0或G_SIG1中的i位值清零。i位清零后,如果G_SIG0或G_SIG1中的值不为零,说明有与Gi成对的绿灯对子存在。把这个数值与绿冲突矩阵数据中Gi对应的数据相与,若结果不为零,说明有与Gi成对但不允许同时点亮的绿灯对子存在,即存在绿冲突,循环处理结束,准备输出黄闪。如果结果为零,i加1,进行下一轮比对处理。

按照冲突矩阵的数据格式,需将G0~G15分别与第2节中描述的绿冲突矩阵数据的三块数据进行校验,FPGA程序设计如图9所示。在每次读信号到来时,FPGA读入2字节数据,随后地址信号ADR加1计数,地址ADR 0~3的区域为第一块数据,4~7的区域为第二块数据,8~11的区域为第三块数据。在满足时序(BUSY为0,CHCK为1)与不黄闪的条件下,读入的第一块数据用于绿灯状态G0~G7与自身的比对,第二块数据用于绿灯状态G0~G7与绿灯状态G8~G14的比对,第三块数据用于绿灯状态G8~G14与自身的比对。如果比对处理结果判定为绿冲突,则将绿冲突临时标志置1,否则将临时标志清0。

4.4 黄闪延时判断模块

当信号灯闪烁时,每隔250 ms就要改变一次状态,即0和1的交替变化,这样冲突临时标志必然也会变化,从而导致错误判断。因此需要加入延时判断,在BUSY上跳变的时候对临时标志进行判断,若是1则计数器累积加1,否则清0计数器。当累计到19时(BUSY周期16 ms,即计数时间超过300 ms),才可确认为冲突信号,触发黄闪信号,程序如图10所示。

延时判断必须在临时标志被清0之前,从图11的时序图中可以看出,临时标志位变化是在BUSY上升沿之前,清0在BUSY上升沿之后,因此延时判断的触发信号为BUSY的上升沿。

4.5 其他模块

实际上,信号冲突检测电路还包括红绿冲突检测、红灯灭与绿灯灭检测电路,这些电路在逻辑上相对简单,本文不做描述。另外,利用Xilinx FPGA的IP核生成的ROM模块以及RS232串口模块在本文所列出的相关参考文献中有详细的介绍,这里也不再描述[7-8]。

5 仿真与测试

通过Xilinx的ISE开发软件编写Test Fixture测试文件对各个模块进行仿真测试,查看各个模块的波形时序正确后,对顶层模块进行整体仿真。仿真结果表明,本设计时序逻辑正确,当2个灯组的绿灯状态违反绿冲突矩阵数据定义时能正确检测出冲突,进而进入黄闪。最后利用STM32主控板和FPGA开发板以及自己焊接的LED信号灯电路对程序进行实际验证测试,如图12所示。测试表明,信号灯在没有冲突的时候能正常运行,冲突时则进入黄闪状态。

6 结论

本文详细介绍了基于FPGA的绿冲突检测电路各个模块的原理与设计,经过严密的时序分析以及Verilog语言编程,实现了各个模块的基本功能,并通过了功能仿真与实际的硬件测试。结果表明该系统可以正确检测出各种绿信号冲突并立即做出处理,使得智能交通系统更加安全可靠。利用FPGA设计的功能模块经过编译后生成实际的时序逻辑电路,更加稳定可靠,而且后期还可以进行功能更改与完善,方便维护。

电子发烧友App

电子发烧友App

评论