802.11应用架构根据IEEE 802.11无线标准,提供了立即可用、方便修改的实时正交频分复用(OFDM)物理层(PHY)和底层媒体访问控制层(MAC)参考设计。 802.11应用架构包含于LabVIEW Communications系统设计套件(简称 LabVIEW Communications)中。

这个架构提供了良好的开发起点,帮助研究人员探索全新的算法和架构来支持大幅增长的端点数量、发明新波形来调制/解调信号或寻找全新的多天线架构来充分运用无线媒介的自由度,进而找到改良802.11标准的方式。

802.11应用架构包含了使用LabVIEW Communications开发的PHY块和MAC块。 该框架搭载了强大的Xilinx Kintex-7 FPGA平台与Intel x64通用处理器,这两者皆可紧密集成NI软件无线电(SDR)硬件的RF和模拟前端装置。

我们完全重新设计了这个框架,使用户可以轻松对其进行修改,同时遵循802.11标准的主要规范。 这种设计可让无线研究人员根据802.11标准快速搭建实时原型开发实验室并开始运行。 他们还可以专心改良特定的系统项目、轻松修改设计以及将其创新与现有标准进行比较。

1. 范围和标准遵循

802.11应用架构提供了单个站点的功能,包含接收(RX)与发射(TX)功能,并使用OFDM作为核心数字调制机制。 OFDM适用于复杂度低的多功能PHY实现,并且可减缓宽频无线信道的离散效应。 OFDM采用快速傅立叶变换(FFT)和快速傅立叶逆变换(IFFT)来实现发射机与接收机的频域PHY处理。 通过在频域上处理数据,OFDM可有效地让PHY通过通信频谱的平行窄频区段来传输数据。 由于减缓信道离散只需要针对每个区段进行一次数学运算,所以通过窄频区段来执行数据传输是相当理想的做法。

以下各部分介绍了所提供的PHY与底层MAC功能以及所遵循的802.11标准。

1.1

PHY层

802.11应用架构提供了下列PHY发射机功能:

加密

卷积编码和位交织

导频序列生成

BPSK/QAM星座映射器

信号字段生成

通过IFFT生成OFDM码元

循环前缀(CP)插入

前导码字段补充

为接收机端提供了特定函数对应的补充功能:

数据包检测

时间和频率同步

自动增益控制

信号字段检测

循环前缀去除

通过FFT解调OFDM码元

信道估算和迫零均衡

BPSK/QAM解调

基于维特比译码器的卷积译码(包括分选)

解密

802.11应用架构可支持IEEE标准所规定的不同OFDM配置。 版本1.0可支持20 MHz a/g和20 MHz n/ac这两种副载波格式,具体特性如下:

系统带宽: 20 MHz

副载波频宽: 每个副载波(窄频区段)占用312.5 kHz

副载波分配

. 20 MHz a/g: 分配53个连续副载波(载波频率的中央(第27个)副载波)

. 20 MHz n/ac: 分配57个连续副载波(载波频率的中央(第29)副载波)

零位中央副载波: 中央副载波通过归零可避免本地振荡器出现基带馈通。

导频副载波可允许接收机补偿残留的频率同步失配和相位漂移:

. 20 MHz a/g: 53个副载波中有4个是导频副载波

. 20 MHz n/ac: 57个副载波中有4个是导频副载波

发射机每个IFFT输出字段前面都会有800 ns的循环前缀,可保留接收器端的循环卷积,避免码元之间相互干扰。所以每个OFDM码元可用来传输数据的副载波数量如下:

. 20 MHz a/g: 48个副载波

. 20 MHz n/ac: 52个副载波

这样一来,对于20 MHz的信道分配而言,48 * 312.5 kHz = 15 MHz,52 * 312.5 kHz = 16.25 MHz。 这两个频谱数量分别对应20 MHz a/g和20 MHz n/ac模式的数据。

802.11应用架构采用简化的PHY帧格式。 图1为已实现的格式。

图1. 一般的PHY架构格式

PHY架构包含以下字段:

传统模式的短训练字段(Legacy mode short training field, L-STF) - 用于接收机端的增益控制、数据包检测、频率同步的静态字段。 字段时间长度为8 ?s。

传统模式的长训导字段( Legacy mode long training field,L-LTF) - 用于时间同步与信道估算的静态字段。 字段时间长度为8 ?s。

传统模式的信号字段(Legacy mode signal field, L-SIG)- 包含已应用的调制编码机制(MCS)和框架长度等信息的动态字段。

超高吞吐量短训练字段(Very high throughput short training field, VHT-STF):用于超高吞吐量模式802.11ac的静态字段。 目前的接收机实现方案往往忽视了VHT-STF字段,仅评估L-LTF字段。

超高吞吐量长训练字段(Very high throughput long training field, VHT-LTF):用于超高吞吐量模式802.11ac的静态字段。 目前的接收机实现方案往往忽视了VHT-LTF字段,仅评估L-LTF字段。

负载(PAYLOAD)属于动态字段,仅由MAC消息定义。 负载的长度取决于信号传输调制机制。 最长的负载采用二进制相位位移键控(BPSK)机制。 最短的负载则采用64-QAM机制。

上述的框架格式符合IEEE 802.11ac规范,但是并未提供超高吞吐量信号字段(High Throughput Signal Field,VHT-SIG-A 或 VHT-SIG-B)。

1.2

媒体访问控制(MAC)层

802.11应用架构提供了下列MAC发射机功能:

. DATA PDU生成,包括添加地址信息

. 帧检验序列(Frame check sequence, FCS)生成

. ACK PDU生成

以下功能适用于接收机端:

. 帧检验序列(Frame check sequence, FCS)检验

. ACK PDU传输的地址检验和触发

. MAC SDU提取

802.11应用架构针对MAC PDU采用了一个简化的框架结构。 图2显示的是用于数据和ACK帧的数据包结构。

图2.MAC PDU帧结构

MAC PDU帧的第一个字段是TYPE字段,占用了一个字节。 接收机根据该字段判断要解码的MAC PDU帧。 802.11应用架构中,TYPE只有两种类型: DATA(0x08)和ACK(0xD4)。 未来应用架构可能会包含更多类型。 MAC数据包中第二和第三个字段长度均是6个字节,分别代表目标的MAC位址和来源的MAC位址。 MAC数据包的第四个字段是MESSAGE字段, 其中包含来自更高层协议的所有数据,通过无线链路进行传输。 MAC数据包的第五个字段是CRC32字段, 长度为4个字节,由FPGA的CRC32模块生成,附加到每个信息上以便检错。

1.3 遵循IEEE 802.11标准

802.11应用架构遵循一部分特定的IEEE 802.11标准。选择特定支持功能的原因在于尽可能简化代码以便修改,同时遵循802.11标准的主要架构。

除了上述的简化数据包格式之外,以下是其他固定或简化的设置和步骤,有助于降低应用架构的复杂度:

仅支持单一输入/输出(SISO)传输模式

仅限BPSK、QPSK、16 QAM和64 QAM调制与编码机制(MCS)

专用交错复用器

专用SIFS时序

简化的自动增益控制(AGC):802.11应用架构提供简化的AGC机制。 其中一部分在主机上实现,所以需要较长的调整时间。 AGC循环必须接收多个数据包才能计算并设置正确的增益值。

2. 实现概述

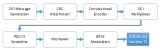

由于802.11系统的延迟要求,大多数区块都会在FPGA上实现。 不需要实时执行功能和FPGA初始化与控制功能的特性都在主机处理器上实现。 发射器和接收器实现方式分别如图3和图4所示,其中显示了主机-FPGA的分区。

图3.发射器示意图

就发射器端而言,主机会把读取自UDP插槽的用户数据传输至FPGA。 也可选择使用随机产生的数据包。 主机代码会显示输入控件,以便设置参数,例如调制和编码机制。 然后在FPGA上应用这些参数来执行基带与RF处理。 FPGA上的信号处理还包含了PHY帧合成、OFDM调制和转换至模拟信号。

图4.接收器示意图

在接收器端,FPGA会执行所有的基带运算以便接收并解码信号,例如数据包检测和同步化、OFDM解调制、信道估算和均衡以及解码等。 解码后的数据传输至主机。 主机可能会随意把接收到的数据写入UDP socket。 此外,FPGA会把额外的数据(例如所接收的I/Q样本和所检测的数据包解调后的I/Q星座图)传输至主机。 额外数据可用于记录调试日志,也可用于显示频谱或接收到的星座图。

第三小节提供更多FPGA的实现信息,第四小节则阐述了主机实现。

3. FPGA实现

3.1 概述

FPGA顶层实现了下列功能:

状态机和常规配置

发送处理

接收处理

射频处理

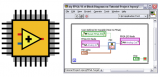

代表这些功能的元素会放在FPGA顶层架构图中,分成四栏,如图5所示。 每栏皆包含多个循环;所以举例来说,最左栏是一个状态机器处理循环、一个主机寄存器配置循环和一个收发器初始化循环。

图 5. FPGA顶层示意图

3.2小节会进一步解释状态机。 3.3和3.5小节会分别阐述发射器和接收器。 如需了解更多射频处理细节,请查看3.4小节。

主机寄存器配置(Host Register Configuration)循环负责执行过程中主机的配置参数更改。 这些更改可能包含调制和编码机制、设备MAC位址和副载波格式等信息。 该循环会生成FPGA的相关配置,例如数据副载波的数量和每个QAM码元的比特数。

收发器初始化(Transceiver Initialization)循环是当前实现的一个占位(placeholder)符,可用于在整个收发器开始运行前进行常规配置和初始化。

3.2 状态机

为了控制PHY处理功能以便收发数据包,FPGA上实现了下列三个状态机:

收发器状态机(Transceiver state machine):协调发射器与接收器状态机的顺序运行。

发射器状态机(Transmitter state machine):协调发射器的运行。

接收器状态机(Receiver state machine):协调接收器的运行,包含数据包检测与同步。

图6显示了FPGA顶层状态机循环内的状态机位置。

图6.状态机循环内的状态机位置

3.2.1 收发器状态机

收发器状态机有四个状态,可在发射器和接收器之间进行协调。 请注意,802.11接收器的默认状态是数据包侦听。 因此,收发器默认的idle状态对应至接收器的detect状态。如果发现数据包前导码,收发器就会变成rx状态,直到数据包解码完成为止。 一旦有能够传输的数据包,同时状态机处于idle状态 (也就是接收器则处于detect状态)时,收发器会迅速切换至发射状态。

状态

说明

备注

init

此状态表示收发器首次启动。

?

idle

接收器正在侦听数据包。

?

tx

发射器正在生成数据包。

?

rx

接收器正在同步或解码数据包。

?

3.2.2 发射器状态机

发射器状态机有五个状态,如下表所示。

状态

说明

备注

idle

发射器正在等待数据发送。

为了快速启动发送操作,L-STF和L-LTF预先计算的样本已经写入重采样FIFO。 如需更多信息,请查看3.3.3小节。

SIGNAL copy

生成信号字段并复制到重采样FIFO。

收发器必须处于idle状态才能进入此状态。

?VHT copy

超高吞吐量(Very high throughput, VHT)前导码会复制到重采样FIFO。

?

PAYLOAD copy

生成数据负载字段并复制到重采样FIFO。

?

finish

重新设置发射器。

3.2.3 接收器状态机

接收器状态机有五个状态,如下表所示。

状态

说明

备注

idle

接收器正在等待数据包检测初始化。

?

detect

接收器正在侦听数据包(数据包检测模式)。

收发器必须处于idle状态才能进入此状态。

sync

接收器与检测到的数据包进行同步。

收发器必须处于tx状态才能进入此状态。

decode

接收器正在处理接收到的数据包。

?

finish

接收器已完成数据包接收

?

3.3 发射器

3.3.1 概述

发射器会分成三个循环,如图7所示。

TX MAC + PHY循环会读取主机所提供的数据,并且构建MAC PDU数据包,如1.2节所述。 接着MAC PDU数据包的比特会经过信道编码,并且以80 MS/s的采样率生成复数值的基带样本。

Copy TX data sources循环会通过添加丢失的信号字段来构建PHY帧格式,如1.1节所述。

TX sample interpolation循环会把I/Q基带样本的采样率从80 MS/s转换为120 MS/s,以便满足DAC的要求。

下面几节将会进一步介绍这些循环。

图 7. 发射器循环

3.3.2 发射器MAC+PHY的循环

TX MAC+PHY Loop的输入与输出如8所示。主机数据通过一个称为TX:PacketBytes的直接内存访问Host-to-Target FIFO提供。 另一个Host-to-Target FIFO称为TX:NumPacketBytes,可提供要读取的字节数的控制信息。 TX:PacketBytes所提供的数据包含目标MAC位址和MAC SDU负载。

图 8. 发射器MAC + PHY循环的输入与输出

Format MPDU Bits区块会根据消息信息和设备配置生成剩余字段,主要是插入1个字节的TYPE字段和6个字节的SRC-MAC字段,并且附加一个4字节的CRC32字段。 所获得的MAC PDU帧如图2的结构所示。如果要进行调试,此帧也通过TX: PHYIn target-to-host FIFO写入主机。

下一个区块叫做TX PHY TOP,包含了信道编码和基带调制处理,如图9所示。

图 9. TX PHY Top的程序框图

Format PPDU Bits区块可执行两项操作:

1、附加于L-SIG字段前方,L-SIG字段包含PSDU比特数量、每个数据副载波的比特(也就是调制机制)和编码率。

2、补充填充位,这样一来数据包就可以匹配特定QAM星座图中OFDM码元的比特位界限。 举例来说,通过64-QAM编码而成(每个码元6位)且长度为168字节的消息(由MAC PDU、服务位和尾位组成)会以224QAM码元来表示。 如果每个OFDM码元有48个数据副载波并且使用a/g模式时,下一个可用的界限就是240 QAM码元。 相差16个码元意味着需要补充96个填充位。

MAC格式化区块完成之后,PHY帧就可以准备执行信道编码。 这些比特会进行加密,通过二进制卷积码(Binary Convolutional Code, BCC)完成交错编码。 要使用的BCC速率取决于调制与编码机制(MCS),这一机制由主机提供并用于传输数据数据包。 ACK数据包一律采用MCS 0来传输。

交错的比特会映射至QAM U8码元索引(而不是复合的基带样本)。 这些码元索引可简化QAM码元的表示,有助于减少码元映射器的内存占用。 生成码元索引后,QAM码元就会映射至副载波结构,如1.1小节所示。 副载波会根据每个OFDM码元以正确的顺序排列,零子载波则会在中心频率下插入。 零子载波也会插入到频带边缘,以确保有效的FFT变换。

完成子载波格式化之后,QAM码元索引就会映射至复数基带(同相和正交)样本。 IFFT区块会把频域I/Q样本转换至时域I/Q样本。 发射器和接收器的FFT大小都是256,有助于轻松扩展带宽。 IFFT也会插入循环前缀,长度为64个样本。 这样一来,每个OFDM码元就会有320个样本,由于802.11标准的OFDM码元持续时间为4ms,采样率就等于80 MS/s。

3.3.3 复制传输数据源(Copying Transmit Data Sources)循环

如图10的循环所示,不同TX数据源的复数值基带样本会通过多个路径进行传输,最终生成一个802.11 PHY帧,如1.1小节所述。 不同训练字段的复数值基带样本,也就是L-STF、L-LTF、VHT-STF和VHT-LTF,都会经过预计算并储存至ROM表格。

图 10. 复制传输数据源循环的输入与输出

3.3.4 内插发射器样本(Transmit Sample Interpolation)循环

图11所示的循环把采样率从80 MS/s转换为120 MS/s,也就是NI USRP默认的DAC采样率。 基本上,采样率转换是使用一个2:3内插器完成的。 如果要进行调试,可以使用目标至主机的DMA FIFO,也就是TX:PacketDebug,以80 MS/s的采样率访问802.11帧的复数值基带样本。

图 11. 内插发射器样本循环的输入与输出

3.4 RF处理

RF处理循环是从NI USRP Streaming Sample Project中截取出来的。 如需深入了解RF处理循环,请查看NI USRP Streaming Sample Project文档。 ADC和DAC处理循环已针对802.11应用架构进行了简化与调整。除了项目范例之外,RF0和RF1发射端口1与接收端口1和2的启用/禁用是由主循环控制,而非RF配置开关(RF Configuration Switches)循环。

图 12. FPGA顶层的ADC/DAC处理

图12显示了802.11应用架构FPGA顶层DAC/ADC界面循环的原理图。 此循环包含DAC与ADC界面以及必要的处理功能,可用于接收基带信号并将基带信号进行转换以便传输。

数字增益、频移和I/Q减损补偿都会在TX信号传输至NI USRP DAC之前应用到信号中。 发射信号的数字I/Q样本会通过FIFO(TX:PreDAC)进入循环。

在接收器端,NI USRP ADC的数据经读取之后进入接收信号处理程序,以修正I/Q减损与频移。 然后I/Q样本会通过FIFO (RX:PostADC)传输至下一个处理循环。

使用内部的环回模式可跳过RF处理程序。 一旦启动RF处理,TX数据就会直接进入RX处理链。

3.5 接收器

3.5.1 概述

接收器分成三个循环,如图13所示。

1、RX采样抽取循环(RX Sample Decimation Loop)会抽取来自ADC的RX样本,以尽量达到理想的I/Q采样率,也就是80 MS/s。

2、RX同步循环(RX Sync Loop)负责完成数据包检测、时间与频率同步和循环前缀消除。

3、RX MAC + PHY循环则会执行PHY层的信道估算、均衡、OFDM解调与解码以及MAC层的CRC与地址检查。

图13.接收器循环

下面将进一步讨论上述三个循环。

3.5.2 接收器采样抽取(Receiver Sample Decimation)循环

图14为接收器采样抽取循环,用于转换采样率。 和DAC一样,ADC的工作频率为120 MS/s。和发射器一样,接收器的处理频率为80MS/s。所以需要使用一个3:2抽取器来连接ADC和FPGA上的接收器处理。

图 14. RX采样抽取循环的输入和输出

3.5.3 接收器同步(Receiver Synchronization)循环

图15显示了接收器同步循环的界面,图16则是同步的程序框图。

图 15. 接收器同步循环的输入与输出

图 16. TX PHY Top的程序框图

重采样之后,开始进行基于L-STF架构的同步。 该过程以Schmidl-Cox算法为基础。

同步单元内的第一个模块会计算样本的自动关联。 计算自动关联所使用的时间延迟以L-STF序列的周期性为基础。 这个数据会进一步转换成能量归一化和平均的关联指标。 输出端处也会计算平均载波频率偏置(Carrier Frequency Offset, CFO)估算序列。 后续模块会使用这些输出来生成和CFO估算值。

下一个模块会完成L-STF同步的第二个步骤。 收到数据包后,第一个模块输出端的关联指标就会在高数值(代表L-STF字段)和低数值(代表移至先前的L-STF字段)之间转换。 该模块实现了一个差分器,可以把向下斜率转换至峰值。 所产生的信号就会成为代码中的关联差异指标,该值也就是时序同步的指标。

第三个模块用于判定是否已检测到某个数据包。 一旦收到一个结构完整的802.11数据包,第二个模块算出的关联差异指标就会显示一个峰值,对应于L-STF和L-LTF之间的转换值。 阈值检测可以在L-STF结尾和L-LTF开头估算此位置,从而实现粗同步(在一个循环前缀内完成)。如果峰值在超过特定数量的连续样本内保持在特定的阈值以上,此模块就会判定检测到802.11前导码,并通过STF Found指示控件表示。

检测到数据包之后,下一个模块就会补偿所有算法与实现延迟,将基于传统短训练字段(L-STF)的同步信号与抽取的I/Q样本与CFO估算序列(由第一个模块计算而得)进行对齐。 CFO估算会根据CFO估算序列和STF Found指示控件进行锁存。 LTF字段第一个(估算的)元素之前的数据样本会标示为无效。 这些数据流会发送至下一个模块,也就是信道频率偏置(CFO)修正模块,以消除相邻样本之间累积起来的相位差。

下一个模块OFDM选通器(OFDM strober)从估算的L-LTF第一个码元开始。在每个OFDM码元中,循环前缀(CP)样本会标示为无效,从而消除CP。 选通功能一直持续到数据包中估算的所有OFDM码元完成CP消除为止。 请注意,OFDM码元的数量在传统信号(L-SIG)字段中进行编码,之后L-SIG会在接收链中完成解码。

3.5.4 Receiver PHY+MAC循环

图17显示了Receiver PHY+MAC循环界面,图18显示了RX PHY Top和 RX MAC Top的程序框图。

图 17. Receiver PHY+MAC循环的输入与输出

处理链内第一个模块就是FFT。 FFT会将所有有效的样本转换至频域,逐个OFDM码元地进行。

下一个模块会处理副载波域的LTF码元,以获得信道响应的近似值来进行后续的迫零信道均衡。 该估算值会映射至两个分量: 反向通道幅值和单位信道估算值。 使用这些分量即可降低均衡所需的位精确度。

基于信道估算,下一个模块会通过迫零运算来均衡802.11 OFDM码元。 完成均衡之后,即可通过导频信号评估来消除每个OFDM码元中的残留CFO和相位漂移。

图18: RX PHY Top和RX MAC Top程序框图

完成相位修正之后,接收到的样本就会进入OFDM反格式化器来移除所有的零子载波和导频副载波,并在发射器的格式化器之前以相同的顺序重新排列数据副载波。 这个反格式化器的输出端提供了I/Q星座图,可以传输至主机进行分析并调试。

进行反格式化之后,就会从QAM星座图提取比特数据,并且去除交错配置。 去交错的比特流会进入Viterbi解码器进行信道解码。

下一个模块会解码并解读L-SIG字段。 其中包含PHY参数,可能会随着每个数据包而有所差异,例如调制与编码机制(MCS)和数据包路径。 接收器PHY区块会在处理链的前几个阶段使用此信息,例如同步单元(如3.5.3小节所述)末端的OFDM选通模块以及本小节的大部分区块。 根据L-SIG估算的参数值可通过这些区块的反馈路径来提供。 代码设计可确保参数会根据这些数值正确更新。 举例来说,对于每个数据包,L-SIG会使用已知的MCS(BPSK,速率-1/2代码)来发送。 参数必须根据L-SIG的估算值进行更新,并且应用至数据负载内的OFDM码元。

最后,解码后的比特经过解密转送至MAC。

MAC端会根据MAC PDU所包含的四个FCS字节执行CRC检查。 之后会检查Type字段,以判断是否接收到DATA数据包或ACK数据包。 然后将接收数据包的目标地址与站点的设备地址进行对比检查。 如果CRC检查和地址检查通过的话,就会把接收到的数据包显示给主机。 如果是DATA数据包的话,接收和提取的MAC SDU位字节加上源位址会通过target-to-host DMA FIFO RX: PacketBytes一同发送至主机。 接收到的数据包的大小也会通过target-to-host DMA FIFO RX: NumPacketBytes提供给主机。

4. 主机实现

802.11应用架构包含了一个顶层主机.gvi,用于配置FPGA、与FPGA交换负载数据以及监控系统状态。

左上方的指示控件和输入控件均已初始化。 之后就会生成一个会话,其中包含所有必要处理的参考信息。 所有循环在执行期间都会使用这个会话簇来交换数据或访问FPGA资源。 只要按下停止(Stop)按钮或出现错误,所有的While循环都会停止运行,会话中的所有处理操作都会关闭。

可能的参数设置请查看项目的文档。

图19. Host Top-Level VI程序框图

4.1 主循环

此循环会根据主机前面板的当前设置来配置FPGA。 循环会将发射队列(Transmit Queue)的数据传输至FPGA发射器,并把FPGA接收器的解码数据放入接收队列(Receive Queue)。 如果系统不是在RF环回模式运行,就会忽略发射或接收部分。 主循环还会进一步更新主机前面板的显示项目,以反映当前的系统状态。

4.2 自动增益控制

主循环会连续监控所收到的信号功率,并且相应地调整RX路径的增益。

4.3 RF与802.11 IP配置

此循环用于设置频率、功率电平和增益,可针对发射器和接收器配置NI USRP RF前端装置。 此外还会更新前面板来显示目前的RF状态。

4.4 吞吐量测量

数据通过UDP送出去时,此循环就会监控接收器端的吞吐量。

4.5 UDP数据读写

一旦启用上循环,即可处理接收队列的数据,并且通过UDP将数据发送出去。 下循环可以把随机数据的常数数据包(PN模式)或接收到的UDP数据包(UDP 模式)放入发射队列。 主循环会使用这两个队列来与FPGA交换数据。

4.6 停止执行

执行主机VI时,所有循环都会并行运行。 只要按下停止(Stop)按钮,该操作就会在最后一个循环被捕获,同时通过其他队列同步至所有其他循环。 每个循环都包含连接至循环条件终端的检错停止(check stop)模块,如果按下停止按钮或出现错误,就会退出该循环。

5. 结论

LabVIEW Communications 802.11应用架构1.0提供了两个在NI SDR硬件上运行的站点之间的实时802.11链路。此应用架构通过利用现有链路和只需修改或添加所需部分,可帮助用户专心于特定领域的研究。

基于LabVIEW的灵活性和该框架的模块化特性,用户可轻松互换设计的某些部分,以便针对未来的无线系统开发新的算法。除此之外,由于LabVIEW固有地连接了主机和FPGA,设计还可进行分区,以便充分利用FPGA的并行执行功能和主机的计算性能。

这个架构为无线研究和原型开发提供了丰富的起点。 立即下载LabVIEW Communications评估版: ,开始您的开发。

如有问题, 请发送电子邮件至 labview.communications@ni.com 。

6. 缩略词表

ACK

Acknowledge(确认)

AGC

Automatic Gain Control(自动增益控制)

BCC

Binary Convolutional Code(二进制卷积码)

BPSK

Binary Phase Shift Keying(二进制相移键控)

CP

Cyclic Prefix(循环前缀)

CRC

Cyclic Redundancy Check(循环冗余校验码)

DMA

Direct Memory Access(直接内存访问)

FCS

Frame Check Sequence(帧校验序列)

FFT

Fast Fourier Transform(快速傅立叶变换)

FIFO

First In First Out(先进先出)

FPGA

Field Programmable Gate Arrays(现场可编程门阵列)

GVI

Graphical Virtual Instrument(图形化虚拟仪器)

IEEE

Institute of Electrical and Electronics Engineers(电气电子工程师协会)

IFFT

Inverse Fast Fourier Transform(快速傅立叶逆变换)

I/Q

Inphase/Quadrature(同相/正交)

ISI

Intersymbol Interference(码间干扰)

L-LTF

Legacy Long Training Field(传统长训练字段)

LSB

Least Significant Bit(最低有效位)

LTF

Long Training Field(长训练字段)

L-SIG

Legacy Signal Field(传统信号字段)

L-STF

Legacy Short Training Field(传统短训练字段)

MAC

Medium Access Control(媒体访问控制)

MCS

Modulation and Coding Scheme(调制和编码机制)

MS/s

Mega Samples Per Second(每秒兆次采样)

OFDM

Orthogonal Frequency Division Multiplexing(正交频分复用)

PDU

Protocol Data Unit(协议数据单元)

PHY

Physical Layer(物理层)

QAM

Quadrature Amplitude Modulation(正交调幅)

QPSK

Quaternary Phase Shift Keying(四进制相移键控)

RX

Receiver(接收器)

SDR

Software Defined Radio(软件无线电)

SDU

Service Data Unit(服务数据单元)

SIFS

Short Inter Frame Space(短帧帧间间隔)

SISO

Single Input Single Output(单输入单输出)

STF

Short Training Field(短训练字段)

TX

Transmitter(发射器)

UDP

User Datagram Protocol(用户数据报协议)

VHT

Very High Throughput(超高吞吐量)

查看802.11应用架构的价格信息

查看LabVIEW Communications系统设计套件的价格信息

电子发烧友App

电子发烧友App

评论