给大家介绍菜鸟的第一款武器。xilinx ISE开发套件。

武器介绍:

名称:ISE Design Suite 14.7

功能:xilinx 系列FPGA开发的必备武器,属于基本套装。用此武器利用verilog或VHDL编写代码,能实现高能爆发能量。

武力:9星。

推荐等级: 10级(菜鸟必备)

备注:本版本开发套件,为xilinx公司ise产品最后一个版本。优点多多,BUG也多多。

获取方法:在xilinx官网上可以下载

装备方法:和普通的软件安装方法一致,没什么特殊强调的地方。一点安装时间很长,如果卡在某个地方20--30分钟,大家不要觉得是程序卡死,继续等下去。

使用教程

1,打开方法:

确认正确安装后,一般会在桌面建立快捷方式,点击快捷方式即可进入软件。如没有,可以 开始----所有程序 ---- Xilinx Design Tools ---- ISE Design Suite 14.7 ---- ISE Design Tools -- 64-bit Project Navigator(32bit 的也可以)

进入界面后,会默认打开你上一次的工程,如果新安装这里就空白的,无所谓啦。点击file - 新建工程。正确操作就是上面的图像。上面有一些英文注释,估计就算大家超级菜,也是可以认识的,这里不细说。

name 中写入工程名,注意工程名要简明之意,不然到最后,做的多了,你自己都不到是干什么的。location 内写入工程文件夹目录,注意不要出现非法字符和中文。外国进口的装备都有这个毛病。然后next。

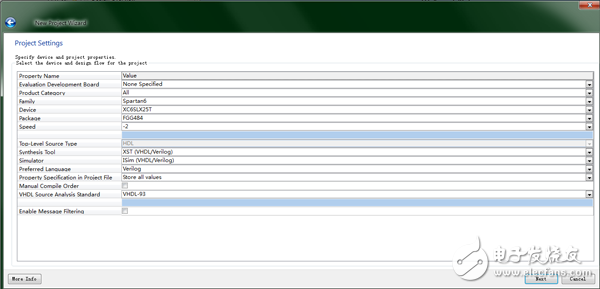

2,工程设置

先上图。

依言是各种能量文字,不会的菜鸟查字典,这是成神必备哦。如果是xilinx 官方发布的开发板,在evaluation development board中会有相关的选项 。如果找不到就说明你买的开发板是山寨的。

如果是自己的板子,就像上图一样,选择none specified,然后再family,device,package,speed中选择自己芯片的参数。有的小伙伴们会问,这个怎么选。告诉你成神必备技之查看文档手册。如果没找到,、

那就是你的问题。不要怀疑手册不全面。其他的一般不用管,next go。

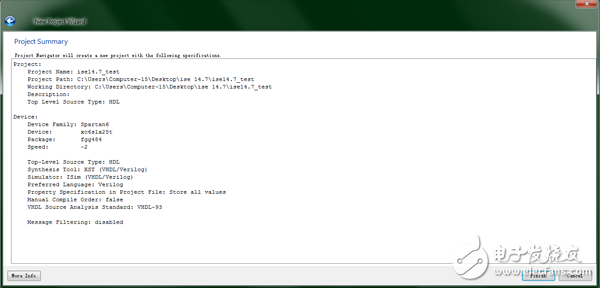

3,各种信息

这一步对初学的小伙伴,完全可以闭着眼睛点next。成神后还是可以看看的。当然对自己之前的操作有怀疑还是可以在验证一下的。

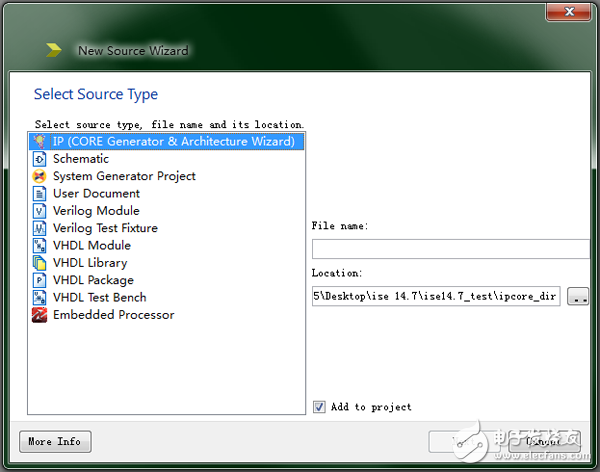

4, 选择资源类型。

这里不一一阐述。说几个注意的。IP,这个是新建ip核。verliog module,如果你要用verilog写代码,选择这个,写仿真选verilog test fixture。用vhdl就选带vhdl的类型。vhdl library是建立vhdl库的,在ip核设计中

会用到。这个对话框在ise开发过程中,可以随时右键工程名进行添加。embedded processor是edk工程,在这里建立edk工程会自动添加到ise顶层文件下。

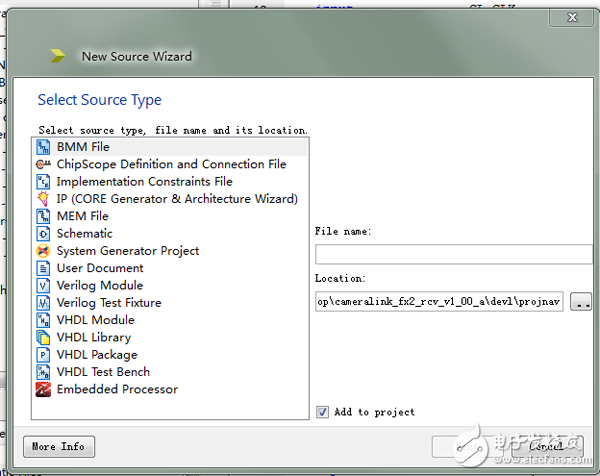

这里需要注意一点,在ise开发过程中,右键右边工程名是弹出的对话框,会多出几个选项。其中chipscope definition and connection file是加载chipscope项目。implementation constraints

file 是ucf文件(约束文件)。

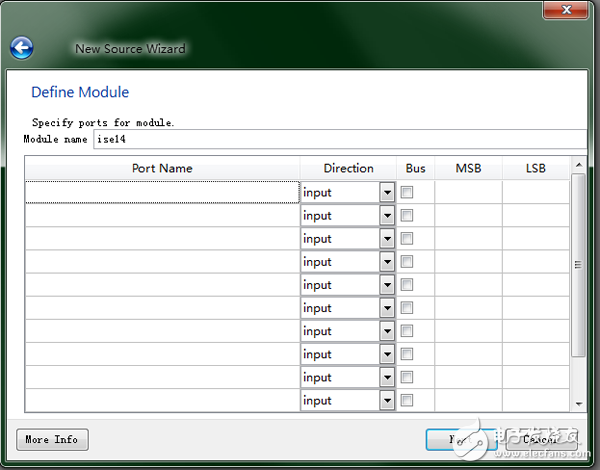

5,端口规格

这一步菜鸟们不需要设置。大神们需不需要就不知道了。到目前为止我从来没有设置过。next

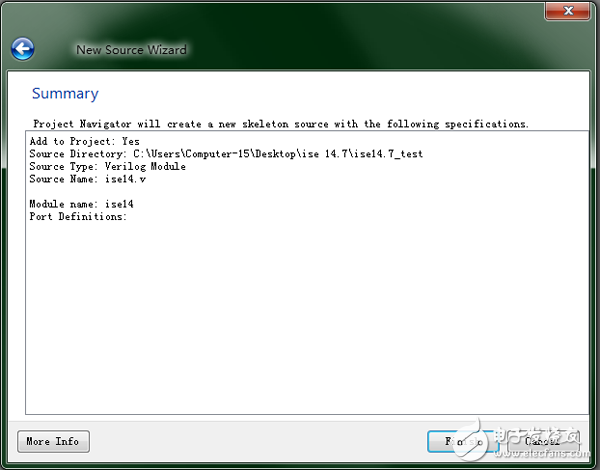

6,概括

狠狠的点击finish ,终于设置完了。

7,工程界面

现在下面的就是进入ise开发的界面了。implementation下是你建立的文件类型和结构,simulation选中后进入的是调试仿真模块。这里你右击xc6clx25t-2fgg484--新建,就会看到上一步介绍的画面。

其实你在这个模块下右击任何一个文件名都会有相同的设置。小伙伴们动手试试,不要老等着我一个一个的介绍。在processes模块下,有很多项,讲几点,synthesize(综合)在一般的代码开发中,编写玩代码

要双击一下这个选项,它是把你的代码映射成逻辑器件,在view RTL schematic 和 view technology schematic 中可以看你代码的逻辑结构图,里面会有种触发器什么的。这一步也是检测你代码是否有错误的

步骤。在此步进行代码校错。implement design中有translate(翻译),map(映射),place & route(布局布线),有兴趣的小伙伴可以上网上详细的查查,这里就是把你写的代码变成FPGA的硬件结构。

generate Programming file 这是生成运行文件。可以直接双击这一步,这样上面介绍的都会自动运行,也可以一步一步的双击运行。在FPGA开发中。这些过程完成后,生成的是。bit文件。在CPLD开发中这步

生成的是。jed文件。所以在进行CPLD开发的菜鸟们就不要苦苦的寻求。bit文件啦。configure target device 点开可以看到下载项,把写好的逻辑下载到FPGA中。analyze design using chipscop是运行

chipscop进行逻辑分析。小伙伴们可以现查有关的知识,也可以等我写有关chipscop的武器教程。

跑到图片下面来,不要跟丢哦。console 在你进行编译等过程中进展情况的显示,如果你有两个屏幕,这个最好放大放在一个屏幕上,所有的错误信息和警告全靠他了。

errors,和warnings这个就不用说了吧。如果你的代码出现错误,一定要在console窗口下反复看错误提示和警告提示。英语差的小伙伴多努力哟。后续有时间会介绍错误与解决办法的集锦。

上面图片上的代码是我随便写的,不要深究呀。

8,仿真操作。

代码写好后可以进行仿真,仿真的工具也有很多。这里简单介绍一下ise内置的。点击simulation,进到这个窗口,右键你的代码文件,ise14,新建。我去又是这个界面。选verilog test fixture。

设置个名字就行了。如果用VHDL。无比聪明的你还需要我告诉你选VHDL test 。。。吗。一般情况下,你的代码量不是很大,测试文件会自动的完整的生成。如果代码量很大,这里只会生成一个简单的框架。

不用怕同志们,对于菜鸟一时半会遇不到这个问题。

9. 武器总结。

有关代码书写,仿真代码的设计,其他工具的使用,以后会一一介绍。在此期间希望同为菜鸟的小伙伴们,多多动脑,自己思考。FPGA成神之路中,学会思考是必须必须具备的哦。

武器使用心得可以交流哦。

电子发烧友App

电子发烧友App

评论