在《数字电路之如雷贯耳的“逻辑电路”》、《数字电路之数字集成电路IC》之后,本文是数字电路入门3,将带来「时序电路」的讲解,及其核心部件触发器的工作原理。什么是时序电路?

2016-08-01 10:58:48 18171

18171

PCB层叠设计基本原则:PCB层叠方案需要考虑的因素众多,作为CAD工程师,往往关注的是尽可能多一些布线层,以达到后期

2010-04-16 17:35:37 1186

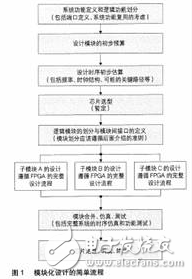

1186 1、硬件设计基本原则(1)速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个

2019-05-04 08:00:00

今天给大侠带来FPGA设计基本原则及思想,话不多说,上货。FPGA设计基本原则及思想一、硬件设计基本原则1、速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过

2020-10-11 12:26:42

1、硬件设计基本原则(1)速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个

2019-07-03 10:17:14

1、硬件设计基本原则(1)速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个

2017-12-20 08:22:28

FPGA设计总结十五条 1、硬件设计基本原则(1)速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换

2017-09-01 10:44:28

逻辑电路分为组合逻辑电路和时序逻辑电路。第四章已经学习了组合逻辑电路的分析与设计的方法,这一章我们来学习时序电路的分析与设计的方法。在学习时序逻辑电路时应注意的重点是常用时序部件的分析与设计这一

2018-08-23 10:28:59

` 本帖最后由 gk320830 于 2015-3-7 21:21 编辑

电路设计的一些基本原则以及元件的特性简介`

2013-06-05 19:48:20

AC-DC电源管理芯片选型基本原则:1、普遍性原则:所选的电源芯片要是被广泛使用验证过的,尽量少使用冷门、偏门芯片,减少开发风险。2、高性价比原则:在功能、性能、使用率都相近的情况下,尽量选择价格比

2021-11-16 08:46:40

6个MOS设计选型的基本原则

2021-03-18 07:04:16

Verilog 设计初学者例程一 时序电路设计 By 上海 无极可米 12/13/2001 ---------基础-----------1. 1/2分频器module halfclk(reset

2018-08-23 13:43:31

员在进行测量时往往会发生错误。由于IEEE 802.16标准使用的OFDM射频波形本身就非常复杂,所以他们在测量移动WiMAX信号时出错的情况更多。本文介绍了有关WiMAX信道功率测量的重要信息,这些基本原则对于三种主要的WiMAX功率测量都适用:发射功率测量、相邻信道功率测量和频谱辐射合格/不合格测试。

2019-06-03 07:50:52

主要信号、输出信号等都是在某个时钟沿驱动触发器产生的同步时序电路可以很好的避免毛刺利于器件移植利于静态时序分析(STA)、验证设计时序性能。10.同步设计中,稳定可靠的数据采样必须遵从以下两个基本原则

2009-05-26 17:31:04

1、硬件设计基本原则(1) 速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一

2017-06-19 16:11:57

1、硬件设计基本原则(1)、速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果

2019-07-17 08:00:00

什么是时序电路?时序电路核心部件触发器的工作原理

2021-03-04 06:32:49

信号完整性处理的8个基本原则

2021-01-14 07:19:08

一、变量初始化变量初始化的基本原则为:可综合代码中完成内部变量的初始化,Testbench中完成可综合代码所需的各类接口信号的初始化。初始化的方法有两种:一种是通过initial语句块初始化;另一种

2022-01-19 07:07:26

实验二 基本时序电路设计(1)实验目的:熟悉QuartusⅡ的VHDL文本设计过程,学习简单时序电路的设计、仿真和硬件测试。(2)实验内容:Ⅰ.用VHDL设计一个带异步复位的D触发器,并利用

2009-10-11 09:21:16

根据波形图设计异步时序电路 急 求大神

2017-12-08 23:07:44

★数字地和模拟地处理的基本原则如下: 1模拟地和数字地之间链接(1)模拟地和数字地间串接电感一般取值多大?一般用几uH到数十uH。 (2)用0欧电阻是最佳选择(1)可保证直流电位相等、(2)单点接地(限制噪声)、(3)对所有频率的噪声都有衰减作

2021-08-06 07:37:24

汽车电源设计要遵循哪几项基本原则?汽车通用电源的拓扑架构有哪几种?

2021-05-12 06:42:22

焊台温度设定的基本原则: 在不影响焊接质量及焊接速度的前提下,焊接设定温度越低越好。 主要考虑因素: 焊料的熔点 PCB板时间曲线图 元器件耐热温度时间曲线图 生产效率 焊盘与PCB连接的粘胶耐热

2010-08-26 19:41:17

电子电路和程序设计形成干扰的基本要素有哪几个?电子电路和程序抗干扰设计的基本原则有哪些?

2022-01-17 07:50:49

及成本等问题。这里给出一些选择基本原则,供参考。成本等问题。这里给出一些选择基本原则,供参考。1、优先考虑升压式DC/DC变换器采用升压式DC/DC变换器不仅效率高并且可减少电池数(减小整个电源体积及...

2021-11-17 08:10:49

稳压二极管稳压电路图分析稳压二极管的性能稳压二极管的主要参数选择稳压二极管的基本原则

2021-02-24 09:25:24

印制电路板基本原则是什么?

2021-04-21 06:45:37

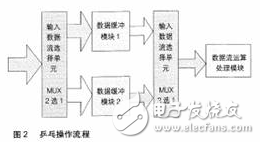

多输入时序电路的基本原理是什么?基于数据选择器和D触发器的多输入时序逻辑电路设计

2021-04-29 07:04:38

谁能说说PCB及电路抗干扰设计的基本原则有哪些呢?

2022-01-17 08:42:35

PLD练习2(时序电路)

2006-05-26 00:14:19 20

20 电器控制线路的基本原则和基本环节 第一节 电器控制线路的基本原则和基本环节 第二节 鼠笼电动机简单的起、停电器控制线路 第三节 电器控制线路的基本规

2008-11-20 17:00:45 0

0 时序电路设计实例 (Sequential-Circuit Design Examples):We noted in previous chapters that we typically deal

2009-09-26 13:01:04 37

37 FPGA设计思想与技巧:这一部分主要介绍FPGA/CPLD设计的指导性原则,如FPGA 设计的基本原则、基本设计:思想、基本操作技巧、常用模块等。FPGA/CPLD设计的基本原则、思想、技巧和常用模

2010-01-11 09:00:37 34

34 为解决TDI-CCD 作为遥感相机的图像传感器在使用中所面临的时序电路设计问题,文中较为详细地介绍了TDI-CCD 的结构和工作原理,并根据工程项目所使用的ILE2TDI-CCD 的特性,设

2010-01-12 09:54:50 21

21 摘要:分析了“数字电路与逻辑设计”课程中“一般时序电路设计”的内容的地位与作用,指出传统教学方法在设计较复杂电路时的局限性,为此完善了教材对该部分内容的讲解,

2010-05-08 08:42:54 0

0 摘要:针对同步时序电路的初始化问题,提出了一种新的实现方法。当时序电路中有未确定状态的触发器时,就不能顺利完成该电路的测试生成,因此初始化是时序电路测试生成中

2010-05-13 09:36:52 6

6 九个基本原则:1.匹配原则(光电匹配、精度匹配)见P122.阿贝比较原则3.运动学原则(按自由度确定约束数)4.统一基面原则(设计、工艺、测量基准统一)5.

2010-07-04 12:58:49 27

27 本资料介绍了大多数汽车电源架构需要遵循的六项基本原则; 列出了四种常用的电源架构,总结了最近三年汽车领域的典型设计架构。当然,用户可以通过不同方式实现具体的设计

2010-07-05 15:23:58 54

54 本文介绍将量子进化算法应用在时序电路测试生成的研究结果。结合时序电路的特点,本文将量子计算中的量子位和叠加态的概念引入传统的测试生成算法中,建立了时序电路的量

2010-08-03 15:29:01 0

0 pcb板设计的基本原则

大家都知道理做PCB板就是把设计好的原理图变成一块实实在在的PCB电路板,请别小看这一过程,有很多原理上

2008-10-28 10:01:39 2434

2434

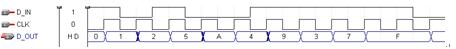

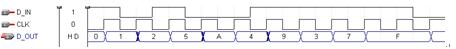

时序电路设计串入/并出移位寄存器一 实验目的1掌握VHDL语言的基本描述语句的使用方法。2掌握使用VHDL语言进行时序电路设计的方法。

2009-03-13 19:29:51 5733

5733

时序电路设计串入/并出移位寄存器一 实验目的1掌握VHDL语言的基本描述语句的使用方法。2掌握使用VHDL语言进行时序电路设计的方法。

2009-03-13 19:29:52 2024

2024

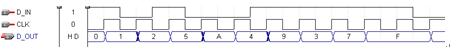

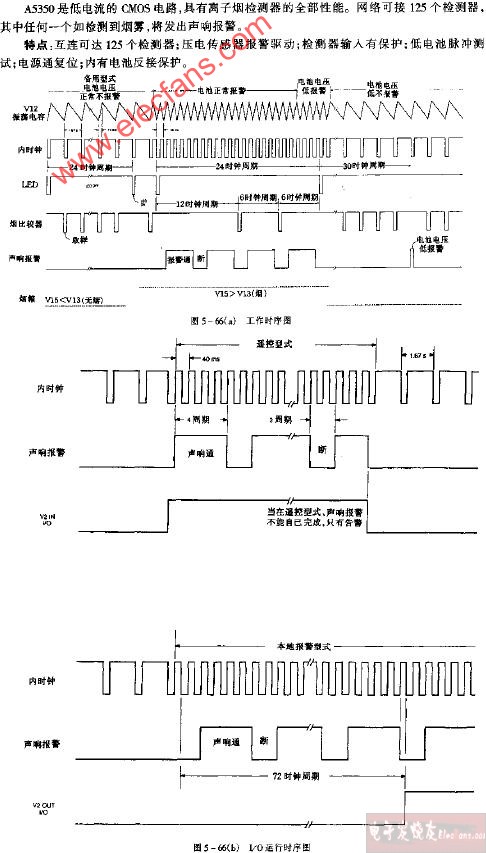

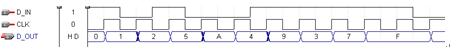

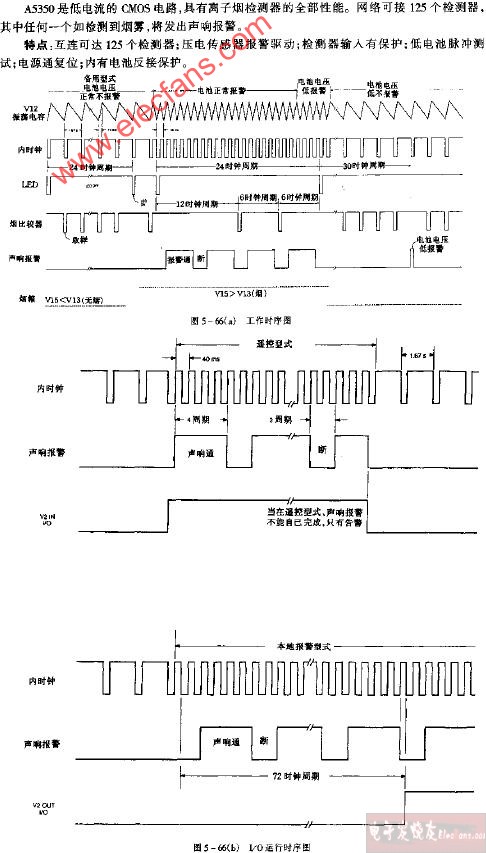

A5350工作时序电路图

2009-07-03 12:22:16 652

652

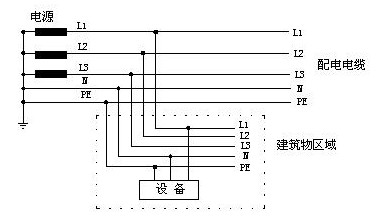

通信设备防雷接地的基本原则

4.1 通信机房建筑物 机房建筑以钢筋混凝土结构为宜。 机房建筑应有避雷

2009-09-09 21:26:15 4324

4324

传感器选用的基本原则

现代传感器在原理与结构上千差万别,如何根据具体的测量目的、测量对象以及测量 环

2009-11-07 11:39:27 2258

2258 印刷电路板设计的基本原则

1.印刷电路板的设计

从确定板的尺寸大小开始,印刷电路板的

2009-11-17 08:41:22 567

567 搭配功放和音箱的基本原则

HIFI器材的搭配非常重要。虽然其中有不少主观因素在内,但功放和音箱的搭配,则必须遵循几大原则,如

2009-12-15 10:55:35 2356

2356 HIFI声音的基本原则

对HIFI的概念,大家已经有了明确的认识。那么,什么声音可以称为HIFI的声音呢?简单来说,它就是让人听着舒服

2009-12-15 10:55:59 1006

1006 同步时序电路

4.2.1 同步时序电路的结构和代数法描述

2010-01-12 13:31:55 4672

4672

电脑维修的基本原则

一、 进行维修判断须从最简单的事情做起 简单的事情,一方面指观察,另一方面是指简捷的环境

2010-02-25 11:35:48 681

681 什么是时序电路

任意时刻的稳定输出,不仅与该时刻的输入有关,而且还

2010-01-12 13:23:14 8109

8109

为了实现时序电路状态验证和故障检测,需要事先设计一个输入测试序列。基于二叉树节点和树枝的特性,建立时序电路状态二叉树,按照电路二叉树节点(状态)与树枝(输入)的层次逻辑

2012-07-12 13:57:40 0

0 印刷电路板图设计的基本原则可以让你了解很多知识。

2015-11-02 17:25:09 0

0 内电层分割基本原则,内电层分割基本原则,内电层分割基本原则

2015-12-24 11:02:05 0

0 PCB设计基本原则,好东西,喜欢的朋友可以下载来学习。

2016-01-18 15:17:27 0

0 EMC-制作印制电路板的基本原则,有需要的下来看看。

2016-03-29 16:49:35 0

0 FPGA学习资料,有兴趣的同学可以下载看看。

2016-04-07 10:18:54 0

0 家庭装修中电气设计的基本原则,感兴趣的小伙伴们可以看看。

2016-08-22 17:06:03 0

0 基于FPGA技术的RS232接口时序电路设计方案

2017-01-26 11:36:55 29

29 在传统设计中,所有计算机运算(算法逻辑和存储进程) 都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW) 的功耗,厂商间展开了残酷的竞争

2017-10-25 15:41:59 25

25 “时钟是时序电路的控制者” 这句话太经典了,可以说是FPGA设计的圣言。FPGA的设计主要是以时序电路为主,因为组合逻辑电路再怎么复杂也变不出太多花样,理解起来也不没太多困难。但是时序电路就不

2018-07-21 10:55:37 4504

4504 组合电路和时序电路是计算机原理的基础课,组合电路描述的是单一的函数功能,函数输出只与当前的函数输入相关;时序电路则引入了时间维度,时序电路在通电的情况下,能够保持状态,电路的输出不仅与当前的输入有关,而且与前一时刻的电路状态相关,如我们个人PC中的内存和CPU中的寄存器,均为时序电路。

2018-09-25 09:50:00 24779

24779 关键词:时序电路 , 同步 同步时序电路设计 1.建立原始状态图. 建立原始状态图的方法是: 确定输入、输出和系统的状态函数(用字母表示). 根据设计要求,确定每一状态在规定条件下的状态迁移方向

2018-10-31 18:14:01 1097

1097 时序电路,是由最基本的逻辑门电路加上反馈逻辑回路(输出到输入)或器件组合而成的电路,与组合电路最本质的区别在于时序电路具有记忆功能。

2019-09-27 07:10:00 2169

2169

在介绍选择GPU服务器的基本原则之前,先来跟大家介绍下常见的GPU和GPU服务器。

2020-02-24 13:29:18 2750

2750 PLC选型的基本原则是:所选的PLC应能够满足控制系统的功能需要。

2020-04-25 10:10:45 16070

16070 PLC控制系统的设计四项基本原则如下

2020-05-18 08:57:36 3616

3616 PID控制器选型应根据控制对象特性及生产过程对控制系统的要求进行,PID控制器选型基本原则如下:

2020-06-14 11:10:48 1461

1461 PID控制器选型应根据控制对象特性及生产过程对控制系统的要求进行,PID控制器选型基本原则如下

2020-06-18 09:44:27 2056

2056 不同家庭的装修设计各有不同,家用电器的配置也不尽相同,但电气设计的基本原则是相同的。家庭装修中的电气设计基本原则如下:

2020-06-24 18:20:29 26

26 时序电路是数字电路的基本电路,也是FPGA设计中不可缺少的设计模块之一。

2020-09-08 14:21:22 6067

6067

时间的重要性不言而喻,加上时间这个维度就如同X-Y的平面加上了一个Z轴,如同打开了一个新的世界。所以今天我们就要来聊聊时序电路。 在时序电路中,电路任何时刻的稳定状态输出不仅取决于当前的输入,还与

2021-01-06 17:07:22 4371

4371 面积和速度是ASIC芯片设计中对相互制约、影响成本和性能的指标,贯穿FPGA设计的始终。在FPGA设计中,面积是指一个设计消耗的FPGA内部逻辑资源的数量,可以用消耗的触发器和查找表的个数或者是等效逻辑门数来衡量;速度是指一个设计在FPGA上稳定运行时所能达到的最高频率,由设计时序状态决定。

2021-01-20 15:49:54 12

12 片上系统(SoC)基本原则和参考书说明。

2021-03-26 14:59:57 10

10 电子发烧友网为你提供6个MOS设计选型的基本原则资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-11 08:52:21 39

39 硬件原理图设计还应该遵守一些基本原则,这些基本原则要贯彻到整个设计过程,虽然成功的参考设计中也体现了这些原则,但因为我们可能是“拼”出来的原理图,所以我们还是要随时根据这些原则来设计审查我们的原理图,

2022-06-14 10:29:00 3903

3903 组合逻辑和时序逻辑电路是数字系统设计的奠基石,其中组合电路包括多路复用器、解复用器、编码器、解码器等,而时序电路包括锁存器、触发器、计数器、寄存器等。 在本文中,小编简单介绍关于时序电路的类型和特点等相关内容。

2022-09-12 16:44:00 7234

7234

从今天开始新的一章-Circuits,包括基本逻辑电路、时序电路、组合电路等。

2022-10-10 15:39:01 875

875 工业传感器选型的六大基本原则

2023-01-06 09:17:17 675

675 那么,如何才能将过去的输入状态反映到现在的输出上呢?「时序电路」到底需要些什么呢?人类总是根据过去的经验,决定现在的行动,这时我们需要的就是—记忆。同样,「时序电路」也需要这样的功能。这种能够实现人类记忆功能的元器件就是触发器。

2023-03-24 10:48:58 818

818

同步和异步时序电路都是使用反馈来产生下一代输出的时序电路。根据这种反馈的类型,可以区分这两种电路。时序电路的输出取决于当前和过去的输入。时序电路分为同步时序电路和异步时序电路是根据它们的触发器来完成的。

2023-03-25 17:29:52 17514

17514

电子发烧友网站提供《手机故障维修基本原则及方法.ppt》资料免费下载

2023-10-24 14:22:13 1

1 电子发烧友网站提供《汽车电源设计的六个基本原则.doc》资料免费下载

2023-11-13 14:44:41 0

0 pcb布局的基本原则 PCB布局(Printed Circuit Board Layout)是电路板的设计过程,它的目的是将电子元器件和连接线路按照要求布置在电路板上,并确保电路板的正常运行

2023-12-07 17:27:35 594

594 控制静电放电的三个基本原则 控制静电放电是一项关键的工程问题,尤其是在现代工业中。静电放电不仅可能损坏电子设备和电子元件,还可能引发火灾和爆炸等安全问题。为了有效地控制静电放电,我们需要遵循三个

2024-01-03 11:00:40 390

390 群脉冲预防方案的基本原则?|深圳比创达电子

2024-01-15 14:03:37 207

207

时序电路是由触发器等时序元件组成的数字电路,用于处理时序信号,实现时序逻辑功能。根据时序元件的类型和组合方式的不同,时序电路可以分为同步时序电路和异步时序电路。本文将从这两个方面详细介绍时序电路

2024-02-06 11:22:30 291

291 时序电路是一种能够按照特定的顺序进行操作的电路。它以时钟信号为基准,根据输入信号的状态和过去的状态来确定输出信号的状态。时序电路广泛应用于计算机、通信系统、数字信号处理等领域。根据不同的分类标准

2024-02-06 11:25:21 399

399 时序电路基本原理是指电路中的输出信号与输入信号的时间相关性。简单来说,就是电路的输出信号要依赖于其输入信号的顺序和时间间隔。 时序电路由时钟信号、触发器和组合逻辑电路组成。时钟信号是时序电路的重要

2024-02-06 11:30:00 344

344

正在加载...

电子发烧友App

电子发烧友App

评论