FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。MEMS技术科普文章

得益于日益成熟的技术,MEMS传感器在各类电子产品上快速普及,我们身边的智能手机、平板电脑等几乎所有电子设备无不包含,然而大部分人对MEMS技术还是比较陌生的。...

2023-08-15 1067

设计一个计数器来讲解时序逻辑

时序逻辑是Verilog HDL 设计中另一类重要应用。从电路特征上看来,其特点为任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关。...

2023-08-14 1536

基于搭建的MMC半桥子模块电磁暂态快速模型建模

模型背景 之前那我们介绍过根据不同子模块的状态搭建的MMC子模块模型(MMC 半桥子模块电磁暂态快速模型建模)。为进一步测试所搭建模块的正确性,我们根据之前介绍的单站MMC模型(MMC最近...

2023-08-14 1906

UART串口收发的原理与Verilog设计实现

串口是串行接口(serial port)的简称,也称为串行通信接口或COM接口。串口通信是指采用串行通信协议(serial communication)在一条信号线上将数据一个比特一个比特地逐位进行传输的通信模式...

2023-08-12 3245

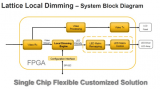

如何使用FPGA实现自适应全阵列局部调光呢?

乍一看,今天的汽车看起来跟几十年前的汽车没什么差别,但事实并非如此。车舱内、引擎盖下甚至轮胎内都隐藏这巨大的变化,可谓到处都有进步。...

2023-08-11 579

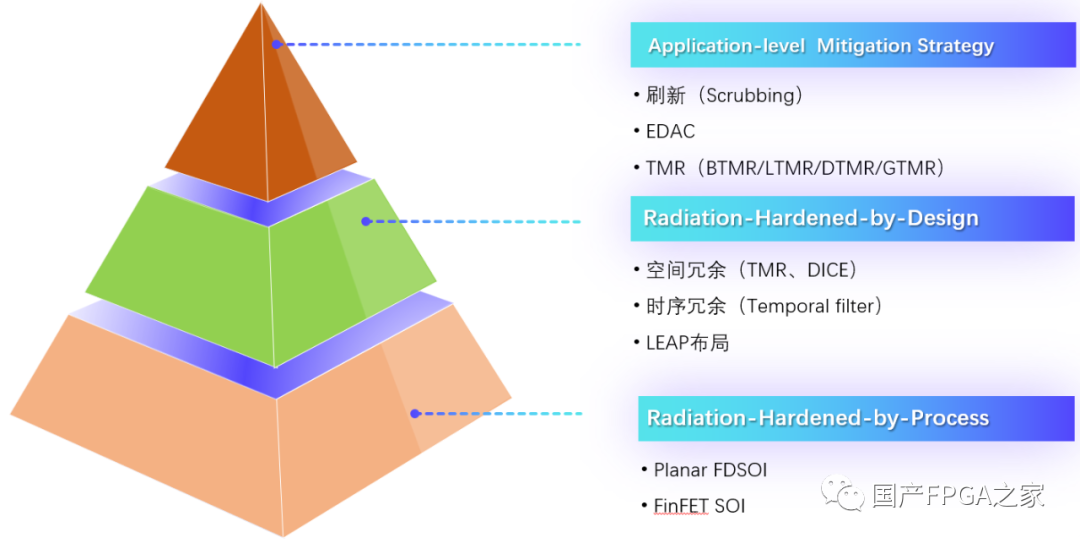

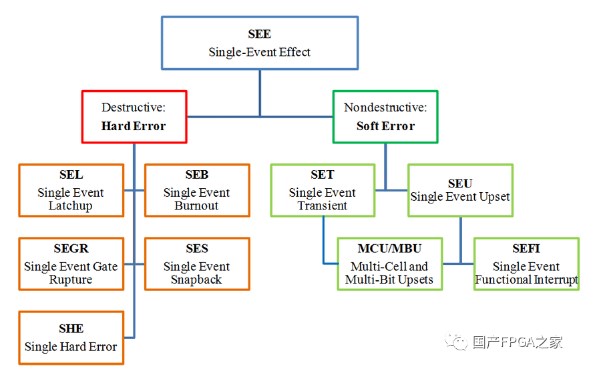

讲解一下SRAM型FPGA在轨会遇到的问题及其影响

SRAM型FPGA属于核心元器件,因此对SRAM型FPGA进行抗辐照加固设计非常必要。今天贫道主要给大家布道一下SRAM型FPGA在轨会遇到的问题及其影响。...

2023-08-11 2812

推出CXL,Intel是为了什么?聊聊数据中心另一个新技术CXL

在过去几十年中,CPU一直是计算系统中的绝对核心,甚至连存储、网络等子系统的能力都是CPU说了算。...

2023-08-11 3175

摩尔精英封测协同解决方案 力推SiP/FCBGA封装

市场对更高性能、更小尺寸、更低能耗的需求从不止步,然而,随着摩尔定律放缓和先进工艺成本攀升,仅靠制程迭代带来的性能增益有限,需要系统级的优化。...

2023-08-10 1279

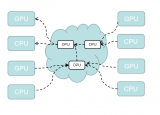

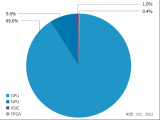

在不同应用场景下DPU不同的性能要求阐述

DPU本质上是通过DPU卡上资源,解耦计算、控制、存储,利用CPU、GPU、FPGA加速器等异构处理单元,通过以智能卡为接口的网络实现高效的数据分发和调度。市面上流行的DPU产品基本上都实现了3类...

2023-08-09 2894

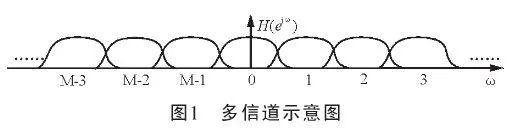

数字收发组件的关键技术 RF-FPGA芯片在窄带系统设计中的优势

对于通信、雷达等无线电行业相关的朋友,我相信大家对于窄带系统的设计,必然是轻车熟路,如数家珍。尤其是围绕FPGA+AD/DA的数字收发的架构设计,那估计更是心中有笔,信手拈来了。 传统...

2023-08-09 2930

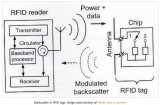

什么是被动后向散射?“无电池”物联网即将到来!

当谈到物联网设计时,最重要的一个方面是电池寿命。较长的电池寿命意味着更长的正常运行时间、更少的维护需求,以及物联网设备更大的可持续性。...

2023-08-09 893

如何提升跑Calibre效率呢?

Siemens的Calibre是业内权威的版图验证软件,被各大Foundry厂广泛认可。用户可以直接在Virtuoso界面集成Calibre接口,调用版图验证结果数据,使用起来极为方便。...

2023-08-09 1913

求一种超低成本FPGA JTAG方案

首先按照GitHub 说明在虚拟机上安装依赖项,然后创建一个新的存储库目录并克隆了 pico-SDK 和 XVC-Pico 项目。...

2023-08-09 562

Vivado的Implementation阶段约束报警告?

前言:本文章为FPGA问答系列,我们会定期整理FPGA交流群(包括其他FPGA博主的群)里面 有价值 的问题,并汇总成文章,如果问题多的话就每周整理一期,如果问题少就每两周整理一期,一方面...

2023-08-08 1487

FPGA零基础学习之TLC5620驱动教程

在FPGA处理完数字信号之后,我们有些情况下是需要将数字信号转变为模拟信号再输出的。比如音频信号在滤波后,需要转换为声音信号进行输出。...

2023-08-04 1081

薄膜PMUT研究进展综述

据麦姆斯咨询报道,近日,新加坡国立大学(National University of Singapore)和新加坡科技研究局(A*STAR)微电子研究所的研究人员组成的团队在Microsystems & Nanoengineering期刊上发表了题为“Thin-...

2023-08-03 1974

时钟偏移对时序收敛有什么影响呢?

FPGA设计中的绝大部分电路为同步时序电路,其基本模型为“寄存器+组合逻辑+寄存器”。同步意味着时序路径上的所有寄存器在时钟信号的驱动下步调一致地运作。...

2023-08-03 1633

Vivado仿真器和代码覆盖率简析

编写 HDL 通常是 FPGA 开发中耗时最少的部分,最具挑战性和最耗时的部分可能是验证。根据最终应用程序,验证可能非常简单,也可能非常复杂,简单的话只需对大多数功能进行检查或执行完全...

2023-08-03 2355

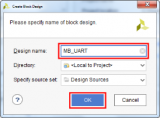

MicroBlaze串口设计

本系统中,Basys3的MicroBlaze模块调用基于AXI协议的UART IP核,通过AXI总线实现MicroBlaze-UART之间的通信,完成串口打印。...

2023-08-02 1833

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS | harmonyos |

发布文章

发布文章